A Quarterly Publication of The Microelectronics Packaging & Test Engineering Council

Volume 24, Number 3

### STRUCTURALLY FUNCTIONALIZED MATERIALS

Optimized for In-Situ Cleaning During Advanced Wafer Level Test

page 19

Known Good Die Virtual Workshop 2020 KGD Powering More than Moore! page 15

Development vs. Production, a Paradigm Shift in Thinking page 16

Interview - Catching Up with Ivor Barber From National to Fairchild to LSI to Xilinx to AMD in 39 short years page 24

#### **INSIDE THIS ISSUE**

UP FRONT It's amazing how busy semiconductor companies and their supply chains have been recently.

CALL TO ACTION The need for solder columns in commercial applications will grow more than 25x over the next 10 years.

MEMBER NEWS from Intel, Samsung, ASE, Henkel, FormFactor, Indium, Integra, ON Semiconductor, Fralock and more.

#### ANALYSIS

Adding monitors or traceability into an SoC is not new, but it is beginning to become a huge new opportunity.

# Enabling the Future

As the original pioneers of the OSAT industry, Amkor has helped define and advance the technology, manufacturing and test landscape.

We deliver innovative packaging solutions with the service and capacity global customers rely on.

The MEPTEC Report is a Publication of the Microelectronics Packaging & Test Engineering Council

141 Hewitt Street, Summerville, SC 29486 Tel: (650) 714-1570 Email: bcooper@meptec.org

Publisher MEPCOM LLC Editor Bette Cooper Art Director/Designer Gary Brown Sales Manager Gina Edwards

#### MEPTEC Executive Director

Ira Feldman MEPTEC Advisory Board

#### **Board Members**

Dave Armstrong Advantest Ivor Barber AMD Jack Belani Indium Corporation Calvin Cheung ASE (US) Inc. Jeff Demmin Keysight Technologies Douglass Dixon 360 BC Group Jaspreet Gandhi Xilinx Nick Leonardi SMART Microsystems Herb Reiter eda 2 asic Consulting

Emeritus Advisors

Seth Alavi Sunsil Joel Camarda Anna Gualtieri Elle Technology Ron Jones N-Able Group International Phil Marcoux PPM Associates Mary Olsson

#### Contributors

Brian Bailey Semiconductor Engineering Ivor Barber Advanced Micro Devices (AMD) William Boyce SMART Microsystems Ltd. Jerry Broz, Ph.D. International Test Solutions Ira Feldman Feldman Engineering Corp. Martin Hart TopLine Corporation

MEPTEC Report Vol. 24, No. 3. Published quarterly by MEPCOM LLC, 141 Hewitt Street, Summerville, SC 29486. Copyright 2020 by MEPCOM LLC. All rights reserved. Materials may not be reproduced in whole or in part without written permission. MEPTEC Report is sent without charge to members of MEPTEC. For nonmembers, yearly subscriptions are available for \$75 in the United States, \$80US in Canada and Mexico, and \$95US elsewhere. For advertising rates and information contact Gina Edwards at 408-858-5493.

### UP FRONT

### **Zooming Ahead**

Ira Feldman Executive Director, MEPTEC

WELCOME! From long time MEPTEC members to recent subscribers to casual visitors, we are glad you are here.

I continue to be optimistic. It is simply not in my or anyone else's ability to predict when things will settle on the "new normal". When I last wrote this letter, I was thinking it would be another two months for us in Silicon Valley. Unfortunately, we passed that milestone about a month ago...

My continued optimism is based upon our ability to adapt. It is amazing how busy semiconductor companies and their supply chains have been recently. Many companies are shipping record volumes even with the uncertainty and challenges of the pandemic. And friends and colleagues report being as busy as ever. But the good news is they are not too busy for the **excellent content that MEPTEC is providing.**

Not only are the **Semiconductor Industry Speaker Series** luncheons we jointly host with IMAPS as a **biweekly webinar** going well, we had a **great panel discussion** about the need for **Known Good Die**. "Who cares about Known Good Die? Heterogenous Integration is where the action is!" had over two hundred thirty attendees live on the webinar with many more watching on YouTube. If you missed the panel discussion or one of the speaker series presentations, check out the recordings at **youtube.com/MEPTECpresents** and please subscribe to our channel today.

In terms of adapting, we have changed the **Known Good Die Workshop to a virtual event** on the mornings of **September 16-18.** Through the generosity of our sponsors, registration will be free of charge. Please see the excellent program on page 15 with full details at www.kgdworkshop.org and register today.

The MEPTEC Advisory Board is also working on another virtual event for either early December or the first quarter of 2021. As soon as the details are ready, we will let everyone know. There are certainly some exciting topics being considered which further increases my optimism about our ongoing programming.

I look forward to hearing your suggestions and feedback as to how MEPTEC can best serve you. Please don't be shy!

Stay safe and healthy!

Ira Feldman Executive Director, MEPTEC ira@meptec.org +1 650-472-1192

### CALL TO ACTION

## Does the FPGA Industry Face Peril? Pt. V

Martin Hart TopLine Corporation

PART IV OF THE SUMMER 2020 MEPTEC REPORT titled "Call to Action" addressed the need to strengthen the gaps in the diminishing supply base that collectively threatens America's leadership position as a producer of Field Programmable Gate Array (FPGA) devices for the aerospace and defense industries.

### Defense Grade FPGA Require Solder Columns

Heritage hardware used in the aerospace and defense (A&D) industry are built on a platform of Field Programmable Gate Array (FPGA) devices with solder columns instead of solder balls. Column Grid Array (CGA) FPGA packages engaged in mission critical black box systems are more reliable than Ball Grid Array (BGA) packages. FPGA BGA packages with solder balls prematurely fail due to huge stresses caused by differentials inherent in material mismatches between the FPGA package and Printed Circuit boards (PCB). In a nutshell, ceramic BGA devices experience an unacceptable level of failures; whereas, column CGA devices endure significantly longer.

### Risk of Continuation of Supply of Solder Columns

Today, Original Device Makers (ODM) of ceramic FPGA devices rely on just one subcontractor (Six Sigma, Milpitas California) to attach copper wrapped solder columns for the entire aerospace and defense industry. To understand the risk of relying on a monopoly supplier, one needs only to ponder a simple question: Can the aerospace and defense industry be assured of a consistent supply of solder column attachment services 10, 20 or 30 years from now? A sudden shortage of mission critical FPGA devices could cause market distortions that are

Lead Free Solder Column. U.S. Patent Pending

not in the defense industry's best interest, resulting in warfighters not flying and rockets not launching. To strengthen the resiliency of supply, VPT Components and Micross Components (recently acquired by Corfin Industries, financially backed by equity investor, Behrman Capital) are at various stages of attaining Oualified Manufacturers List (OML) approval to offer copper wrap column attachment services on FPGA devices. Other microelectronics subcontractors are also showing interest in offering column attachment services. That said, as of the date of this publication major ODM device makers, who control over 80% of all FPGA devices for aerospace and defense, have not taken steps to qualify a second source as a contingency back up. The principal reason cited for such inaction is the lack of a budget to qualify alternative subcontractors to attach copper wrap columns.

#### **Emerging Technologies Need Columns**

New markets for massive A.I. computing, silicon antennas and super-sized devices for 5G towers and satellites under development require solder columns to reduce stress caused by Coefficient of Thermal Expansion (CTE) mismatch in materials. The need for solder columns in such commercial applications will grow more than 25x over the next 10 years. These burgeoning applications require tens of thousands of solder column terminals per device. Ramping demand will quickly swamp the capacity of today's subcontractors to attach solder columns. A risk exists in the current supply chain for column attachment services should the need for columns in the defense market suddenly surge.

#### Pending RoHS Requirements for Lead Free Columns

Historically, the aerospace and defense industry has largely been exempt from meeting the requirements of the European Union (EU) Restrictions of Hazardous Substances (RoHS) directive which regulate the use of lead (Pb) in solder columns. It is widely speculated that one day in the future, RoHS will stop renewing its exemption which currently allows high Pb content solder balls and solder columns. This event could trigger unintentional consequences by forcing ODMs to convert to fully leadfree FPGA products. This could force individual end-users to independently seek lead (Pb) bearing column attachment services. Such a cascade of events could most likely exceed the production capacity of the current monopoly column attachment subcontractor. To meet future needs for lead-free columns, TopLine has applied for patents on Pb-free solder columns.

#### Conclusion

By the end of 2021, it is anticipated that more than five subcontractors in the USA will be proficient at providing column attachment services to the aerospace and defense industry. Presumably, the Defense Logistics Agency (DLA) current travel ban will be lifted after the Corona Virus dissipates, allowing the DLA to resume on-site auditing to certify additional QML suppliers of column attachment services. Establishing strength in this critical area will enhance readiness, provide greater security of supply, and cause fewer program delays by the potential inability to deliver FPGA components in a timely manner.  $\blacklozenge$

### Intel Collaborates with Argonne National Laboratory, DOE in Q-NEXT Quantum Computing Research

INTEL HAS ANNOUNCED that it is among the leading U.S. quantum technology companies included in Q-NEXT, one of five new national quantum research centers established by the White House Office of Science and Technology Policy (OSTP) and the U.S. Department of Energy (DOE). Q-NEXT, National Quantum Information Science Research Center, is led by Argonne National Laboratory and brings together world-class researchers from national laboratories, universities and leading technology companies to ensure U.S. scientific and economic leadership in this advancing field. The collaboration will enable Intel to actively contribute to the industry's efforts on quantum computing.

"Advancing quantum practicality will be a team sport across the ecosystem, and our partnership with Argonne National Laboratory on Q-NEXT will enable us to bring our unique areas of expertise to this cross-industry effort to drive meaningful progress in the field. At Intel, we are taking a broad view of quantum research that spans hardware and software with a singular focus on getting quantum out of labs and into the real world, where it can solve real problems."said James Clarke, director of Quantum Hardware at Intel.

Quantum computing has the potential to tackle problems beyond the capabilities of conventional systems today by leveraging a phenomenon of quantum physics that exponentially expands computational power. This could dramatically speed complex problem-solving in a variety of fields such as pharmaceuti-

Photo of the inside of a quantum computing refrigerator in Intel's Quantum Computing Lab in Hillsboro, Oregon. Credit: Walden Kirsch/Intel Corporation

cals, telecommunications and materials science, accelerating what today could take years to complete in only a matter of minutes.

To speed the discovery and development in this promising emerging field of computing, the DOE and the OSTP have created five new quantum information science research centers across the country, with Q-NEXT being one of them.

The Q-NEXT facility will create two national foundries for quantum materials and devices, and leverage the strength of private-public partnership to focus on the advancements of three core quantum technologies:

• Quantum networks: Development of communications networks and interconnects for the transmission of quantum information across long distances, including quantum repeaters that enable the establishment of "unhackable" networks for information transfer.

• Quantum-enabled sensing: Development of sensor technologies that can leverage the exponential power of quantum computing to achieve unprecedented sensitivities for data capture, which would have transformational applications in physics, materials and life sciences.

• Quantum test beds: Ongoing research utilizing quantum test environments, including both quantum simulators and future full-stack universal quantum computers, with applications in quantum simulations, cryptanalysis and logistics optimization.

Q-NEXT will additionally seek to train a nextgeneration, quantum-ready workforce to ensure continued U.S. scientific and economic leadership in the rapidly advancing field of quantum information sciences.

Intel's research efforts in quantum span the entire quantum system - or "fullstack" - from qubit devices to the hardware and software required to control these devices, to quantum algorithms that will harness the power of quantum technologies. All of these elements are essential to advancing quantum practicality, the point at which quantum computing moves out of research labs and into real-world practical applications.

Visit intel.com for more.

#### MEMBER **NEWS**

#### KEITH JACKSON, ON SEMICONDUCTOR PRESIDENT AND CEO, ANNOUNCES PLANS TO RETIRE

ON SEMICONDUCTOR has announced that Keith D. Jackson, the Company's President and Chief Executive Officer, intends to retire from ON Semiconductor in May 2021. To ensure an orderly transition. Mr. Jackson will continue to remain in his current roles until his retirement and will assist the Board of Directors in its search for his successor. In addition, Mr. Jackson will also retire as a member of the Board of Directors in connection with his retirement as President and Chief Executive Officer and does not currently anticipate standing for reelection at the Company's 2021 Annual Meeting of Stockholders. www.onsemi.com

#### ► AEHR RECEIVES INITIAL ORDER FROM NEW CUSTOMER FOR FOX-NP<sup>™</sup> SOLUTION AEHR TEST SYSTEMS

announced that it has received orders from a new customer and their subcontract manufacturing supplier for a FOX<sup>™</sup> solution including a FOX-NP<sup>™</sup> full wafer test system, an initial WaferPak<sup>™</sup> Contactor, and a FOX WaferPak Aligner to perform production qualification. This new customer will begin utilizing Aehr's FOX-NP system for initial production burn-in and stabilization of their high performance silicon photonic devices and is then expected to transition to Aehr's FOX-XP wafer-level test and burn-in systems to meet their volume production forecast. www.aehr.com

#### INTEGRA RANKS ON THE 2020 INC. 5000 WITH THREE-YEAR REVENUE GROWTH OF 115 PERCENT

INC. MAGAZINE has revealed that Integra Technologies ranks on its annual Inc. 5000 list, the most prestigious ranking of the nation's fastest-growing private companies. The list represents a unique look at the most successful companies within the American economy's most dynamic segment-its independent small businesses. Intuit, Zappos, Under Armour, Microsoft, Patagonia, and many other well-known names gained their first national exposure as honorees on the Inc. 5000. www.integra-tech.com

#### CAREER TECHNOL-OGIES USA ACQUIRED BY FRALOCK

FRALOCK, a leading engineering and manufacturing provider of specialty material solutions for technically challenging and mission critical applications, has announced that it has completed the acquisition of Career Technologies USA. Career Technologies, with three facilities in the greater Los Angeles area, is a leading provider of engineering and manufacturing solutions. The company focuses on integrating various materials and components for demanding applications and technologies, including flexible and rigidflex circuits and related assemblies, for the medical device, aerospace, and other specialty markets. Both Fralock and Career Technologies focus on thermal and electrical management technologies. www.fralock.com 🔶

### Indium Corporation Introduces New Ball-Attach Flux

INDIUM CORPORATION has released a new ball-attach flux, WS-829, designed for printing and pin transfer applications for the smallest sphere and high-density applications, including LED die-attach.

WS-829 is a water-soluble, halogen-free flux that can be used for ball-attach on substrate in a standard ball-grid array (BGA) manufacturing process (especially for the smallest sphere applications < 0.25mm) as well as wafer-/ panel-level packaging (WLP/ PLP).

Indium Corporation offers a robust portfolio of flux products designed for new or

emerging industry challenges. To learn more about Indium Corporation's fluxes, visit www.indium.com/ball-attach. Indium Corporation is

a premier materials refiner, smelter, manufacturer, and supplier to the global electronics, semiconductor, thin-film, and thermal management markets. Products include solders and fluxes; brazes; thermal interface materials; sputtering targets; indium, gallium, germanium, and tin metals and inorganic compounds; and NanoFoil®. Founded in 1934, the company has global technical support and factories located in China, India, Malaysia, Singapore, South Korea, the United Kingdom, and the USA.

For more information about Indium Corporation, visit www.indium.com.

### Henkel Offers High-reliability Alloy for ADAS Assembly

THE GROWTH OF ADVANCED DRIVER

Assistance Systems (ADAS) to support autonomous driving is unprecedented and so are the requirements for computing performance. Highly integrated ADAS domain controllers with centralized engine control units (ECUs) are the brain of the system receiving data from cameras, lidar, ultrasonic sensors and radars for perception and fast safety-critical decision making. The reliability of the electronics hardware is critical to long term functionality, making Henkel's 90iSC high reliability alloy essential to solder joint stability for safety critical components.

As with other automotive electronic components, the design of ADAS control units is challenged by weight and footprint – miniaturization of components becomes increasingly important. Nonlead packages (without leads or pins sticking out of the side of the package) contribute to optimizing the component footprint on a printed circuit board (PCB). In some cases, it can be optimized from 40 to 80% by changing from standard packages to non-lead packages, when multiplied by the number of components on the control unit the real-state becomes significant.

Automotive solder joints should be designed to be as reliable as possible, because they play a central role in keeping the driver, passengers and pedestrians safe. Each solder joint must provide reliable electrical conductivity and mechanical fixation. Some designers raise concerns about the reliability of the solder joints as non-lead packages expand under thermal stress and shear strain forces may originate micro cracks at the interconnection. In many cases, conventional tin-silver-copper (also known as SAC) lead-free solder paste materials are not able to meet the requirements of applications in ADAS and other critical automotive components. That is why Henkel joined together with partners to create the innovative 90iSC alloy. The creep resistance and tensile strength of the 90iSC alloy surpasses targets of SAC and SnPb (tin-lead) alloys at all measured strain rates and temperatures, maintaining a stable grain structure and ensuring assemblies are more robust preventing electrical failures. With its durability and adaptability, 90iSC has become the leading high-reliability, lead-free and RoHS-compliant solder alloy. Henkel offers a complete range of Loctite solder paste solutions capable of exceeding the challenges of harsh environments for safety-critical electronic applications, and compliant with the automotive engineering test MS184-01 for high stress components.

For more about Henkel's 90iSC alloy visit www.henkel-adhesives.com/electronics. •

### Samsung VP to Keynote IWLPC

THE INTERNATIONAL Wafer-Level Packaging Conference and Expo announces Dan Oh, Ph.D., Engineering VP of the Test & System Package (TSP) unit at Samsung Electronics will deliver the opening keynote presentation of the virtual event. The presentation, "Trends, Challenges, Opportunities in Advanced Packaging for Smart Computing Era" will be released on Tuesday, October 13, 2020 at 9:00am US Pacific Time.

Dr. Oh is responsible for developing signal and power integrity and thermal solutions for memory, S. LSI and foundry devices. From 2016 to the end of 2019, Dr. Oh led the Package Development department responsible for both research and development of the entire Samsung product line. During this time, he helped establish an advanced wafer-level packaging laboratory for developing high-end server products such as 2.5D Silicon/RDL interposers, FO-WLP and 3D TSV devices. He also helped research and grow FO-PLP technology for consumer and mobile products commercializing the world's first FO-PLP product for the Galaxy watch.

Dr. Oh received his Ph.D. in electrical engineering from the University of Illinois, Urbana-Champaign in 1995. He has over 30 years of experience in the packaging and signal and power integrity fields with multiple high-tech companies, including Intel, Rambus, and Synopsis.

The keynote presentation is open to all registered attendees. The technical conference and expo are available on-demand from October 13-30 with a live, online exposition enabled October 13 and 14.

For questions about the IWLPC conference, please contact Jaclyn Sarandrea, jac-lyn@smta.org. ◆

#### ASE Technology Holding Joins Apple's Supplier Clean Energy Program

ASE TECHNOLOGY HOLDING CO., LTD. HAS ANNOUNCED that it has joined the Apple Supplier Clean Energy Program. As a leading semiconductor packaging, test and system service provider, ASE is focused on cutting edge manufacturing technologies including System-in-Package (SiP), Heterogeneous Integration (HI), 3D IC, MEMS and sensor, and systems integration that form the backbone of many electronic devices. Semiconductor manufacturing is an energy intensive industry, and ASE is taking bold steps to improve its energy efficiency and steadily shift to greener production.

ASE is supportive of industry efforts to advance the use of clean energy within the supply chain and is pleased to join the Apple Supplier Clean Energy Program which is focused on transitioning suppliers to clean, renewable energy. By participating in the program, ASE can augment its current approaches to clean energy by tapping into the leadership and resources established by Apple.  $\blacklozenge$

**Remove contamination** and collect debris from critical contactors.

Innovative turn-key products that **ensure high yields** and lower cost of test.

**AFTER CLEANING**

# Improving yield, reducing cost.

www.inttest.net

### OPTICALLY CLEAR EPOXY for Bonding & Coating

#### **TWO PART EP37-3FLF**

Very high flexibility Elongation 50-100%

Cryogenically serviceable down to 4K

Low viscosity 600-1,100 cps

Excels in e-textile packaging

www.masterbond.com

🖀 (408)516-4611 🛛 info@namics-usa.com

### New SmartMatrix<sup>™</sup> 3000XP Probe Card Lowers DRAM Test Costs by More than 25%

Provides 300 mm Wafer Testing for up to 3000 Die Simultaneously

#### FORMFACTOR, INC., A LEADING

semiconductor test and measurement supplier, has announced the release of the SmartMatrix 3000XP probe card, reaching another high-throughput milestone in DRAM wafer test. The new SmartMatrix 3000XP probe card allows DRAM manufacturers to test 3000 die or more in a single touchdown leveraging FormFactor's proprietary Tester Resource Enhancement (ATRE) and MEMS probe technologies. The new breakthrough allows the simultaneous test of approximately 1000 additional die over previous capabilities and can reduce the test cost per die by more than 25%.

The DRAM industry's migration to the 1Z and 1 $\alpha$  nanometer process node from the previous 1X and 1Y nodes continues the trend to increased die count on wafer. As a result, full-wafer DRAM probe cards that simultaneously test every die on the wafer must keep pace. Built on FormFactor's proven and scalable DRAM probecard architecture, the SmartMatrix 3000XP incorporates new custom electronics to enhance signal integrity while leveraging massive tester resource sharing to enable highly parallel test at the 1Z and 1 $\alpha$  nanometer nodes. According to market research firm IC Insights, the 1Z DRAM node will move to high volume production late this year.

"The technology built into our advanced DRAM probe cards provides customers a way to keep test costs in check, increase throughput of a test cell, and ramp to high volume production quickly," said Matt Losey, Senior VP and GM of the Probes Business Unit at Form-Factor. "The SmartMatrix probe card, with its scalable MEMS probe technology, helps accelerate our customers' yield and performance knowledge while meeting their aggressive die shrink roadmap."

The SmartMatrix 3000XP probe card's key features include:

- Proprietary TTRE (Terminated Tester Resource Enhancement) technology, enabling parallel test of 3000 die for low test cost

- Ultra-high switch-density ATRE (Advanced Tester Resource Enhancement) components allowing efficient component placement on existing 520mm PCB tester platforms

- Industry-leading test temperature range, from -40C to 125C, with a single probe card design for optimal operational efficiency

- Proven low-force 3D MEMS probe technology, enabling more than 150,000 probes per card at 1Z and 1α tech nodes pitch requirements. The platform supports the next generation 3D MEMS probe technology for ultrasmall DRAM die

- Test clock rates up to 200 MHz at wafer sort, significantly increasing throughput and test coverage without compromise on test times

For more information, visit the Form-Factor website at www.formfactor.com. •

### COLUMN

### COUPLING & CROSSTALK

By Ira Feldman

Electronic coupling is the transfer of energy from one circuit or medium to another. Sometimes it is intentional and sometimes not (crosstalk). I hope that this column, by mixing technology and general observations, is thought-provoking and "couples" with your thinking. Most of the time I will stick to technology but occasional crosstalk diversions may deliver a message closer to home.

### Replacing the Road

HELLO, FELLOW ROAD WARRIORS! Do you feel lost? Unappreciated? Unable to deliver your message or solve customer problems? I too am struggling with the current pandemic situation. And I suspect many of you are too - especially the dyed in the wool corporate marketing, sales, and business development road warriors. Truth be told, I had seven international business trips on the schedule for 2020. New suitcases bought in January remain untouched. As an optimist, I did not return them since they *will* get used... And this working from home bit? I've been working from home for almost fifteen years. What I am not used to is not leaving or more specifically not heading out to a customer site or conference somewhere. Can I really deliver results totally "hands-off" via virtual means? Will the absence of in-person meetings hamper business or future progress?

How well are we doing virtualizing in person business interactions? Business meetings are easy, right? We all just hop onto the company's web conferencing platform with our web cameras & screen sharing and go! Far easier, more efficient, and definitely more socially distanced than gathering in the stuffy conference room. Not so fast there... Yes, the basics of "meeting" are covered. And yes the need for travel anywhere is eliminated. Or are they?

Like most tools, **web conferencing works well for specific types of meetings** within a specific range of constraints. One has to be careful that everything starts looking like a nail if all you have is a hammer. Beyond the technical issues like bandwidth, forced software downloads, and security there are a wide range of human factors and social issues to be considered. Issues from "what is the purpose of the meeting" to "Zoom fatigue" <sup>[1]</sup>. It is clearly a different dynamic if it is an established work team doing weekly status updates versus a vendor meeting a potential customer for the first time. The current tools are better for established relationships.

When things settle as the "new normal" there will likely be an overwhelming demand for in-person events like conferences.

So, we really need to understand what happens as part of a business gathering beyond the information exchanged. First, humans are social creatures. When things settle as the "new normal" there will likely be an overwhelming demand for in-person events like conferences. Those in sales and marketing would argue that there is nothing as productive as a face-to-face meeting and research like Professor Bohn's<sup>[2]</sup> has shown that in-person appeals are 34 times more successful than email.

At conferences and tradeshows, which are far more complex than a routine team meeting, the value to the attendees typically far exceeds the information that is presented on the "main screen". And this value needs to be taken into consideration when shifting conferences from in-person to online. For some, the actual presentations are irrelevant beyond motivating attendance and gathering people who are interested in the topics being presented. Many professionals I know highly value the networking opportunities and random conversations through which they make connections and learn important details. And just like the lack of office "water cooler conversations" in each day's fully scheduled set of web meetings, most virtual conferences do not deliver these impromptu and informal conversations.

As I've worked on the planning for MEPTEC, TestConX, and other events I see a worrisome trend of conference organizers and online platform providers who are trying to replicate a physical event. These attempts at direct virtualization work as well as a Rolex watch knock-off. They are flashy and from a distance look great. But once you look closer at the details there are lots of problems. Who really wants to spend 8+ hours per day in front of their computer for three days in-a-row to attend a virtual event? And the ambiance of a cavernous windowless exhibit hall with poor acoustics and thin carpet? So, why bring the bad and the ugly into the online world?

Event organizers must take the opportunity to innovate and try new approaches to improve their online versions. Yes, many years of best practices have informed us what works in terms of in-person events. However, these practices may not translate well into the virtual world. It is time to step back and look at the event goals and rethink every aspect as an online version is built. For example, online education has permitted a greater shift to the "Flipped Classroom" model<sup>[3]</sup>. Research has proven that when students are exposed to content prior to meeting with the instructor, they focus on higher levels of cognitive work during class time thereby increasing learning. And which is easier to follow and watch, a closeup of a well-known university lecturer presenting in a high-quality video recording or the same person appearing as a small dot

[1] "How to Combat Zoom Fatigue", Liz Fosslien and Mollie West Duffy, Harvard Business Review, April 29, 2020. https://hbr.org/2020/04/how-to-combat-zoom-fatigue

[2] "A Face-to-Face Request Is 34 Times More Successful Than an Email", Vanessa K. Bohns, Harvard Business Review, April 11, 2017. https://hbr.org/2017/04/a-face-to-face-request-is-34-times-more-successful-than-an-email

[3] "Flipping the Classroom", Cynthia J. Brame, Center for Teaching, Vanderbilt University. https://cft.vanderbilt.edu/guides-sub-pages/flipping-the-classroom/

# SPECTRUM IS YOUR HI-REL IC PACKAGE AND LID SOLUTION

FOR MIL-AERO, AUTOMOTIVE, COMMUNICATIONS, MEDICAL, WIRELESS AND AVIONICS APPLICATIONS

Spectrum offers:

- Highly knowledgeable sales staff with decades of Industry Experience

- Highest quality ROHS, REACH, Non-Conflict Minerals and Counterfeit Prevention compliant materials

- ISO-9001:2015 and AS9120B QMS Certified

- Qualified Source for: Mil-Aero, Automotive, Communications, Medical, Wireless, Avionics

- World Wide Same Day Shipping

- Guaranteed On-Time Delivery

- Small Business, Veteran Owned

- Competitive pricing

Located in Silicon Valley for the past 30 years, Spectrum Semiconductor Materials, Inc. is a World Wide Authorized Distributor of packages and lids for IC assembly. Our proven track record, consistent customer service and long-standing supplier relationships makes us the premier distributor for your IC Packaging needs.

Visit www.spectrum-semi.com to see what we can do for you!

155 Nicholson Ln. San Jose, CA 95134 (408) 435-5555 Email: ssm\_sales@spectrum-semi.com

### COLUMN

at the bottom of a 500-person auditorium?

Online versions of events should also follow best practices for the mediums they are using. Why build a lousy user interface (UI) for a website while trying to emulate an inperson event? Websites should be designed for usability and user engagement and need not look like a physical event. A popular conference platform has virtual booths with a counter and fictitious booth occupants. Behind the booths fake views of city skylines are included. When was the last time you saw floor to ceiling windows in an exhibit hall with high elevation city views? In this particular case, this design choice is not only confusing, it squanders precious computer screen real estate and is not mobile device friendly.

As virtual events are (re)designed, attention should be paid to analytics for organizers, sponsors, and exhibitors. Sponsors and exhibitors should identify what their goals are and collect data to appropriately measure results. Is your goal brand awareness (raw number of impressions) or sales lead of a certain quality or something else? Sometimes you will need to enlist the organizer's support to collect meaningful data. With today's platforms more aspects can be measured with greater specificity than at a physical event. There is no reason to have generic metrics such as lumping attendance from multiple adjacent shows all together. If these aspects are discussed up front, it is more likely the organizers can work through the details to support the collection of the desired data. And like any on-going process, having data to drive decisions about future events is critical.

As you are planning and packing your (virtual) suitcase for your next business meeting, spend the time to give some thoughts as to the business goals you are trying to achieve; which tools and mediums are the most appropriate; and how to measure the results. Winners will use the time to innovate in the virtual space while others spend their time attempting to replicate their existing and sometimes mediocre in-person experiences.

For more of my thoughts, please see my blog http://hight-echbizdev.com.

As always, I look forward to hearing your comments directly. Please contact me to discuss your thoughts or if I can be of any assistance.  $\blacklozenge$

IRA FELDMAN is the Principal Consultant of Feldman Engineering Corp. which guides high technology products and services from concept to high volume manufacturing. He engages on a wide range of projects including technical marketing, product-generation processes, supply-chain management, and business development. In addition to serving as MEPTEC's Executive Director he is the General Chair of TestConX. He lives in Silicon Valley (San Francisco Bay Area) and previously was more likely found in an airport than his office. (ira@feldmanengineering.com)

### **Monitoring Chips After Manufacturing**

Adding monitors or traceability into an SoC is not new, but it is beginning to become a huge new opportunity across the entire silicon lifecycle.

Brian Bailey, Technology Editor/EDA Semiconductor Engineering

Reprinted with permission from Semiconductor Engineering, August 19th, 2020. Online version with hyperlinks: https://semiengineering.com/post-siliconcomprehension/

#### NEW REGULATIONS AND VARI-

ability of advanced process nodes are forcing chip designers to insert additional capabilities in silicon to help with comprehension, debug, analytics, safety, security, and design optimization.

The impact of this will be farreaching as the industry discusses what capabilities can be shared between these divergent tasks, the amount of silicon area to dedicate to it, and the value they may be able to extract from it. New business models may emerge to deal with data ownership.

Is this the next frontier for silicon? "Yes," says Steve Pateras, senior director for test marketing at Synopsys. "We spent many years trying to optimize designs, tape them out, and then forget about them. We have come to the realization this is no longer possible. You need a methodology, a platform, and an approach that provides a way of monitoring and managing electronics throughout their operational life."

There are multiple drivers for doing this. "The challenge of ensuring everything is functioning as expected throughout a chip's lifetime has become more difficult," says Aileen Ryan, senior director for Tessent portfolio strategy at Mentor, a Siemens Business. "Structural monitoring is required to detect defects, degradations and aging effects. Additionally, there may be functional issues caused by bugs and even malicious attacks which must be detected and mitigated. For chips that are deployed in situations where safety, security and resilience are a priority, it is critical that detection of these issues takes the minimum amount of time."

Technology pressures certainly are making it necessary. "As process technology advances, designers can no longer insert large margins to obtain yield, and ensuring that chips behave within specification is becoming a lot more difficult across different workloads," says Norman Chang, chief technologist at Ansys.

### New Business Models May Emerge to Deal with Data Ownership. Is this the Next Frontier for Silicon?

"In addition, with large AI chips and other large SoCs, the workload cannot be accurately predicted."

Reliability issues are growing. "With technology transitions, such as finFETs, a lot of new types of defects got introduced in these devices during the manufacturing phase," says Faisal Goriawalla, senior staff product marketing manager for Synopsys. "Some of these will manifest quickly, during production. Some of these will manifest later in the SoC lifecycle. The process rules are getting increasingly complicated. The memory bitcell transistor is very sensitive to the process. It is 2X more sensitive than the logic transistor used to synthesize the rest of the chip."

Aging is becoming a big concern,

too. "Things are getting less reliable, and the reliability requirements are going up," says Synopsys' Pateras. "It is not just reliability. It's security, safety, it's even performance, it's power."

This is not just for the benefit of the chip manufacturers. "A big application is preventive maintenance," says Ansys' Chang. "Consider unexpected system shutdowns, which can cost a lot of money. If you can catch that before the system breaks down and replace a particular chip or particular PC board, that can save a lot of money. Intentional shutdowns of the system can be done safely, whereas unexpected shutdowns can cause damage. Preventive maintenance can save a lot of money."

In other industries it is likely to become mandatory. "A new regulation from the United Nations Economic and Social Council, WP.29/GRVA (The Working Party on Automated/Autonomous and Connected Vehicles) is due to go live in January 2021," says Mentor's Ryan. "This work relates closely to ISO 21434 and ISO 26262 standards which also address cybersecurity and safety in vehicles - and how these ultimately impact vehicle design and passenger safety. What this means to vehicle OEMs is that they will be automatically and ultimately responsible for the cybersecurity of a vehicle, not only at the point of sale or throughout its warranty period, but throughout its entire lifecycle."

#### The Basics

Synopsys' Pateras provides us with a primer on the subject. "It's all about managing silicon throughout the lifecycle. The approach has two components to it. First, we need visibility into the chip. We need to know what's going on and so

### ANALYSIS

we embed various forms of instrumentation – monitors, sensors. Think of PVT sensors, think of structural monitors like looking at the margins, looking at the path delays, looking at clocking abnormalities, and even more macro monitoring. If you think of security, you need to be looking at activity on buses. What is being read and written to memories? What's being accessed? And so, the first component of this approach is to get visibility into the chip for various components."

That's step one. "Once you have all these monitors and sensors in the chip, and you've placed them properly in an efficient way, you need to make use of that information. So the second part of this approach is analytics - taking this data at different points in time. We may want to take it during manufacturing. We may want to take it during production test. We may want to take it while we're trying to bring up the system. And I certainly want to be taking it throughout the operational life of the system. And we want to perform analytics to figure out what's going on and then react to it. Analytics can be on-chip, they can be off-chip but locally within a system, sort of edge analytics, or they can be centralized, where we send data to some central repository where we're doing some sort of big data analytics."

#### **Owning the Data**

One of the big questions that comes from this is who owns the data. "The whole question of data analytics involves how to run analytics, who runs it, and who can access it," says Frank Schirrmeister, senior group director, solutions marketing at Cadence. "When I look at some of my personal devices, there are machines which sync data locally to an app, but they do not interface to others. That is because of the value of the data, because you really want to control who can access the data because if they have access to the data, they could build the same thing again. It will be an interesting challenge for the whole notion of data platforms."

That could affect business models within the industry. "A lot of designers are putting in dynamic frequency voltage scaling," says Chang. "Based on the reading from the thermal sensors they can slow down the frequency or lower the Vdd of operation in order not to exceed the thermal hotspot threshold. That's the current way of doing things, but with the post silicon on-chip sensors, we can think about a new working scenario where we bring together the multiphysics simulation vendor, combined with a chip vendor and the customers using those chip in the system. Can postsilicon monitoring provide information that becomes beneficial to all the parties? It is a new problem to think about in terms of the business model."

And it may not be an easy problem to solve. "If you're a vertically integrated company, it's no issue," says Pateras. "You can use the data throughout the stack. If not, there needs to be a way of sharing the results of the analytics. If you're a chip provider who put the sensors and monitors into the chips, and that data is being extracted from the chips, you need to be able to at least allow the results of some basic analytics to be provided to the system vendor. That data could be post processed analytics rather than raw data coming off the chip. This is why there's value in doing analytics at different stages. If there's a lot of raw data coming at you, you may want to be able to filter out what's really important and then you can do system level analytics."

#### Securing the Data

Allowing this type of data off-chip could be a security vulnerability. "Security is needed for silicon, regardless," says Pateras. "You want security for antihacking, for IP theft and so forth. Security is a critical aspect of chips going forward. So there needs to be techniques used to ensure the security of this data and you can think of using encryption keys to provide access to the chip and that same mechanism would be used for accessing this monitor data. There's no way to access the monitored data unless the proper access is provided. And then access can be controlled by the chip provider, and by the system provider as needed."

The data could enhance security. "Could you use this data for side-channel attacks?" asks Chang. "Possibly. Usually you put a thermal sensor in sensitive locations, or a thermal hotspot. If the thermal hotspot location is coincident with the security sensitive location, and with a different payload in an AES security chip, you may create different thermal reading from different payloads, and that information may enable an attacker to crack the key. That's why the information coming out should be secured. But it also works the other way. If the attacker is exercising a specific workload, or the sequence of the payload, in order to extract the key, the on-chip thermal sensors or other sensors can have a machine learning agent to try to detect the pattern of the specific workload."

Functional monitoring is becoming an important issue. "State-of-the-art solutions for functional issues in the field deploy embedded monitors on the chip, which constantly watch for anomalous or unexpected behavior," says Ryan. "These monitors are instantiated in hardware and operate at clock speed, constantly collecting data about how the chip is operating. This data can then be correlated and analyzed to identify the root cause of a functional problem."

Or a vulnerability. "In some forms of attack, it may create a spike in voltage, or it may create a temperature increase that is abnormal," says Pateras. "Being able to monitor voltage and temperature on an ongoing basis, and then be able to understand the history of those parameters, allows you to discover or detect changes in the behavior of those parameters that are abnormal. Another example is monitoring bus activity. Again you could look at what is a normal amount of transaction data or the type of transaction data that is normal for that system. If you start seeing changes or anomalies, you can then determine that something's going on and quickly turn off access to those components. It requires both the monitors to be able to see what's going on, and it also requires the data history and requires the ongoing analysis of that data."

And finally, security needs to be updated regularly throughout the lifetime of a product and best practices need to be maintained. "Nothing is secure unless you practice secure principles," said John Hallman, product manager for trust and security at OneSpin Solutions. "Usually, an insider is the weakest link. So after you've done all the due diligence, this

### ANALYSIS

needs to be part of the normal behavior."

That also includes regular monitoring for data leakage, Hallman said. "You may have several organizations that know a piece of the design, but nobody really knows all the pieces. If you look at complex designs, very few people ever know the larger scheme for a chip. Those controls need to be kept pretty tight, and you need good checks and balances."

#### Accessing the Data

There are design decisions that have to be made about how to get data offchip. Is it intrusive, utilizing existing communications channels which may also affect operation or performance, or does it have dedicated resources to be able to obtain and transmit the data in an unobtrusive manner? How do you balance the on-chip computation and storage requirements against bandwidth?

"We see the same thing during the development process when running in the hardware engines," says Cadence's Schirrmeister. "We often refer to them as accelerated verification IPs, which are optimized to collect data. The challenge is very similar to large-scale edge processing. There is a network from your sensor to the data center. Where do you do the compute? You can push out everything, which is very intrusive and will impact speed, versus computing things internally. Then you don't have all the data available anymore. You only have the computed derived data. But then you have a much better chance to collect that and stream it out."

Test standards are paving the way in being able to collect data within complex packages. "IEEE 1838 is a new testability standard which was developed for 2.5D and 3D-IC testing," says Synopsys' Goriawalla. "It enables you to think about inter-die test and intra-die test management. You have a situation where you no longer have the accessibility to all of the middle die that are stacked in a 3D structure, and so you need to have a framework, and infrastructure which is able to test through the bottom die to test the other dies that are stacked on top of it. In addition, there is also die to die connectivity, or the interconnect which needs to be tested."

Some systems may use existing interfaces. "There may be the need for some standardization of monitor data," says Pateras. "Then we can use standard bus accesses, going through standard functional high-speed interfaces to access that data. If any chip or chiplet or die has a PCI Express, or USB interface, we will piggyback on that to gain access to the monitor data. We have IP inside the chip that provides access to the monitor data on-chip and sends it through these existing functional interfaces. That means we do not add additional infrastructure to gain access to the monitor data."

Part of the decision may be based on the speed with which you need to detect and react. "For safety-critical use-cases, this kind of on-chip embedded analytics system will give the fastest possible detection and response times," says Ryan. "In other use-cases, where time

<section-header>

Stocked in USA www.TanakaWire.com

FALL 2020 MEPTEC REPORT | 13

### ANALYSIS

is not so critical, the data collected by on-chip monitors can be loaded into an off-chip analytics system, where it can potentially be correlated with an even richer set of data to determine root cause and next steps."

#### Understanding the Data

Many years ago, GE started to collect huge amounts of data from their aircraft engines. At the time, they did not know how they would use all that data, but today they do. "Part of the problem at the beginning is you often don't know what to measure," says Schirrmeister. "That's why you want to have the option to push out all the data but then the dire consequence of this is that, just by virtue of interface bandwidth, you will have to slow things down to do that. The tendency is to measure everything and store everything and that's only possible for a certain amount of time."

Machine learning can be helpful. "We are applying machine learning to these analytics," says Pateras. "Some are algorithmic, but we're also looking to apply standardized neural net-based approaches to looking at trends. This is an ongoing, evolving space where we're going to continually try to improve our understanding of what's going on in those chips and be able to better predict what's going to happen."

Some of the data may need to be tied back to more extensive models. "Post silicon monitors are a very good idea that provides you with a better reading for real-time chip operation, but also create a problem," says Chang. "The problem is that it's not model-based. It is purely based on the reading from the on-chip sensors. And so they only provide a one dimensional view. But the workload is changing, the threshold is changing. You need a model-based digital twin to complement the on-chip sensor reading. Consider a sensor that can tell you resistance is getting larger, but if you don't have a physics-based model, you cannot predict how much time before it will fail. You need a reliability model to complement on-chip monitoring sensors."

#### How Much Overhead?

Defining the area or performance penalty for the insertion of this type of monitoring is difficult. Not only will

systems have different amounts of monitoring, but much of that circuitry may already exist for other functionality. "There are early indications that customers are willing to give up a small amount of area," says Pateras. "Area is always important but if this becomes part of the functional requirements of the chip, then it becomes more accepted and less of an afterthought. These monitors are useful for many things. They are useful for bring up, they useful for performance improvements. PVT sensors are used for doing things like dynamic voltage and frequency scaling. This is a functional requirement. You can't make this chip work without it. So these monitors and sensors have already been placed into chips, at least in these lower nodes, just to make a chip work. Taking a little more area is not that much of a stretch in most cases."

Sometimes it may be coupled to safety requirements. "There is likely to be a mechanism or infrastructure in the chip which is performing some kind of testing," says Goriawalla. "This is not just the traditional manufacturing test, but it could be in-system. It could be in the form of power-on self test, it could be a periodic test during mission mode functional operation. This safety infrastructure has to be in the chip so that when it finds an error that it cannot recover from. that cannot be corrected, it needs to have a mechanism to aggregate the errors and report them to a functional safety manager for then reporting to a higher level system software or to the user."

#### Tying it Back to the Development Flow

There is a lot to be gained from this data in the development flow. "Chip design is based on simulations and on basic models, but there's very little real data being used to optimize this design," says Pateras. "We're now looking at using these analytics. Think about path delays and margin analysis, and using it to better understand the distribution of margins and frequencies and then driving that back to the design implementation tools, to our models, to calibrate those models based on the actual silicon data. That will allow us to tighten our margins and tighten the timing on our designs and make them more optimized. The link from silicon analytics back to design is

something we're very excited about."

Better understanding leads to better products. "If we can do real-time monitoring for the lifetime of the product, you will really see the aging phenomenon," says Chang. "That will provide valuable feedback to the design stage, enabling better chips for the next generation. We can see thermal cycling running under a realistic scenario over different workloads. As a simulation vendor, how do we provide the multi-physics model, or a reduced-order modeling? That can help to do a good correlation with real-time sensor data to provide valuable information for the whole ecosystem."

And with systems houses becoming responsible for the product over the lifetime, there may be constant updates. "With security becoming a critical aspect of IC development, post-silicon analysis is going to change," says Sergio Marchese, technical marketing manager for OneSpin. "ISO 21434, the automotive cybersecurity standard, has specific demands on how OEMs and their supply chain handle incident response, for example. Assessing the impact of newly discovered hardware and software vulnerabilities on systems, and identifying and verifying solutions, will become almost a routine task. The very nature of security verification, where unintended use case scenarios take center stage, means that static analysis techniques will have a significant role in implementing systematic, efficient incident response processes."

#### Conclusion

The introduction of on-chip monitoring was initially required for a number of small use cases, but as technology has progressed and the value of analytics understood, the ways in which this data could be used are becoming endless. The entire chain from EDA vendors, to chip developers, to systems companies, to the end users who deploy those systems all see value in the data that could be provided. Many of those capabilities are becoming necessary to fulfill end product requirements, or to deal with safety and security demands. There are many issues that need to get resolved, such as who owns the data, or who can gain access to it, and long term, that may lead to some interesting new business models.  $\blacklozenge$

### **MEPTEC PRESENTS**

# **KNOWN GOOD DIE VIRTUAL WORKSHOP 2020**

### KGD Powering More than Moore!

### September 16-18, 2020

ith the demise of Moore's Law due to the economics of advanced semiconductor process nodes, the demand for greater cost performance and differentiation has fueled the development of advanced packaging. Having Known Good Die (KGD) is essential for many, if not all, of the current 'crop' of advanced semiconductor packaging.

Join us at the 20th Annual Known Good Die Workshop on September 16-18, 2020 for a cross-functional view of challenges and solutions for achieving KGD!

| JOIN US FOR THREE ONLINE SES | SIONS |

|------------------------------|-------|

|                              |       |

| Wednesday | September 16, 2020 | 8:00 - 10:00 am PDT |

|-----------|--------------------|---------------------|

| Thursday  | September 17, 2020 | 8:00 - 10:00 am PDT |

| Friday    | September 18, 2020 | 8:00 - 10:30 am PDT |

Friday September 18, 2020

THE SOLUTIONS

#### Wednesday September 16, 2020

MEPTEC

#### 8:00 am

**Opening Remarks**

THE NEED

End to End Data Yuri Mitnick Cisco

Zoe Conrov Cisco

8.00 am

Shift Left David Armstrong Advantest

Bernice Zee

Thursday September 17, 2020

THE STRATEGY

Analysis Challenges

Advanced Packaging Failure

Known Not Bad Die Success: Repair, Redundancy, and Pragmatism Bob Patti NHanced Semiconductors, Inc.

10:00 am Adjourn

After 30 Years Why Are We Still Talking about Known Good Die? Jan Vardaman Techsearch International

Improving SiP Quality and **Reducing Cost Using Machine** Learning and Predictive Analytics Jeff David **PDF** Solutions

**Die Sorting & Inspection** Gerald Steinwasser Muhlbauer

**Die Crack Prevention and Detection in Advanced Packaging** Woo Young Han Onto Innovation

10:00 am Adjourn

10:30 am Adjourn

#### Event Registration is Free Courtesy of Our Sponsors

**Emerald Sponsors**

Sapphire Sponsor

FOR MORE INFORMATION AND TO REGISTER ONLINE TODAY GO TO KGDWORKSHOP.ORG

### **SMART** MICROSYSTEMS<sup>™</sup>

### Development vs. Production, a Paradigm Shift in Thinking

William Boyce SMART Microsystems Ltd.

FOR MOST NEW PRODUCT DEVELopment organizations, development and production should go hand in hand. Products should move seamlessly from concept to prototype, to production representative, and finally to production. At least that is the goal. The challenge is in making sure that the transition is seamless, and that is often the biggest hurdle. During the product development cycle, the focus is primarily on ensuring the product meets or exceeds the minimum customer design requirements and that the design is also manufacturable. At some point, the product needs to be released for production, and this is the transition point at which we sometimes stumble as an organization if we are not properly prepared.

In previous articles, we discussed the concept of concurrent engineering, but we did not discuss the actual product development transitions within that process. The concept of concurrent engineering assumes that the teams are working together to ensure that the transition points are managed effectively, but certain factors can aggravate that transition. For example, when the process development engineer is in the development phase, minor changes are both normal and expected. New drawing revisions, lifecycle changes, and changes in incoming material quality are all par for the course. Process development engineers become accustomed to accepting things like the incoming material variation and learn how to work around it. Rework loops become a way of life in process and product development. Let's face it, without rework loops in development, most products would never make into production. But, when we shift from the development phase into pre-production or production, we need to have these

issues resolved the best we can.

For most product development teams there are specific phases that we identify with. For us at SMART, we have come to view a "concept" phase as that stage in the process at the very beginning, where we attempt to determine whether or not the idea or concept is viable. Is the fundamental concept sound, does it work, and can it be built? The development phase begins at concept, and continues through production representative, with test and inspection data collected along the way. The prototype portion is the point in the development cycle where we determine if we can actually produce working prototype sample parts that will function in the environment and application for which the product was intended. This is the point at which the process engineering team gets more heavily involved and begins to refine the proposed production process. Production representative phase should include production representative tools, processes, and components. These production representative sample parts should in every way represent a finished product with the exception that they are not produced on production qualified tools. Production parts are production qualified and meet or exceed the customer engineered drawing requirements in every way. These last two phases are where we see most of the transition paradigm misalignment issues.

It is at that point of transition between development and production release where the thinking needs to change. This is particularly an issue because we want to keep the same individual engineers from concept through release, and these development engineers are no longer in a development program, they are now in production. So there needs to be a paradigm shift in how we think about the process going forward. Since the product is no longer in development, processes must be adapted and refined to reflect production needs. One example of a refinement point is tolerance of variation in incoming material – we need to be far less tolerant of incoming material issues and those issues need to be documented, categorized, and flagged to the teams. The teams need to increasingly refine the documented processes, and be more observant of change, which can be achieved using statistical process control (SPC) and other methods. This is how we ensure that every product leaving the production process meets or exceeds the customer requirements. This is the big challenge that teams face as they move the process into production. There are however some actions that can be taken to minimize or eliminate this risk of this common stumbling point.

Many times we are asked, "When is it a good time to start planning for product launch?" If you have read some of my previous articles, you will recall that we like to *begin with the end in mind*. That means that planning for product launch should start on day one of the product concept. There are a lot of things we can do to properly prepare, far too many to list here, so I will mention just a few critical but simple things we can do to increase our prospect of success and reduce the chance of launch issues.

First of all, the development team should be documenting all of the issues that have been noticed along the way. This includes any incoming material issues, process issues, process data, etc. This valuable, irreplaceable information and data should effectively and completely find its way into all of the manufacturing process documentation. At SMART we use work order travel-

# **Reliability and Environmental Life** Testing, Test & Inspection and Failure Analysis Services I NIISTER

- Providing solutions for Product Engineers who have manufacturing and quality challenges

- Comprehensive Test, Inspection, and Failure Analysis services located in one facility

- Reduction of overall cost and continuous product improvement

SMART Microsystems' Super Ultraviolet (SUV) Accelerated Test Chamber is one of only three in the U.S. providing access to a unique and valuable capability.

# THINK SMART.

#### MICROELECTRONIC ASSEMBLY RELIABILITY AND ENVIRONMENTAL LIFE TESTING **TEST & INSPECTION AND FAILURE ANALYSIS**

**SMART Microsystems** works with Product Engineers who need solutions to their manufacturing and quality challenges. Providing both comprehensive Reliability and Environmental Life Testing as well as Inspection and Failure Analysis Services in one location, along with expertise in custom microelectronic assembly, allows SMART Microsystems to help customers reduce overall cost for continuous product improvement.

Call us today at 440-366-4203 or visit our website for more information about our capabilities and services.

**Innovative Microelectronic Solutions.**

141 Innovation Drive, Elvria, Ohio 44035 Telephone: 440.366.4203 info@smartmicrosystems.com ISO**9001:2015**

SMART Microsystems is Powered by

LAND ESOEC THE MENTING HELLER HESSE HITACHI Kulche & Softa HODDOLITT @anotronics (Nordson

#### WWW.SMARTMICROSYSTEMS.COM

### **SMART** MICROSYSTEMS<sup>™</sup>

ers for every job that contain all of the discrete steps in the process. Each discrete process step has a discrete process step number that translates to a discrete work instruction card (WIC), and all of the WICs have individual visual aids attached. These documents are all revision controlled and they all have been developed during the product development cycle to include "lessons learned" from both process and material considerations. Secondly, in addition to extensive data aggregations, all root cause analysis and failure mode analysis results should be stored and referenced in a single location and be reflected in the process

Dispense process development for production representative samples.

documentation. Any source of incoming or outgoing unacceptable material conditions, for example, should be in the library of visual aids for production. And thirdly, let's not forget failure analysis. After all, we know it will happen. At SMART we use a tool called the "FA Process Checklist". We capture all of the lessons learned along the way from all of the failures that we investigated and root caused, including going back into early development data, to develop a process of how we will deal with a return, if and when it comes in from the customer. We actually take the time to develop and document a procedure checklist that will

have the greatest likelihood of finding the root cause of the failure, in the shortest time, with the least amount of damage to the evidence. I plan to write a future article on the genesis and application of this very useful tool, but for now I leave you with this final thought: With planning, documentation, and communication a seamless transition from the development cycle into the production is attainable.

Author Bill Boyce is the Engineering Manager at SMART Microsystems. Bill can be reached at Bill@smartmicrosystems.com. ◆

smartmicrosystems.com

MICROSYSTEMS

### PACKAGING

### "Structurally-Functionalized-Materials" Optimized for In-Situ Cleaning During Advanced Wafer Level Test

Jerry Broz, Ph.D., SVP Technology Development International Test Solutions

TECHNOLOGICAL DEMANDS FOR 5G connectivity, Internet of Things (IoT), artificial intelligence (AI), wearables, and automobiles (self-driving, electrified, etc.) are key drivers for semiconductor device functionality and performance. Moving to the next technology nodes is extremely difficult and there are very high costs associated with the fab investment for the process development. In today's commercial landscape, only a few IDM (integrated device manufacturers) and foundries, such as Intel, Samsung, and TSMC, are actively pursuing monolithic silicon wafer scaling to keep pace with the age-old Moore's Law. To cost-effectively meet consumer needs, much of industry is pursuing advanced packaging and assembly solutions, such as 2.5D, 3D, and heterogeneous integration. Using these complex strategies, it is possible to attain economic advantages

and reach the high-end performance that the consumer demands. The advanced packaging market is expected to account for more than 50% of the total packaging market by 2024<sup>[1]</sup>.

Advanced package solutions combine the benefits of multiple processors, sensors, RF, and memory modules, etc., obtained from different suppliers and technology nodes into compact unified system chips or modules. The impact of a single failure within these multi-component systems creates a new level of requirements for data quality, test complexity, coverage, and cost. In the years ahead, wafer-level-test and package-level-test will gain importance for thoroughly validating the IP as "known good" or "good enough". Known Good Die (KGD) is important for packaging houses which want devices fully tested with required functionality and "want [the devices] to be as close to 100% as possible"<sup>[2]</sup>. As a result, the IDMs, foundries,

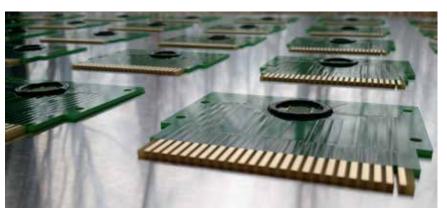

Figure 1. Probe card cleaning materials sized for installation onto cleaning units, polishing plates, and wafers typically used for on-line probe card cleaning within all makes and models of wafer probers.

and off-shore assembly and test (OSAT) suppliers must rely even more heavily on wafer-level, device-level, and packagelevel testing. Ideally, each device would be subjected to a Known Good Die (KGD) test to independently validate its performance; however, in many cases that might not be economically feasible. The highest levels of data integrity at all levels of test are critical for determining the chip functionality without an added cost of test that outweighs the value for when the system is completed.

#### A "Dirty" Challenge

In all instances, wafer-level-test requires physical contact between the contactors of a probe card and the device to assure appropriate electrical connection for valid test performance execution. Many of today's advanced MEMS and vertical probe cards are designed with the lowest possible per-pin forces, often substantially less than 2-grams per probe, and have highly refined tip geometries that minimize scrub damage to ensure stable electrical contact for attaining optimal test yields. Due to the small sizes of these probe tips that might challenge prober optics, some probes are designed with critical reflective surfaces and fiducials that facilitate probe-to-pad-alignment. Ultra-low force requirements are necessary to support zero-defect manufacturing, known-good-die determination, and large area array testing of memory devices, even after multiple insertions at the same pad location<sup>[3]</sup>. The higher the force that a contactor applies to a device, the greater the chance for creating defects or damage to the underlying structures and circuits. As an example, large array memory probe cards can have up to 150K probes which will apply as

### PACKAGING

much as 300 to 400 kilograms of force over a 300mm probing area within the prober.

It is well-known that efficient probecard cleaning and debris collection play an important role to ensure data integrity, maintain stable yields, and tool uptime for cost-effective test execution. As such, probe card cleaning materials have been configured to match the shapes and sizes used within all the various wafer-prober makes and models (Figure 1).

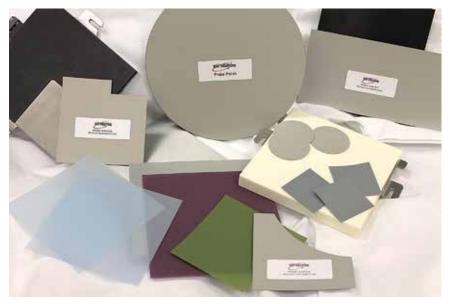

Historically, probe cleaning materials have limited to flat rigid abrasive films (Figure 2), semi-rigid abrasively coated open-celled foams (Figure 3), and abrasive filled compliant polymers (Figure 4). Although these three classes of materials have been generally effective, the cleaning efficiencies for removing contamination and collecting debris from critical surfaces are not sufficient for the ultra-low force, advanced MEMS probe technologies. As the low-force contactor technologies increase in complexity, many of the "traditional" in-situ cleaning materials simply do not have the surface properties to meet performance requirements. To keep pace with the demands for cleaning the next generation of probe-cards, International Test Solutions has innovated a new class of materials that combine key performance attributes from these "simple" cleaning materials with engineered, micron-scale regular structures to attain highly functionalized performance.

#### Approach

Functionalized microstructures can provide improvements and benefits that are not possible with simple non-featured surfaces. Some examples of such performance enhancements for smart materials include (1) "gecko inspired adhesives" that are glue-free, self-cleaning, and multi-reusable as well as insensitive to surface conditions<sup>[4, 5]</sup>; and (2) surfaces built using functionalized "shark-skin" denticles to boost swimming efficiencies by more than 7% and reduce expended energy by 6% over a comparable smooth surfaces<sup>[6,7]</sup>. By functionalizing a probe cleaning material surface, it will be possible to attain consistent, low-force probe cleaning combined with tip shape maintenance and effective sub-micron particle removal.

Figure 2. Flat, rigid abrasive film with a high surface roughness for contact area texturing and surface contamination removal.

Figure 3. Abrasively coated, open-cell poromeric foam for tip shaping and adherent material removal.

Figure 4. Highly cross-linked and abrasively loaded elastomeric polymers with a complaint and flat tacky surface for contact area polishing and accumulated debris collection.

International Test Solutions fabrication process involves compliant polymers for probe card cleaning with different levels of abrasive particle loading; however, attaining functionalized surface geometries required new process development and alternative materials best suited for the process. Numerous surface geometries and configurations were investigated and comprehensively tested at the ITS Center for Cleaning Materials Expertise (CCME) using small scale, reduced pin-count test vehicles representative of full-scale fine pitch and advanced probe-cards.

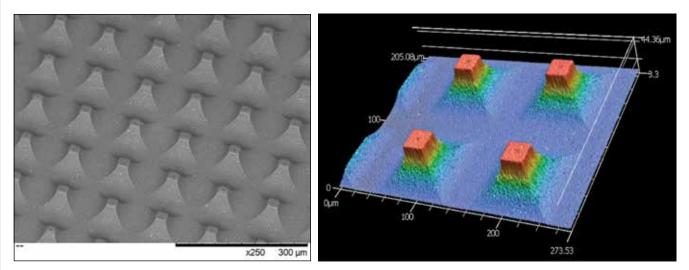

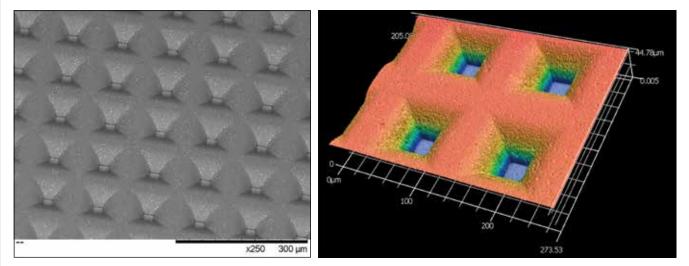

One of the biggest challenges when using ultra low force probes is that any adherent debris and non-uniform cleaning will dramatically affect the data integrity. During the assessment of various flat and foam-based materials, nonuniform material deflection during overtravel resulted in uneven cleaning performance across fine-pitch probe arrays. Peripheral probes often receive uneven cleaning, as penetration is required to effectively clean the sides of the probes and remove debris from the vertical surfaces of microcantilevered probes. With the featured materials, the surface deflection was decoupled such that the peripheral probes received uniform cleaning<sup>[8]</sup>. Some examples of "positive, protruding" functional microstructures (PMD-type), and "negative, recessed" functional microstructures (WFL-Type), that were developed and fabricated for online and offline cleaning, are shown in Figures 5 and 6, respectively.

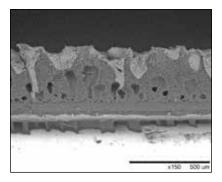

Controlled ultra-low-force cleaning efficiencies in the X, Y, and Z directions without any probe damage were possible within a single touchdown. The functionalized surfaces/shape was effective for maintaining the shape vertical probes without excessive penetration and adherent debris was efficiently removed from the tips of microcantilever probes<sup>[9]</sup>. Such low-impact and highly efficient cleaning is important for maintaining stable electrical contact integrity required for longterm, high-performance device testing. Surface utilization of the functionalized features after probe cleaning (Figure 7) was validated for several predetermined heights, depths, pitches, and shapes ranging from 10um up to 200um. Following the performance testing, several WFL-Type and PMD-Type geometries were qualified use in on-line cleaning during high-volume-production and off-line probe card maintenance.

#### **Application Case Study**

Polymer-based cleaning materials are regularly used to clean large area array microcantilever probes during wafer level test of memory and automotive

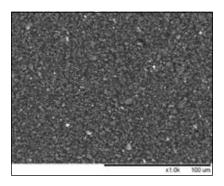

Figure 5. SEM and 3D images of highly cross-linked and abrasively loaded elastomeric polymers with a tacky surface that is functionalized with "positive, protruding" microstructures (PMD-Type) for contact area polishing and accumulated debris removal.

Figure 6. SEM and 3D images of highly cross-linked and abrasively loaded elastomeric polymers with a tacky surface that is functionalized with "negative, recessed" microstructures (WFL-Type) for contact area polishing and accumulated debris removal.

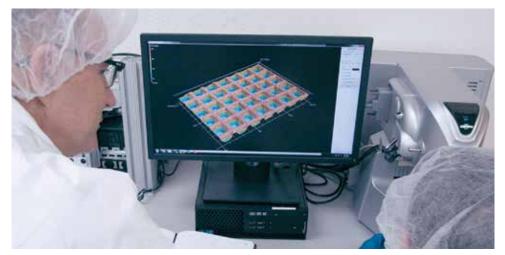

Figure 7. After performance testing, detailed 3D visualization, surface integrity assessment, and metrology of the functionalized microfeatures is performed in the CCME to assess the cleaning material utilization. By combining benchtop test strategies with high magnification video imaging, key insights are gained into the material performance and cleaning mechanisms.

### PACKAGING

Figure 8. Long-term, standard cleaning process using abrasively loaded elastomeric polymers was not 100% effective for complete cleaning and removal of debris from critical surfaces.