Presented at: MEPTEC / IMAPS Semiconductor Industry Speaker Series May 20, 2020

# Multi-disciplinary Simulation for 2.5D/3DIC Co-Design

Sooyong Kim Sr. Product Manager <u>sooyong.kim@ansys.com</u> 3DIC CPS Multiphysics

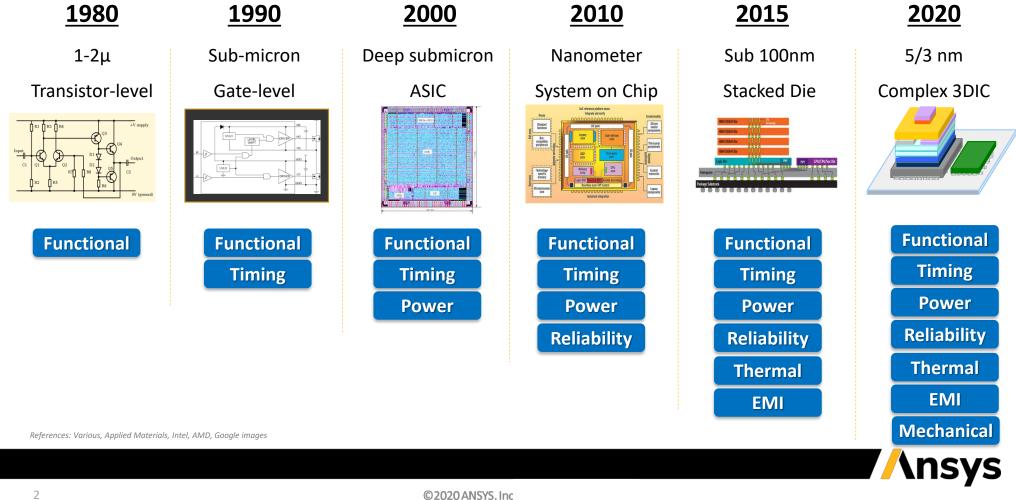

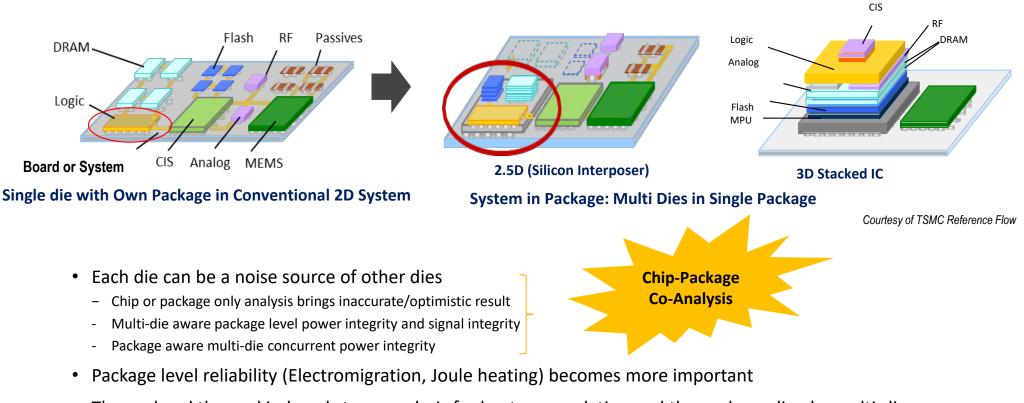

## **Evolution of Chip Design Complexity**

Multiphysics signoff is a MUST for silicon success

• Thermal and thermal induced stress analysis for heat accumulation and thermal coupling by multi-dies

### Challenges in 2.5D Stacking & Analysis Needs

| Characteristic | Interpose                                                                                      | Physics based analysis enabled by |  |         |                                                           |

|----------------|------------------------------------------------------------------------------------------------|-----------------------------------|--|---------|-----------------------------------------------------------|

| Characteristic | Ideal Properties                                                                               | Glass Silicon                     |  | Organic | Ansys                                                     |

| Electrical     | <ul><li>High Resistivity</li><li>Low Loss</li></ul>                                            |                                   |  |         | 2.5D Stacked Die Analysis<br>PI , SI , EM Workflows       |

| Thermal        | <ul><li>High Conductivity</li><li>CTE matched to Si</li></ul>                                  |                                   |  |         | 2.5D Stacked Die Analysis<br>TI Workflow                  |

| Mechanical     | <ul><li>High Strength</li><li>High Modulus</li></ul>                                           |                                   |  |         | 2.5D Stacked Die Analysis<br>Mechanical Analysis Workflow |

| Physical       | <ul> <li>Smooth Surface Finish</li> <li>Large area availability</li> <li>Ultra thin</li> </ul> |                                   |  |         | 2.5D Stacked Die Analysis<br>Structural Analysis Workflow |

| Chemical       | Resistance to process chemicals                                                                |                                   |  |         |                                                           |

| Processability | Ease of via formation                                                                          |                                   |  |         |                                                           |

| Cost           | Low cost per I/O at 25um pitch                                                                 |                                   |  |         |                                                           |

Source: Phil Marcoux , www.allvia.com

**//nsys**

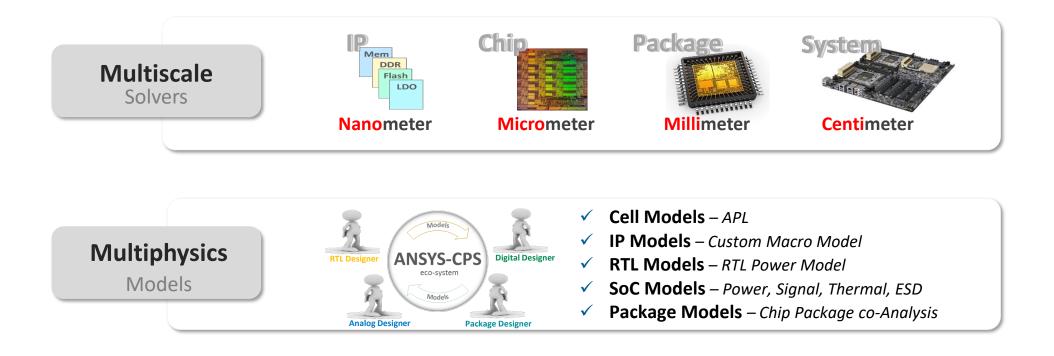

#### ANSYS Multiphysics Simulations for Electronics Systems Core Technologies

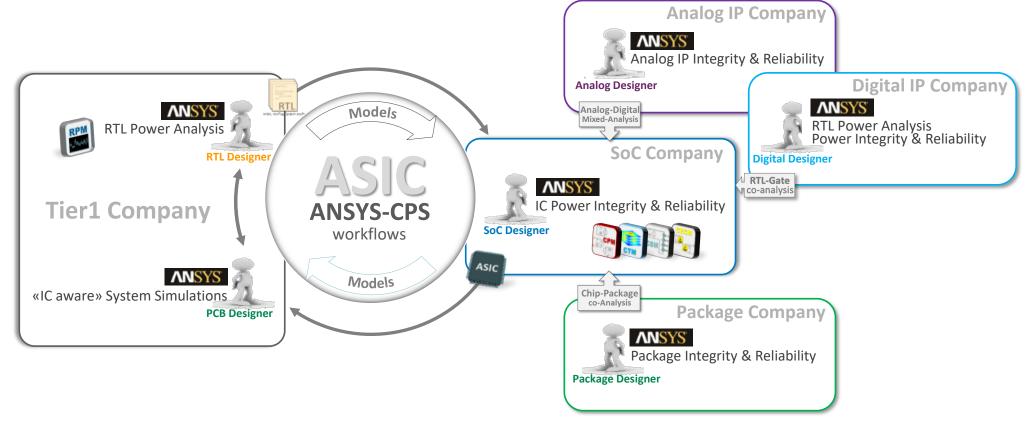

### Reality of Electronics Market Ecosystem

Application Specific Integrated Circuit Use Case

CPS: Chip Package System CPM: Chip Power Model CTM: Chip Thermal Model CSM: Chip Signal Model CECM: Chip ESD Compact Model RPM: RTL Power Model CPA: Chip Package Analysis CMM: Custom Macro Model

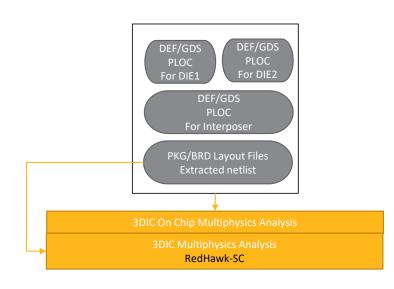

## Ansys Multiphysics solutions for 2.5D/3DIC design

Power Integrity

• Full PDN Power Integrity Signoff for Complex 2.5D/3DIC analysis

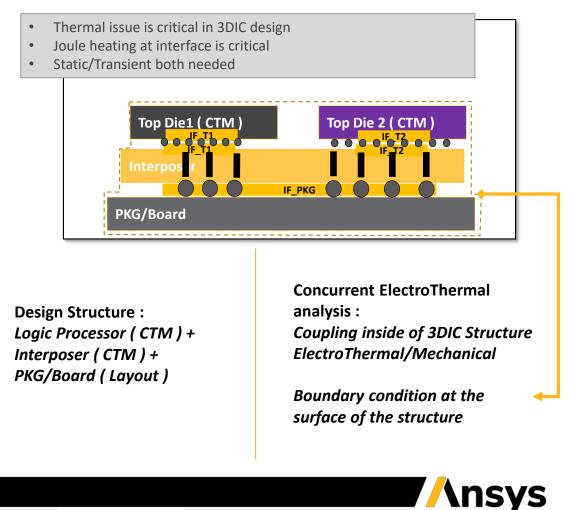

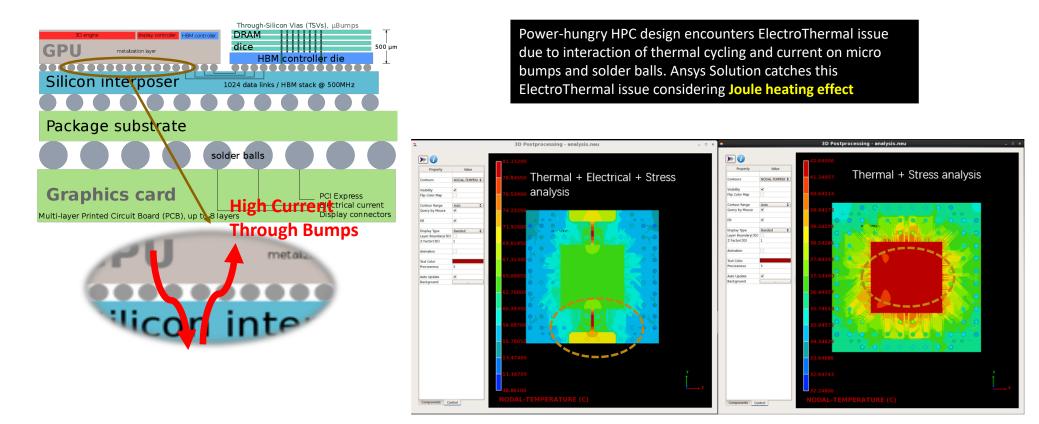

ElectroThermal/Mechanical Integrity

• Full ElectroThermal/Mechanical Integrity Sign off for Complex 2.5D/3DIC analysis

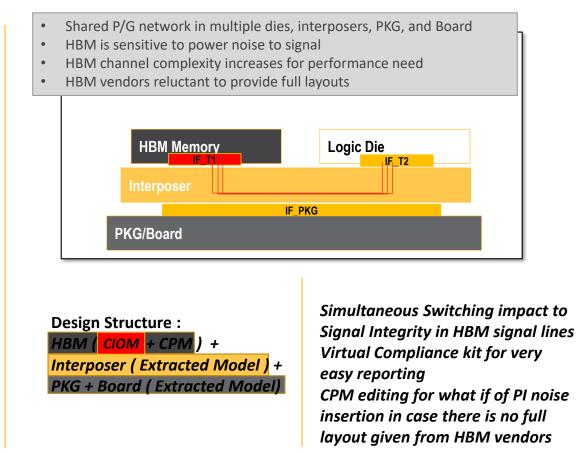

**Power Induced Signal Integrity**

• Chip Package System aware Power induced Signal Analysis for High Capacity HBM 3DIC structure

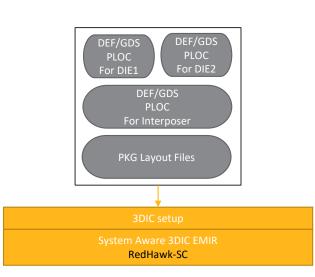

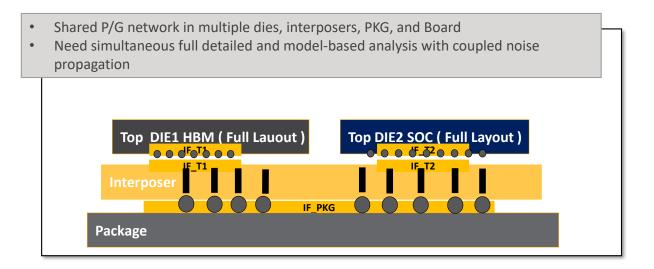

## System Aware 3DIC Chip Level PI analysis Flow concurrent analysis

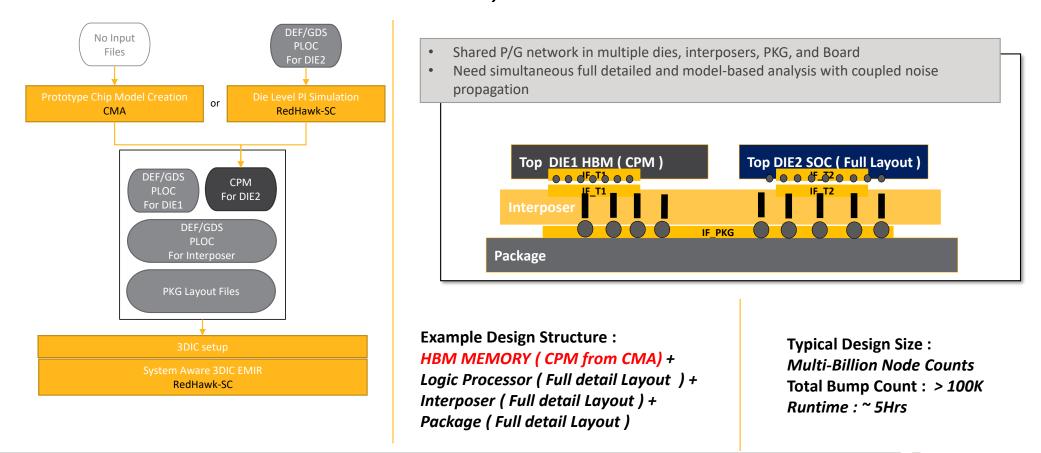

Example Design Structure : HBM MEMORY (Full Detail Layout) + Logic Processor (Full detail Layout) + Interposer (Full detail Layout) + Package (Full detail Layout)

Typical Design Size : *Multi-Billion Node Counts* Total Bump Count : > 100K *Runtime : ~ 5Hrs*

#### 2.5D/3DIC RedHawk-SC onchip power integrity maps

Full die and Interposer reports are in one session, 900mm^2 interposer size

## System Aware 3DIC Chip Level PI analysis Flow model based mixed with concurrent analysis

**//nsys**

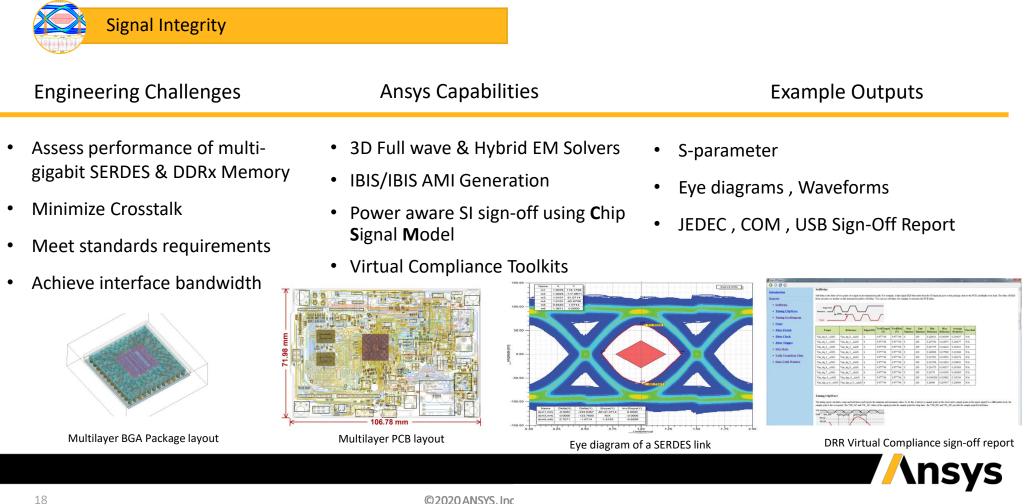

## How Ansys Delivers The Required Capabilities

| Power Integrity                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Engineering Challenges                                                                                                                                                                                | Ansys Capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Example Outputs                                                                                                                                                                                   |

| <ul> <li>Improve power efficiency</li> <li>Verify Power Delivery Network</li> <li>Power planes and Decoupling</li> <li>Meet emission compliance targets</li> <li>Minimize Electromigration</li> </ul> | <ul> <li>Signoff PDN from Transistor to system</li> <li>2D/2.5D/3DIC support</li> <li>Chip aware system co-analysis</li> <li>System aware chip co-analysis</li> <li>Multiscale modeling : Chip Power Model,<br/>Custom Macro Model, Chip Model Analyzer</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>Transient Power noise</li> <li>Current signature</li> <li>Voltage drop</li> <li>Impedance Profile</li> <li>Optimized Decoupling schemes</li> <li>Power/Ground Plane Resonance</li> </ul> |

| Current crowding       Voltage                                                                                                                                                                        | e drop at IC level to the set of | Electrical Model                                                                                                                                                                                  |

#### Ansys Chip Package System ElectroThermal/Mechanical Flow

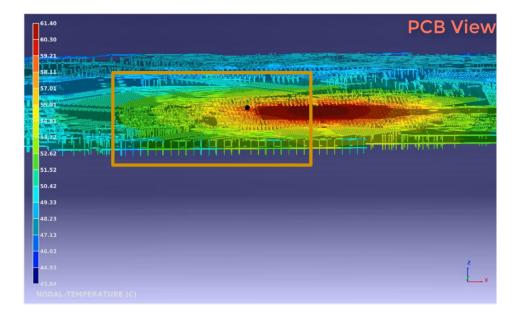

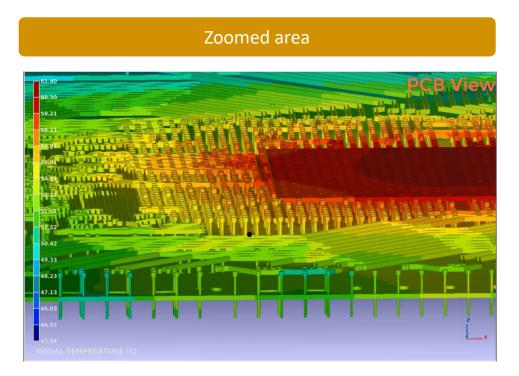

#### RedHawk-SC ElectroThermal Analysis Result Full 3DIC detailed Temperature Profile Maps

## ElectroThermal co-analysis

#### How Ansys Delivers The Required Capabilities

•

٠

**Engineering Challenges**

- FinFET Thermal Effects

- Joules heating

- Power dissipation

- Thermal runaway

- Thermal-induced stress

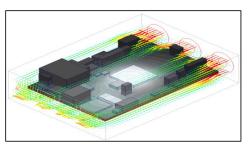

Full detailed Thermal for Chip Package PCB

ElectroThermal with Joule heating with bump current

Joule Heating with DC current

**Example Outputs**

- Heat map

- Temperature Contours

- Velocity Vectors

- Stress, deformation

Full System Level CFD thermal solver with air flow

**Ansys Capabilities**

Chip level Self heat analysis

CFD based thermal solver

Chip Thermal Model

Chip-aware system thermal analysis

System aware chip thermal analysis

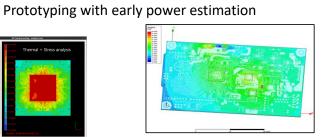

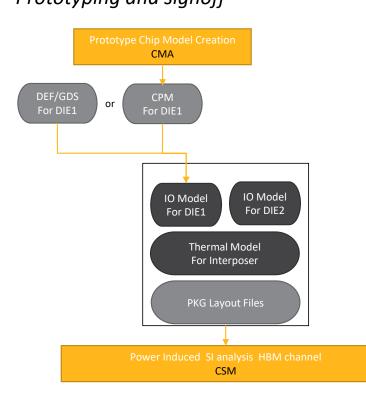

#### Chip Package System aware PSI Analysis for High capacity HBM Prototyping and signoff

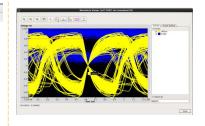

#### 2.5D/3DIC CSM Signal Integrity Power induced Signal Integrity analysis

#### JEDEC reports am Timing Noise Jitter Period Jitter Clock Jitter Trigger

5 ✔ DQa4/PAD WDQSa0/PADP \$ 0.792 10

6 ✔ DQa5/PAD WDQSa0/PADP \$ 0.792 10

7 ✔ DQa6/PAD WDQSa0/PADP \$ 0.792 10

8 V DQa7/PAD WDQSa0/PADP \$ 0.792 10

1 V DQa0/PAD WDQSa0/PADP \$ 0.792 20

2 ✔ DQa1/PAD WDQSa0/PADP \$ 0.792 20

4 ✔ DQa3/PAD WDQSa0/PADP \$ 0.792 20

5 V DQa4/PAD WDQSa0/PADP \$ 0.792 20

6 ✔ DQa5/PAD WDQSa0/PADP \$ 0.792 20

7 🖌 DQa6/PAD WDQSa0/PADP 🗢 0.792 20

8 ✔ DQa7/PAD WDQSa0/PADP \$ 0.792 20

| _ | _ |            | •              | b     | Start Time(ns) | End Time(ns) | Period Jitter(ns) | Pass/Fail |

|---|---|------------|----------------|-------|----------------|--------------|-------------------|-----------|

|   | 1 | ✔ DQa0/PAD | WDQSa0/PADP 🖨  | 0.792 | 10             | 200          | 0.0715096         | N/A       |

|   | 2 | ✔ DQa1/PAD | WDQSa0/PADP 🖨  | 0.792 | 10             | 200          | 0.0720017         | N/A       |

|   | 3 | ✔ DQa2/PAD | WDQSa0/PADP    | 0.792 | 10             | 200          | 0.0709741         | N/A       |

|   | 4 | ✔ DQa3/PAD | WDQSa0/PADP    | 0.792 | 10             | 200          | 0.0715371         | N/A       |

|   | 5 | ✔ DQa4/PAD | WDQSa0/PADP \$ | 0.792 | 10             | 200          | 0.0728677         | N/A       |

|   | 6 | ✔ DQa5/PAD | WDQSa0/PADP    | 0.792 | 10             | 200          | 0.0710761         | N/A       |

|   | 7 | ✔ DQa6/PAD | WDQSa0/PADP    | 0.792 | 10             | 200          | 0.072928          | N/A       |

|   | 8 | ✔ DQa7/PAD | WDQSa0/PADP    | 0.792 | 10             | 200          | 0.0700145         | N/A       |

| 5 🖌 DQa4/PA         | AD WDQSa0/PADP               | ÷  | 0.792                | 10                              | 200                             | 0.0728677                         | N/A                        |

|---------------------|------------------------------|----|----------------------|---------------------------------|---------------------------------|-----------------------------------|----------------------------|

| 6 🖌 DQa5/PA         | AD WDQSa0/PADP               | \$ | 0.792                | 10                              | 200                             | 0.0710761                         | N/A                        |

| 7 🖌 DQa6/PA         | AD WDQSa0/PADP               | ¢  | 0.792                | 10                              | 200                             | 0.072928                          | N/A                        |

| 8 🖌 DQa7/PA         | AD WDQSa0/PADP               | \$ | 0.792                | 10                              | 200                             | 0.0700145                         | N/A                        |

| SelfDelay<br>Target | Waveform Timing<br>Reference | 1  | Eyediagra<br>Vref(V) | m Timing Nois<br>Start Time(ns) | e Jitter Perioo<br>End Time(ns) | Jitter Clock<br>Period Jitter(ns) | Jitter Trigge<br>Pass/Fail |

| 1 🖌 DQa0/P/         | AD WDQSa0/PADP               | ¢  | 0.792                | 10                              | 200                             | 0.174517                          | N/A                        |

| 2 🖌 DQa1/P/         | AD WDQSa0/PADP               | \$ | 0.792                | 10                              | 200                             | 0.174671                          | N/A                        |

| 3 🖌 DQa2/PA         | AD WDQSa0/PADP               | \$ | 0.792                | 10                              | 200                             | 0.174613                          | N/A                        |

| 4 🖌 DQa3/P/         | AD WDQSa0/PADP               | ¢  | 0.792                | 10                              | 200                             | 0.174773                          | N/A                        |

0.17461

0.174908

0.174614

0.174919

0.605613

0.600637

0.604458

0.602089

0.597891

0.602697

0.597195

0.604444

N/A

200

200

200

200

150

150

150

150

150

150

150

150

SelfDelay | Waveform Timing | Eyediagram Timing | Noise | Jitter Period | Jitter Clock | Jitter Trigger Target Reference Vref(V) Start Time(ns) End Time(ns) Period litter(ns) Pass/Fail

\*\*\*\*\*\*\*\* Buffer DRAM ............ ........ Si Interposer .....

CMA generates CPM with power noise connecting to a Channel Model in CSM for Signal Integrity Analysis

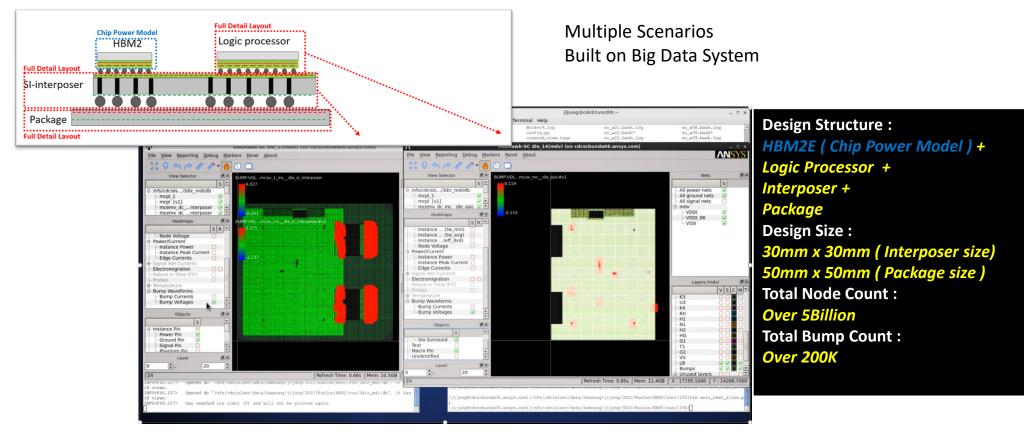

**Design Structure :** HBM2E ( Chip Power Model ) + Logic Processor + Interposer + Package **Design Size :** 30mm x 30mm (Interposer size) 50mm x 50mm ( Package size ) **Total Node Count : Over 5Billion Total Bump Count : Over 200K**

#### How Ansys Delivers The Required Capabilities