## "Structurally-Functionalized-Cleaning Materials"

### **Optimization for In-Situ Cleaning during Wafer Level and Package Test**

SVP of Technology Development International Test Solutions, Inc. Reno, Nevada USA

#### **Overview**

- Introductions and Background

- Advanced Packaging and Importance of Test

- Functionalized Cleaning Materials for Data Quality

- Open Discussion and Questions

Who We Are ....

## Visionary Innovative Collaborative

international

**TEST SOLUTIONS**

- 21 years of cleaning materials innovation

- Headquartered in Reno, NV, USA

- Offices in Taiwan, Europe, Japan, Korea, China, and Singapore.

- Over 75 US domestic and international patents.

- Industry's broadest portfolio of probe card, socket, and wafer chuck cleaning technologies.

- Utilized worldwide at more than 80% of the IDMs, OSATs, and Foundries.

- Trusted and known by the industry as "the cleaning experts".

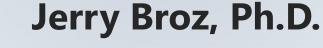

## **ITS Markets and Products at a Glance**

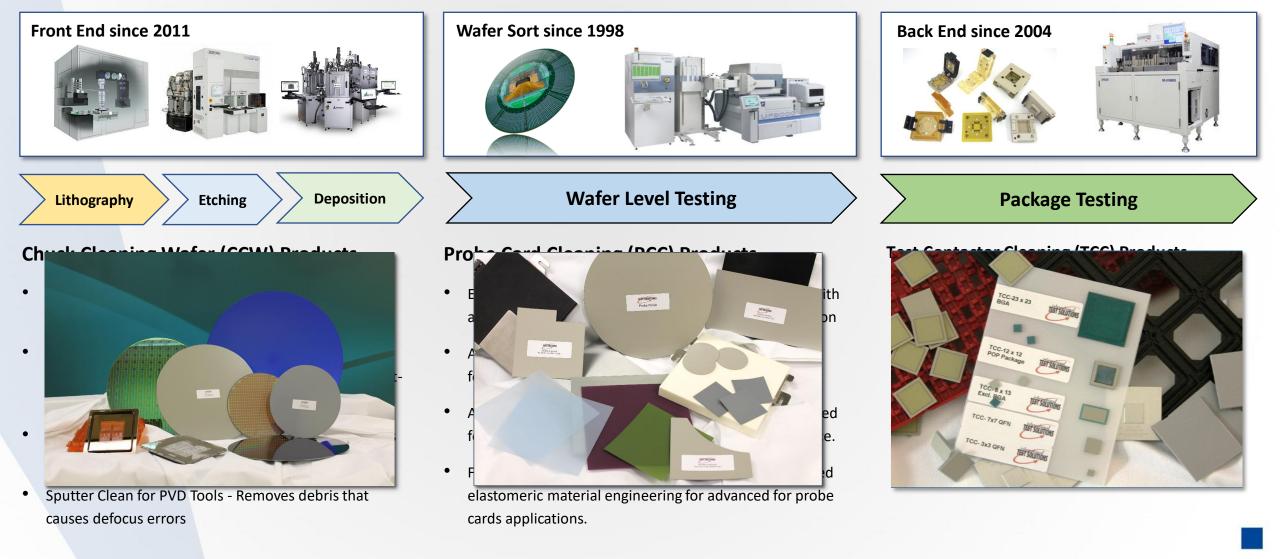

## **Application Landscape Drives Complexity**

Data Cloud and AI Explosion of Data, High Capacity Storage, and HPC growing from 5 Zetabytes to > 40 Zetabytes

#### 5G and Massive Connectivity

More than 1.1 billion smart-device and high-volume connections

#### Smart Devices

More than 250 million wearables and highperformance devices

#### **Internet of Things** 50B connected devices of low-cost devices and massive

data volumes

#### **Automotive Electronics**

89 million connected cars each generating and processing > 1GB of data per second

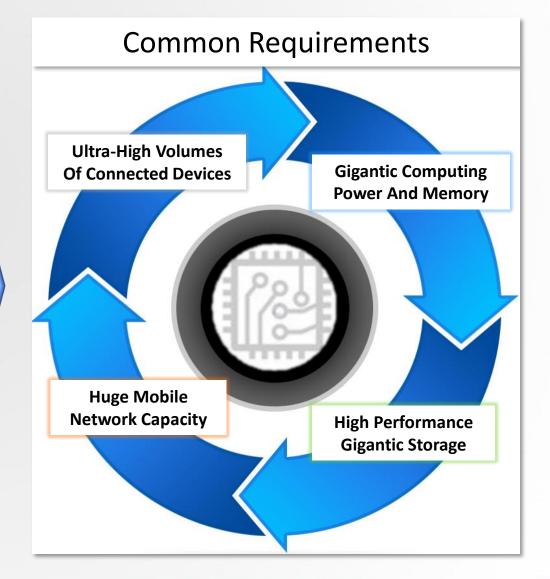

### Alternate Path to SoC Scaling in post-Moore's Law Era

- Few players (basically 3) at the advanced nodes.

- Continuing with a "monolithic" SoC Approach has high development costs.

- Materials and structural innovations have economical benefits; BUT, long cycle times.

- Heterogeneous integration uses "best-in-class technology" in a way to continue performance trends at acceptable costs.

- Rather than scaling features on a monolithic die, advanced packaging expands in the vertical direction.

- Heterogeneous integration can economically increase transistor density.

Source: Samsung Foundry Forum, Semicon West

#### There's no "one-size-fits-all" approach that works anymore.

#### **Heterogeneous Integration Roadmap**

1110

ITDO .

photonics

• Known Good Die and Cost Management are keys for success.

semr

https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2019-edition.html

| From ITRS to HIR                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                         | HIR Technical Working Groups                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ITRS:<br>1991 - 2015<br>Precompetitive<br>15 years outlook & 25 years for emerging<br>materials & devices<br>Sponsored by five global semiconductor<br>associations. Appoint IRC & approve<br>governance<br>Volunteer driven<br>Free access<br>CMOS "Moore's Law" node driven<br>17 Technical Working Groups | HIR:<br>2016<br>• Precompetitive<br>• 15 years outlook & 25 years for emerging<br>materials & devices<br>• Sponsored by IEEE technical societies &<br>organizations with similar outlook. Appoint<br>IRC & approve governance<br>• Volunteer driven<br>• Free access<br>• Systems & application driven<br>• 22 Technical Working Groups | <ul> <li>Heterogeneous Integration Components</li> <li>Single Chip and Multi Chip Packaging</li> <li>(including Substrates)</li> <li>Integrated Photonics</li> <li>Integrated Power Devices</li> <li>MEMS</li> <li>RF and Analog Mixed Signal</li> <li>Cross Cutting topics</li> <li>Emerging Research Materials</li> <li>Emerging Research Devices</li> <li>Interconnect</li> <li>Test</li> </ul> | <ul> <li>Integration Processes <ul> <li>SiP</li> <li>3D +2.5D</li> <li>WLP (fan in and fan out)</li> </ul> </li> <li>Packaging for Specialized Applications <ul> <li>Mobile</li> <li>IoT and Wearable</li> <li>Medical and Health</li> <li>Automotive</li> <li>High Performance Computing</li> </ul> </li> <li>Design <ul> <li>Co-Design &amp; Simulation – Tools &amp; Praction</li> <li>Device, package, subsystem &amp; system levels</li> </ul> </li> </ul> |

|                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                         | HIR is proposing a Supply Chain TWG focused on pre-competitive requirements                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### J. Broz / 20-May-2020 MEPTEC – iMAPS Speaker Series

EEE

7

## **Wafer-Level and Package-Level Testing**

Always Under Pressure of Test Cost Reduction **Provide Feedback for Wafer Manufacturing**

- Until incremental testing is completed, it is hard to tell which is good die.

**Provide Data to Improve Circuit Design and Layout**

Keep High Yield through Repair, Rework, and Retest

Make Adjustment by Calibration

**Facilitate High Density Multi-Die with KGD Solutions**

Minimize Defects and Reliability Risks

Source: TEL Keynote at SWTest Asia 2019

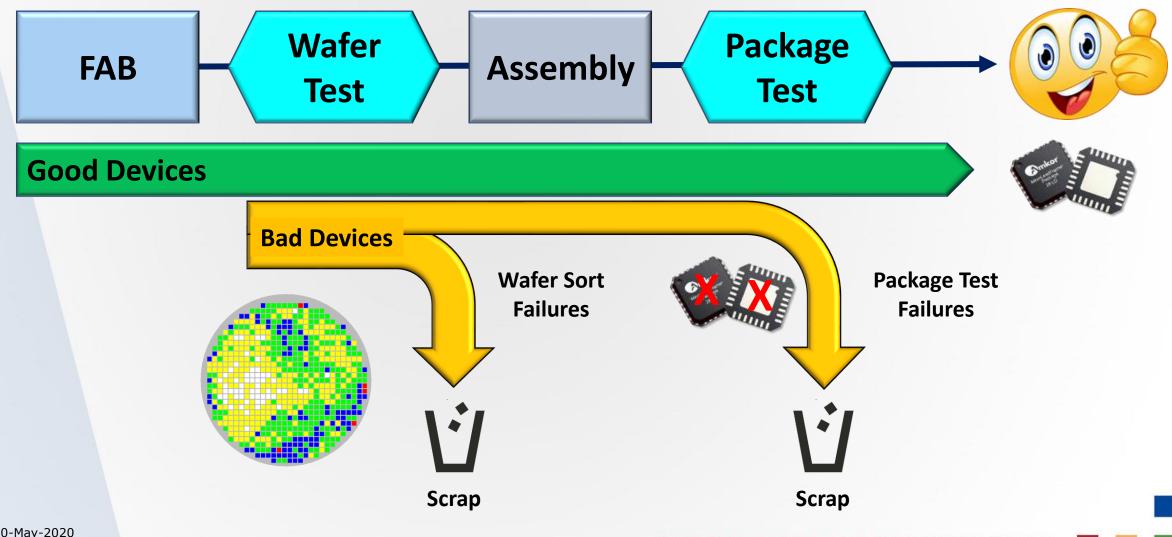

## "Traditional" Device Test Flow

J. Broz / 20-May-2020 MEPTEC – iMAPS Speaker Series

IMPROVING YIELD THROUGH INNOVATION.

9

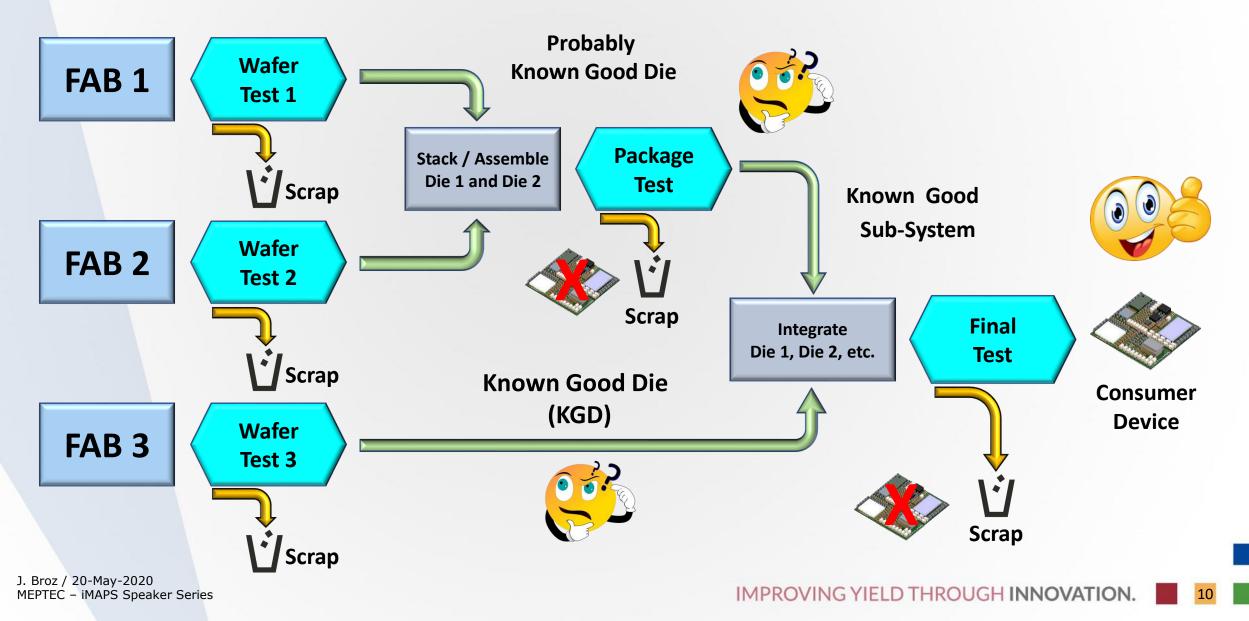

## **Advanced Package Device Test Flow**

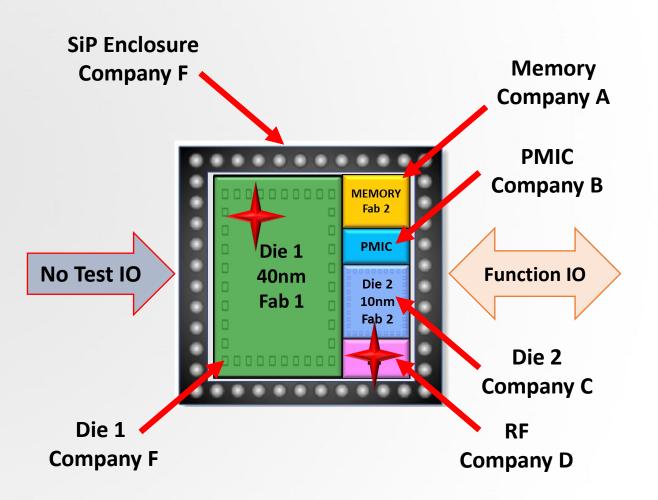

## **Challenges for Heterogeneous Integration**

- Lack of Testability

- Different test strategies needed individual memory, mixed-signal, RF block, PMIC, etc.

- Limited test ports on the final package

- Difficulty of Quality Control

- Chips and final packages come from different companies

- Quality of final product can be difficult to control

#### Difficult to Locate Faults

- Die-to-Die communication

- Tools to find defects within failed chip

- FA requires a lot of manpower and analysis

- Data Quality and Data Integrity at Wafer-Level and Package-Level are Critical

- Probe / Contactor Connection

- High First Pass Yields

- Assurance of Device Performance

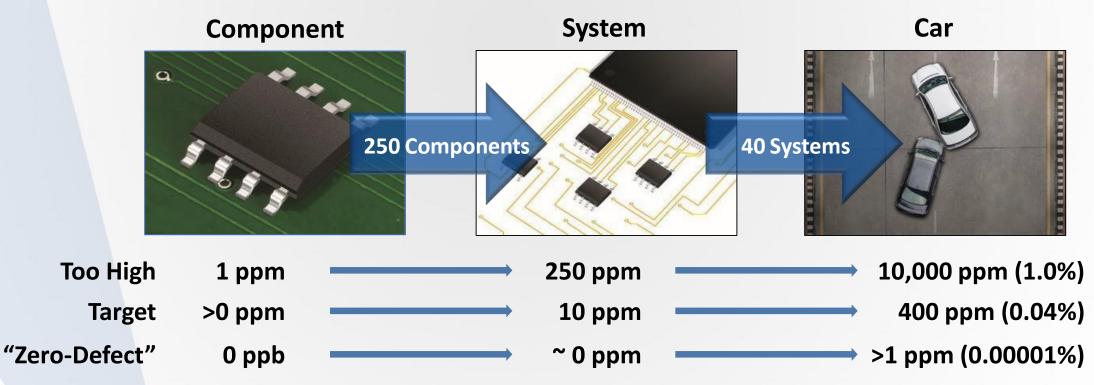

## **Test Thoroughness Prevents the "Multiplier Effect"**

#### Automotive Sector needs to be a "Zero-Defect" World

- Automotive defect levels are 10X more stringent than mobile and consumer.

- Parts per billion (ppb) failure rates basically mandate "Zero-Defect" manufacturing.

- Performance is now being measure in "Raw Incidents".

Source: Infineon Technologies, Texas Instruments, AMKOR, SiP China 2018

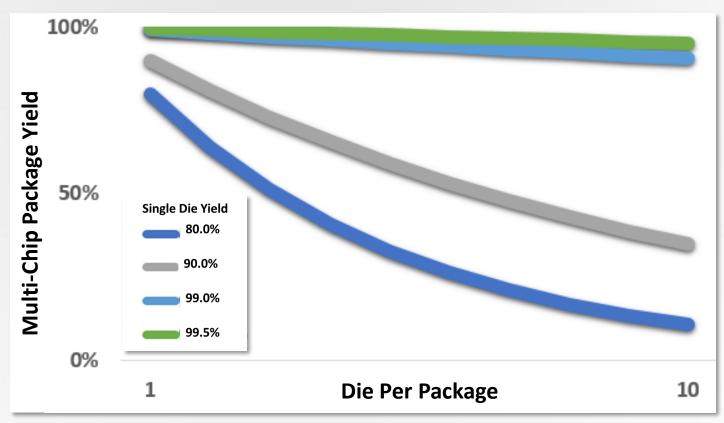

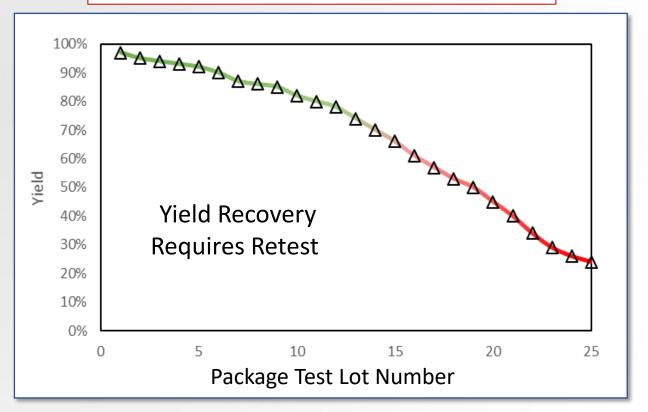

## Wafer Test Cost vs. Package Test Cost

- Wafer test costs to assure KGD could be higher than the package test costs.

- High yields of multichip packages will impact on overall Cost of Test.

- Data integrity is critical to assure high first pass yield and reduce retest

Source: Micron, Keynote at SWTest 2019 San Diego

J. Broz / 20-May-2020 MEPTEC – iMAPS Speaker Series

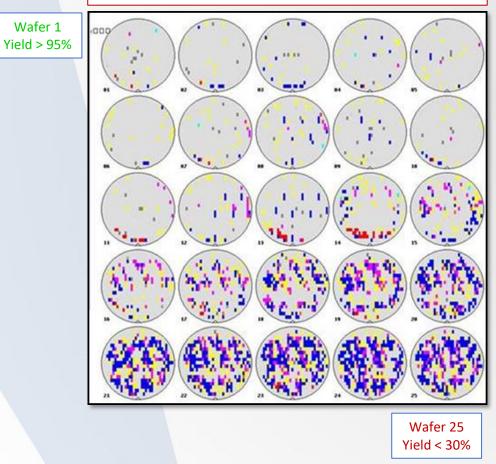

## **Data Integrity (and Yield) Impacted by Cleaning**

#### Wafer Yield Drops When **No Probe Cleaning is Performed**

#### **First Pass Package Yield Drops When No ACC Cleaning is Performed**

Wafer 1

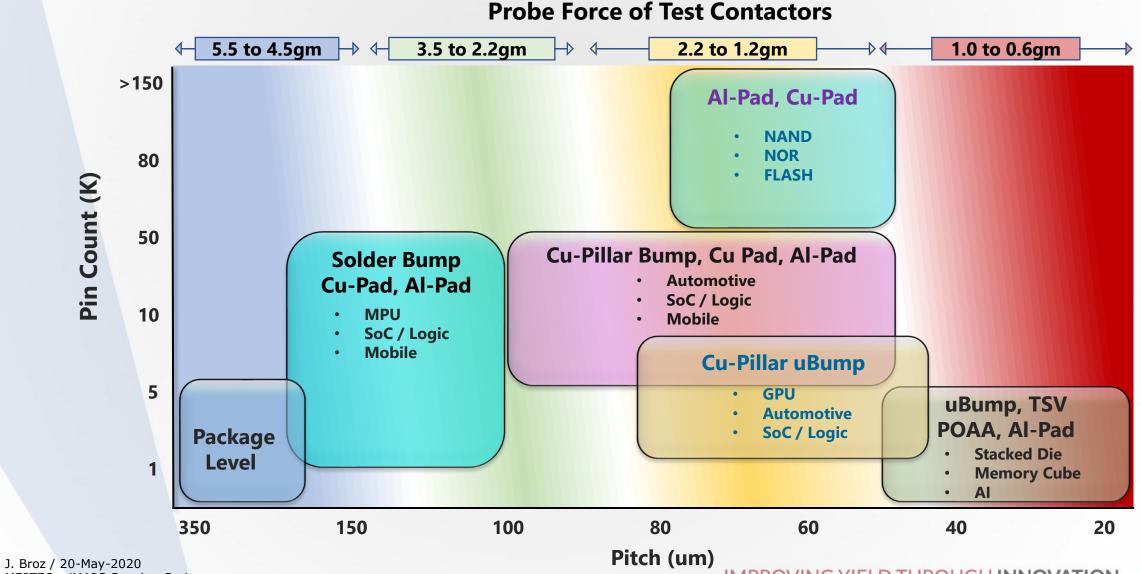

## Wafer and Package Test Complexity Landscape

MEPTEC - iMAPS Speaker Series

IMPROVING YIELD THROUGH INNOVATION

internationa TEST SOLUTION

## "Simple" In-Situ Cleaning Materials

- It is well-known that efficient control of contamination is critical for sustaining high yields.

- Cleaning materials remove debris and maintain surface texture for reliable electrical contact.

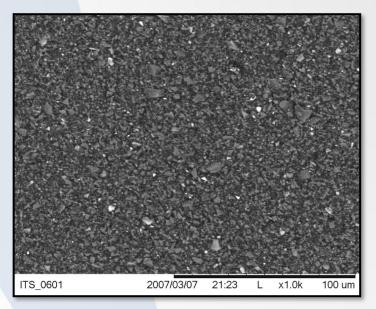

#### **Abrasive Films**

• Surface roughness for tip texturing and material removal

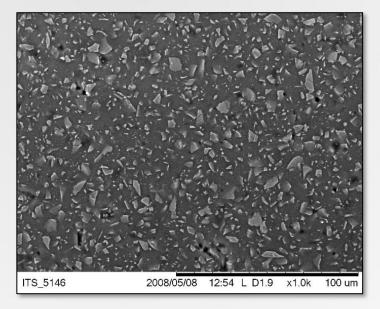

#### **Elastomeric Polymers**

Abrasively loaded, compliant polymers with a tacky surface

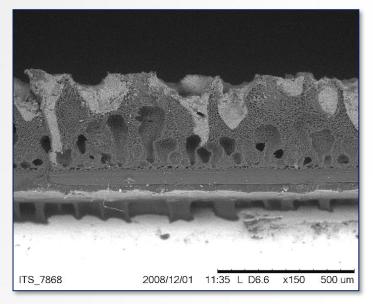

#### **Abrasively Coated Foam**

• Low-chlorine polyurethane foam for tip shape control

## "Functionalized" for In-Situ Probe Cleaning

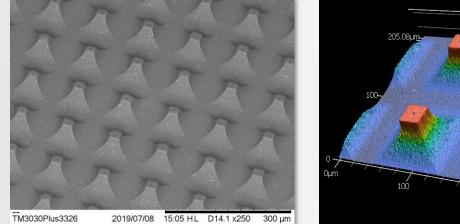

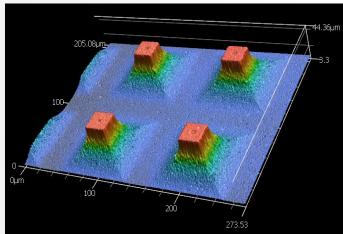

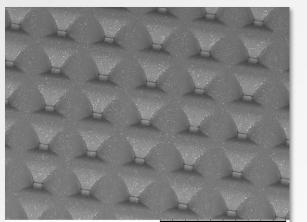

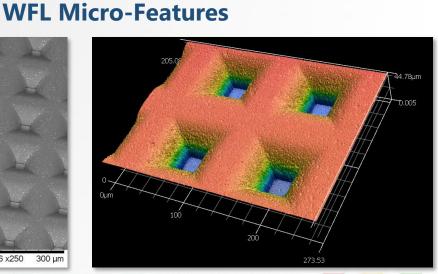

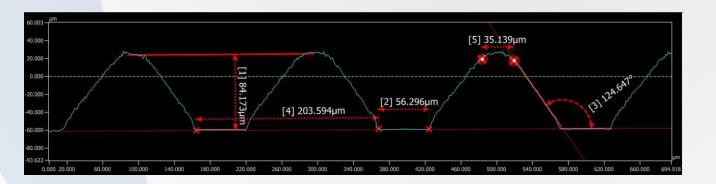

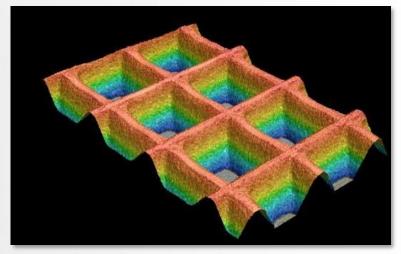

#### **PMD Micro-Features**

- "Simple" cleaning materials <u>CAN NOT</u> meet the critical requirements of future contactors.

- Functional microstructures can provide benefits not possible with a featureless surface.

- "Next Generation" materials have controlled cleaning efficiency in the x, y, and z directions during each cycle.

- ITS' patented functional microfeature cleaning materials are built with engineered geometries ranging in sizes from 10um to 250um to optimize cleaning performance.

TM3030Plus3329 2019/07/08 15:09 HL D13.6 x250 300 μm

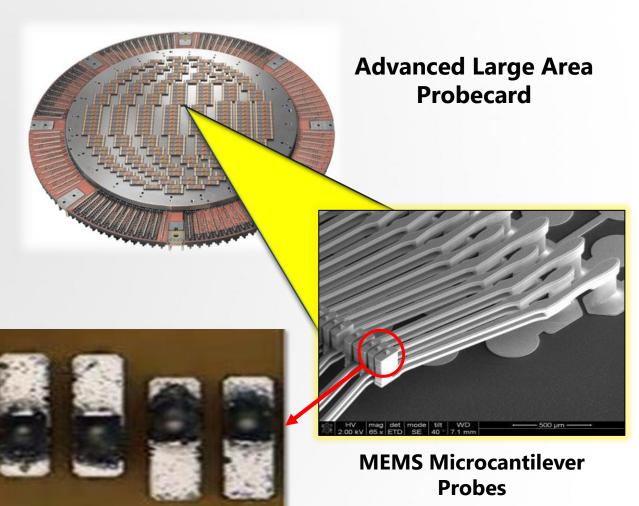

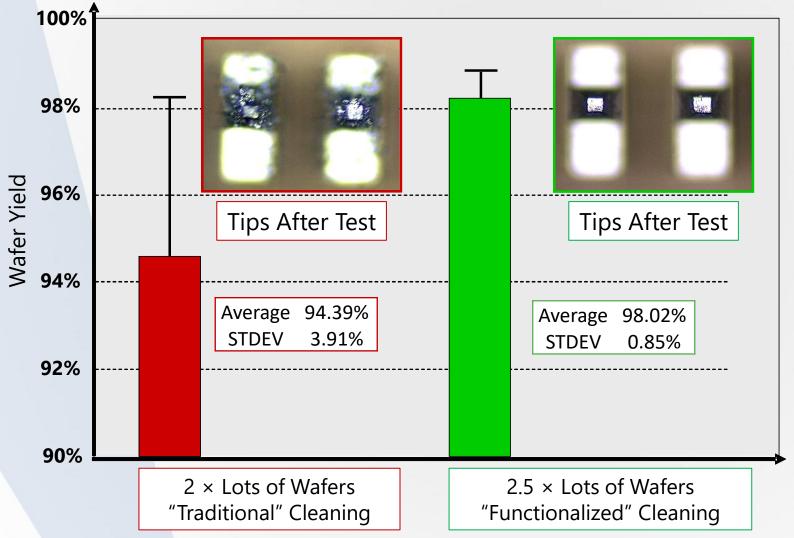

## **Case Study 1: Wafer Level Test**

#### Challenge

Unstable wafer yields during high volume production level memory testing with advanced large area array probe cards.

#### Overview

- Unstable 1st pass yield due to contamination

- Operator intervention due to debris accumulation.

#### Cleaning Process Improvement Strategy

- Implement functionalized cleaning materials

- Maximize 1st pass yield stability

- Reduce Lot-to-Lot yield variations

- Reduce overall Cost of Test

"Simple" Cleaning Process Is Ineffective on Critical Surfaces

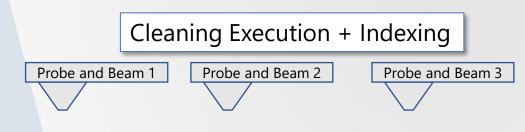

## **Microfeature Cleaning Validation**

- Cleaning executed on WFL functionalized features produces an efficient cleaning action on the probe tip, sides, and base.

- Probe and Beam 1 = direct contact with WFL ridge

- Probe and Beam 2 = side/base contact with WFL side

- Probe and Beam 3 = side/front contact with WFL ridge

#### **WFL Microfeatured Material**

Functionalized Cleaning Material Cleans <u>ALL</u> Critical Surfaces

## **Implementation Results**

#### Process Improvement

- Reduction in yield variance

- Yield improvement  $\approx 4\%$

#### Production Metrics Benefits

- Less operator assist

- Reduced downtime

- Operating efficiency improvements

- Reduced overall cost of test

- "High" Confidence for KGD

# TEST SOLUTIONS

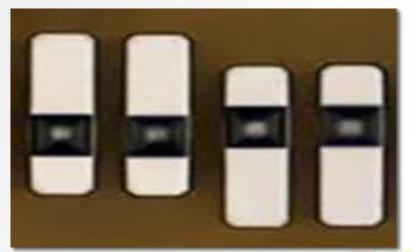

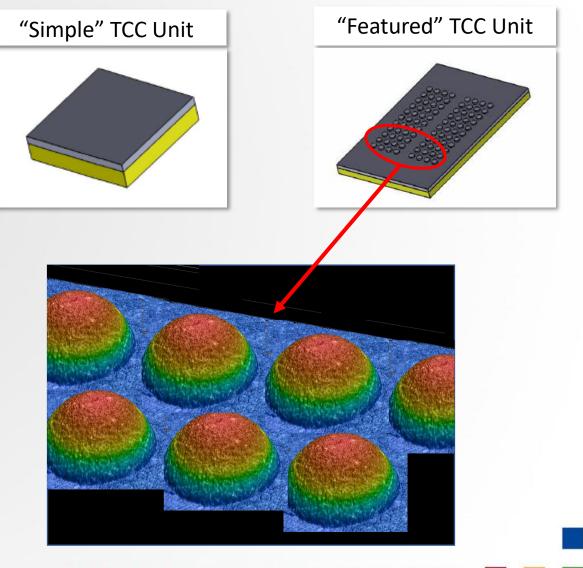

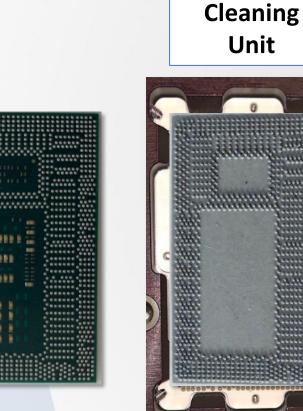

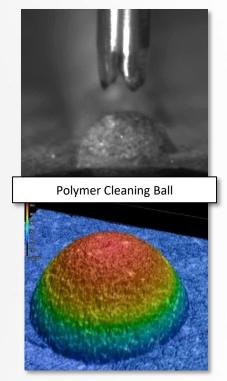

## "Functionalized" In-Situ Socket Cleaning

- "Simple" Test Contactor Cleaning (TCC) devices are built with a flat cleaning layer applied to a substrate.

- Advanced TCC units can be built with functionalized abrasive polymer "cleaning balls" to emulate device solder ball size and pitch

- "Cleaning Balls" will nest into the socket floor for precise ball to pin alignment in the guide hole.

## **Case Study 2: Package Level Test**

DUT

TM3030Plus3359 2019/04/30 12:35 HL D13.4 x150 500 um

#### Turnkey cleaning unit with "Polymer Cleaning Balls"

- "Cleaning balls" nest into the floating base guides of the socket

- Provide precise pin alignment for fine pitch devices.

- Cleaning devices are also built using top and bottom optical features for the accurate alignment required for PoP devices.

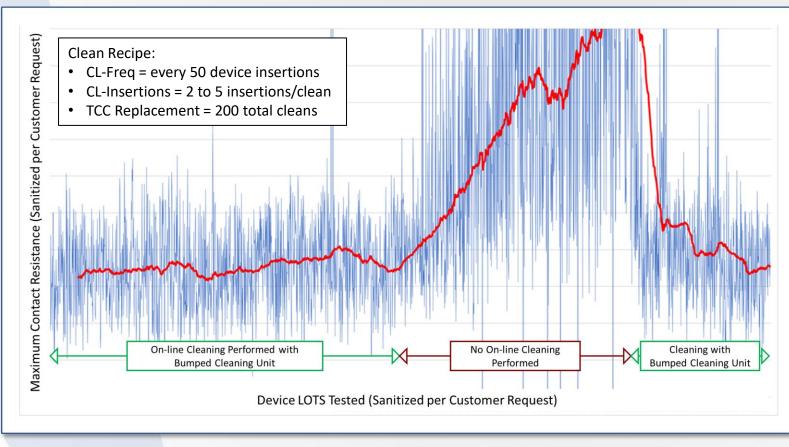

## "Sanitized" Test-floor Results for HVM Customer

When on-line cleaning was terminated, CRES variance dramatically increased.

| Device A     | First Pass Yield | Retest Yield |

|--------------|------------------|--------------|

| Manual Clean | 97.25%           | 1.40%        |

| ACC Clean    | 98.36%           | 0.57%        |

| Yield Gain   | 1.11%            | 0.83%        |

|              |                  |              |

| Device B     | First Pass Yield | Retest Yield |

| Manual Clean | 92.49%           | 3.04%        |

| ACC Clean    | 93.26%           | 2.48%        |

| Yield Gain   | 0.77%            | 0.56%        |

|              |                  |              |

| Device C     | First Pass Yield | Retest Yield |

| Manual Clean | 88.77%           | 3.86%        |

| ACC Clean    | 91.99%           | 2.61%        |

| Yield Gain   | 3.23%            | 1.25%        |

With consistent ACC implementation, CRES (and Data Quality) is controlled to significantly increase first pass yields.

## **Summary / Discussion**

#### • New test strategies, tooling, and materials are necessary for reaching the next nodes.

- Heterogeneous integration uses "best-in-class IP" to advance performance at lower costs.

- Higher costs of consumable products are expected (probes, probe cards, sockets, interface boards, etc.)

#### Reliable wafer and package test results are necessary for "Known Good Die" requirements

- Increased number of measurements and required to assure "good die".

- Significant impact for cost of test with longer test times for thoroughness.

- Unnecessary retest will dramatically increase the cost of test.

#### Contact resistance and contamination control are critical aspect for reduced retest

- "Next Generation" test contactor technologies require appropriate cleaning technologies.

- Reduce chance of discarding devices that would otherwise have been good.

#### "Functional" cleaning materials keep pace with test technology complexity.

- Functionalized geometries facility accurate cleaning efficiency

- Functional microstructures have performance benefits not possible with "flat" (non-featured) structures.

- Controlled cleaning efficiency of advanced contactors are attained in the x, y, and z directions.

# TEST SOLUTIONS

## Acknowledgments

- Cooper Smith (PCC Products Manager)

- Bret Humphrey (TCC Products Manager)

- Gene Humphrey (ITS President)

- ITS Customers and Technical Collaborators

## "Thanks for Attending"

## **Questions** ???

#### Jerry Broz, Ph.D.

SVP of Technology Development International Test Solutions, Inc. Reno, Nevada USA

IMPROVING YIELD THROUGH INNOVATION.

Copyright | © 2020 International Test Solutions | All Rights Reserved