# MEPTECReport

A Quarterly Publication of the Microelectronics Packaging & Test Engineering Council

Volume 21, Number 3

# MEPTEC 2017 SEMICONDUCTOR PACKAGING SYMPOSIUM HETEROGENOUS INTEGRATION - THE ROAD TO IMPLEMENTATION Thursday, November 30, 2017 - San Jose, CA

page 11

Where is the Semiconductor Manufacturing Sweet Spot?

page 12

STATE-OF-THE-ART TECHNOLOGY BRIEFS IBM Zurich researchers have developed a tiny redox flow battery. Future computer chip stacks, in which individual chips are stacked to save space and energy, could be supplied with electrical power and cooled at the same time with these integrated flow batteries. page 23

## **INSIDE THIS ISSUE**

The 67th ECTC lived up to its reputation as the premium international event of the microelectronics packaging industry.

The Heterogeneous Integration Roadmap has accomplished a great deal in the first year.

Advanced packaging industry's first movers, competitive advantage, and disruptive innovations.

Do MEMS work for you? Yes, of course. You use them every day when you use your phone, drive your car, and look at your watch.

# The SiP Company

Innovative IC, SiP, and MEMS packaging portfolio to serve dynamic mobility, IoT, high performance computing, and automotive markets.

PoP • Flip Chip • SiP • WLP • Fanout • FOCoS 2.5D • TSV • Flex • AoP • AiP • Shielding Wire Bond • Embedded • Substrate • Co-Design

# Package it.

У @asegroup\_global

Saseglobal.com

#### The MEPTEC Report is a Publication of the Microelectronics Packaging & Test Engineering Council

315 Savannah River Dr., Summerville, SC 29485 Tel: (650) 714-1570 Email: bcooper@meptec.org

Publisher MEPCOM LLC Editor Bette Cooper Art Director/Designer Gary Brown Sales Manager Gina Edwards

#### MEPTEC Advisory Board

**Board Members**

Ivor Barber AMD

Jeff Demmin Booz Allen Hamilton

Douglass Dixon Henkel Corporation

Nick Leonardi SMART Microsystems

Phil Marcoux PPM Associates

Gamal Refai-Ahmed Xilinx

Rich Rice ASE (US) Inc.

Minghao Shen Altera

Scott Sikorski STATS ChipPAC

Jim Walker WLP Concepts

Special Advisors

Ron Jones N-Able Group International Mary Olsson Gary Smith EDA

Honorary Advisors

Seth Alavi Sunsil

Gary Catlin

Rob Cole

Skip Fehr

Anna Gualtieri Elle Technology

Marc Papageorge ICINTEK

In Memoriam

Bance Hom

#### Contributors

Matt Apanius SMART Microsystems Ltd. Bill Bottoms, Ph.D. Third Millennium Test William Boyce SMART Microsystems Ltd. Jinu Choi Henkel Electronic Materials LLC Doug Dixon Henkel Electronic Materials LLC Ira Feldman Feldman Engineering Corp. Ron Jones N-Able Group International Dr. Gamal Rafai-Ahmed Xilinx Rick Yogelei Semico Research Corporation Paul Werbaneth Intevac, Inc. MEPTECReport B

A Quarterly Publication of The Microelectronics Packaging & Test Engineering Council

Volume 21, Number 3

## ON THE COVER

**RICK VOGELEI**

**MEPTEC**Report

The MEPTEC 2017 Semiconductor Packaging Symposium - Heterogenous Integration - the Road to Implementation, will be held on Thursday, November 30, 2017 at the SEMI Global Headquarters in Milpitas, CA. This event will explore three issues central to the successful execution of heterogeneous integrated packages: Can the packaging community establish a real design for heterogeneous integration ecosystem? Should we rethink the reliability standards for these heterogeneous integrated SIP packages? What are the best test strategies for these heterogeneous integrations, or at least what are the guiding principles?

**12** ANALYSIS – Where is the semiconductor manufacturing sweet spot? Two recent Semico Research Corp. studies provide the information to not only determine the overall sweet spot but to dig even further to find which products and technologies are the driving forces behind the growth or decline.

| SEMICO | RESEARCH | CORPORATION |

|--------|----------|-------------|

|        |          |             |

|        |          |             |

| Heterogeneous<br>Roadmap – Th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | e First Year                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 100                                                |           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| which phone and |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                    |           | exercise of the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | point of atoms. Now solve simplify a point of atoms the set of a point of a | (c) (b) (b) (c) (c) (c) (c) (c) (c) (c) (c) (c) (c | 1999 F 19 | Kitti kusa hekyy (voi<br>faran () ke (Masa)<br>() kasa () ke (Masa)<br>() kitti<br>() kitti | The sectors of the sector of t |

**4** TECHNOLOGY – The Heterogeneous Integration Roadmap serves our profession, industry, academia, government and research institutes to meet the challenges of this new world by stimulating pre-competitive collaboration. This collaboration enables resolution of difficult challenges before they become roadblocks to continuation of the rate of progress.

WILMER R. BOTTOMS, PH.D. THIRD MILLENNIUM TEST SOLUTIONS AND HIR CO-CHAIR

**PACKAGING** – What happens to Intel's competitive advantage when Intel is no longer first mover for advanced process nodes in commercial semiconductor device fabrication? Or, conversely, how much of Intel's present success is a result of it having been the first mover in semiconductor fabrication process and packaging technology over the long period of time that it has?

#### PAUL WERBANETH INTEVAC, INC.

**23** TECH BRIEFS – The State-of-the-Art Technology Briefs contains articles from the Binghamton University S3IP "Flashes." Binghamton University currently has research thrusts in healthcare/medical electronics; 2.5D/3D packaging; power electronics; cybersecure hw/sw systems; photonics; MEMS; and next generation networks, computers and communications.

DR. GAMAL RAFAI-AHMED XILINX

DEPARTMENTS

7 Event Follow-Up 8 Coupling & Crosstalk

10 Industry Insights26 Henkel News20 SMART Microsystems News30 Opinion

MEPTEC Report Vol. 21, No. 3. Published quarterly by MEPCOM LLC, 315 Savannah River Dr.; Summerville, SC 29485. Copyright 2017 by MEPCOM LLC. All rights reserved. Materials may not be reproduced in whole or in part without written permission. MEPTEC Report is sent without charge to members of MEPTEC. For non-members, yearly subscriptions are available for \$75 in the United States, \$80US in Canada and Mexico, and \$95US elsewhere. For advertising rates and information contact Gina Edwards at 408-858-5493, Fax Toll Free 1-866-424-0130.

#### KYOCERA Technology Used to Create One of the World's Smallest Crystal Units Awarded Prestigious Research Prize in Japan

KYOCERA CORPORATION has announced that the company has received the 42nd Inoue Harushige Prize for developing ultra-small quartz crystal units for smartphones, wearable devices and innovative IoT solutions. The crystal units, which apply plasma CVM technology, were developed by Kyocera and Dr. Kazuya Yamamura, a professor at Osaka University.

Each year the Inoue Harushige Prize is awarded to researchers and corporations for outstanding innovations that have contributed to science, technology and the economy in Japan. One of the award criteria is technology that was developed and com-

mercialized by corporations based on original research by universities and research institutions. Kyocera successfully developed ultra-highprecision quartz wafers by combining the unique technology of Kyocera piezoelectric analysis and the plasma CVM technology developed by Dr. Yamamura. From the combination of these unique technologies, Kyocera has realized a photolithographic process with integrated wafer level production. Based on this photolithography technology, Kyocera was able to achieve the world's smallest quartz crystal while still maintaining excellent performance.  $\blacklozenge$

## Universal Instruments Installs Finetech Multipurpose Bonder In its Advanced Process Laboratory

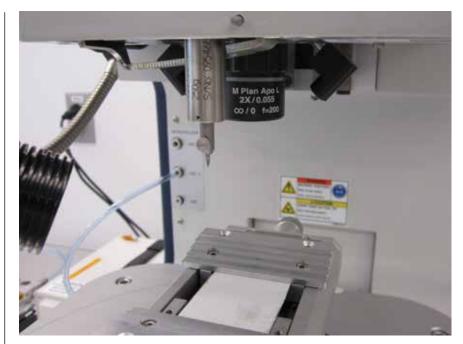

FINETECH AND UNIVERSAL Instruments announce the addition of a FINEPLACER<sup>®</sup> Pico bonding system to the Universal Instruments Advanced Process Laboratory .

The Universal Advanced Process Laboratory (APL) in Conklin, NY, offers comprehensive electronic assembly process research, advanced assembly services and supporting material analyses. It enables OEMs and contract manufacturers to realize rapid product introduction, maximize yield and optimize reliability. The APL has long played an influential role in the electronics community, partnering with industry leaders, engaging academia and executing consortium research to develop new and emerging assembly technologies. The versatile Pico bonder is a great fit for the breadth of the APL mission, provid-

ing a broad range of electronics bonding technologies: thermocompression, thermosonic and ultrasonic bonding, soldering (AuSn, eutectic SnPb, Indium, C4), adhesive technologies, UV curing and mechanical assembly.

The FINEPLACER<sup>®</sup> Pico is a versatile platform used in a wide range of micro assembly applications – such as high accuracy die attach and assembly of components that require a novel bonding approach. It provides a placement accuracy of 5  $\mu$ m, fast, easy process development, and supports bonding forces up to 700 N.

Surface mounted device with delamination (red) along the entire length of several leads. This part would fail per J-STD-020 criteria.

## SonoLab<sup>®</sup> is Your Lab

An ISO/IEC 17025:2005 Certified Testing Lab\* SonoLab, a division of Sonoscan<sup>®</sup>, is the world's largest inspection service specializing in Acoustic Micro Imaging (AMI). Through SonoLab, you'll have access to the superior image quality and reliable data accuracy of Sonoscan C-SAM<sup>®</sup> acoustic microscopes, plus the capabilities and careful analysis of the world's leading AMI experts.

With worldwide locations, unmatched capabilities, extensive experience and the best equipment available, SonoLab gives you the ability, flexibility and capacity you need to meet all your AMI requirements.

#### SonoLab<sup>®</sup> Services

- Component Qualification to Industry Standards

- Materials Characterization and Evaluation

- High-Capacity Screening and Lot Reclamation

- Failure Analysis and Constructional Analysis

- Inspection and Audit Services

- Custom Training

#### To learn more visit sonoscan.com/sonolab

\*For U.S. Locations Only

847-437-6400 • sonoscan.com

Elk Grove Village, IL • Silicon Valley, CA • Phoenix, AZ • England Philippines • Singapore • Shanghai • Taiwan

### NXP Launches World's First Scalable, Single-Chip Secure Vehicle-to-X Platform

NXP SEMICONDUCTORS N.V., THE WORLD'S LARGEST supplier of automotive semiconductor solutions, has expanded its leadership in secure vehicle-to-everything communications (V2X) with its next generation RoadLINK<sup>™</sup> solution. The new NXP SAF5400 is the world's first automotive qualified, high-performance single-chip DSRC modem. Its unique scalable architecture, new industry-leading security features, and leading edge RFC-MOS and software defined radio (SDR) technologies offer OEMs flexible options for cross-regional secure V2X adoption and field upgradeability.

V2X technology allows vehicles to communicate with other cars, infrastructure and vulnerable road users to increase driver safety and smooth out the autonomous driving experience. The DSRC/802.11p version of V2X delivers minimum latency for real-time communication and an operating range that exceeds 1 mile even in areas where cellular network connections are not available. DSRC also provides dedicated secure safety channel operation to enable the secure communication of safety messages and other data in real time, forming an essential part of the suite of autonomous driving sensors for today's connected cars and trucks. V2X based on DSRC is also instrumental in truck platooning, a forerunner of future eco-friendly driving scenarios.

The NXP SAF5400 modem integrates advanced transceiver technology plus the full baseband, MAC and firmware into a complete one-chip standalone modem. It provides superior RF performance for industry-leading range under all channel conditions and is the industry's first single-chip modem with the capability to verify more than 2000 messages per second on chip. The SAF5400 architecture is fully scalable to enable its combination with application processors such as NXP's powerful i.MX family, security, power management and in-vehicle networking solutions, all offered as part of the NXP secure V2X system platform. To enable the highest security, NXP provides the SXF1800, a dedicated hardware secure element based on technology used today in many of the world's most sensitive security environments from electronic passports, banking cards, smartphones and now automobiles.

NXP Semiconductors N.V. enables secure connections and infrastructure for a smarter world, advancing solutions that make lives easier, better and safer. As the world leader in secure connectivity solutions for embedded applications, NXP is driving innovation in the secure connected vehicle, end-to-end security & privacy and smart connected solutions markets. Built on more than 60 years of combined experience and expertise, the company has 31,000 employees in more than 33 countries and posted revenue of \$9.5 billion in 2016. Find out more at www.nxp.com. •

## **Developing new medical devices?**

Start with a **FREE** Promex design review for reliability and manufacturability.

## Unique devices often have equally unique production requirements

Such as not exceeding 85°C during assembly. Handling components that can't be exposed to standard cleaning processes. Providing excellent adhesion between surfaces for fluid processing devices. Controlling voids or bubbles in organics. No matter how unique your requirements, we'll specify the best materials and processes to ensure stable performance.

## Heterogenous assembly and packaging solutions our specialty

We understand the FDA requirements for materials and processes needed to manufacture Class II and Class III devices. Along with providing complete documentation packages. Even if all you have is proof of concept, our engineering and materials experience will get you to assembly of beta units, followed by scaling to high-volume production.

If you're responsible for fast-tracking medical device development, designing microfluidic devices, incorporating more sensors in a smaller package, or assembly in a Class 100 or Class 1000 cleanroom environment:

email RMedina@promex-ind.com or call her at 1.408.496.0222 to ask about your free design review.

promex-ind.com

## **TopLine Rolls Out Graphite Tool for CGA1738 Micro-Coil Spring**

TOPLINE ANNOUNCES A NEW Graphite Tool (patent pending) for precision positioning of 0.4mm diameter Micro-coil springs onto BGA1738 organic substrates as an alternative to conventional solder balls. Micro-coil springs, originally introduced by NASA, provide compliant interconnects between IC packages and the Printed Circuit Board (PCB). The footprint of 1738 packages is 42.5mm x 42.5mm with a pad pitch of 1.0mm. After attaching Micro-coil springs, the reworked package provides more compliancy than BGA (Ball Grid Array) solder balls to absorb stress caused by CTE mismatch, and to increase solder joint reliability under harsh operating conditions.

The TopLine Graphite tool securely locks organic or ceramic LGA substrates in place while Micro-coil springs are attached to the substrate. The procedure is simple: an operator places the LGA inside of the Graphite Tool. Next, a layer of solder paste is printed on the LGA pads using a 125um thick stainless-steel stencil. Afterwards, Micro-coil springs are

dropped in place using TopLine's patented Flip-Pack<sup>®</sup> cassette. After depositing the springs into the graphite, the operator removes the Flip-Pack<sup>®</sup>. The next step is to place the graphite into a vapor-phase reflow oven to form solder fillets that permanently secures the Micro-coil spring to the IC substrate. After cool-down, the CGA is gently removed using an engineered extraction tool.

For more information about the new C7-GRAPHITE-1738M tool set, visit www.topline.tv/CCGA\_Tool.html. ◆

## SHENMAO Introduces New Generation Zero Halogen Lead-Free Solder Paste to solve HoP issues, Improve ICT Testability

#### Prevents Head on Pillow Issue

SHENMAO TECHNOLOGY, INC. introduces New Generation Lead-free Zero Halogen Solder Paste PF606-P245. With superior continuous high-speed printability producing great Solder Paste Print Quality and a wide reflow process window for excellent solderability, it prevents Head on Pillow issues, produces the lowest void and easily fit complicated PCB designs through excellent convergence performance.

SHENMAO PF606-P245 improves ICT testability with flux completely removed from top of solder to prevent contamination of Test Pins during Test operation. Minimal Flux Residue gathers near outside of Solder Joint on the PCB Substrate, a substantial improvement over legacy solder Paste.

For more than 44 years, SHENMAO has been dedicated to produce Solder Products including Water Soluble and No-clean Solder Paste, Laser Solder Paste, Solder Preform, Cored Solder Wire, Wave Solder Bar Alloys, Wave Soldering Fluxes, Extremely Pure Solder Powder up to Type 8, BGA and Micro BGA Solder Sphere, Wafer Level Packaging Solder Paste and Fluxes, LED Die Attach Paste, High Performance Liquid Fluxes, Solder Preform, Solar Ribbon, Plating Anode used in PCB Fabrication, Assembly and Semiconductor Packaging Processes.

SHENMAO Solder Materials are available at affordable cost from 10 worldwide locations. For more information, please contact SHENMAO America at www.shenmao.com Tel: 408-943-1755 e-mail: usa@shenmao.com. ◆

CCGA

Solder columns absorb CTE mismatch between large ceramic arrays and the PCB, making CCGA more reliable than BGA.

## www.CCGA.co

## **Bonding Wire**

Easy to Order

Yes One Spool

(800) 776-9888

Available from TopLine

TanakaWire.com

## FOLLOW UP

## 2017 ECTC – A Global Packaging Conference

*The 67th Annual Electronic, Components and Technology Conference (ECTC) Sponsored by IEEE/CPMT Convened in Lake Buena Vista, FL May 30 – June 2, 2017*

Mark D. Poliks, Binghamton University and Eric Perfecto, GLOBALFOUNDRIES

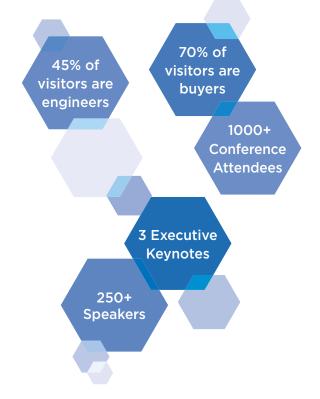

THE 67TH ECTC LIVED UP TO ITS reputation as the premium international event of the microelectronics packaging industry, with 335 papers presented by authors from 22 different countries, in 41 technical sessions spread over three full days. These papers were selected from 576 abstracts submitted for this year's conference. Sessions on fan-out wafer/ panel level packaging and flip-chip packaging were well attended with over 350 people in the audience at times.

These technical sessions were preceded by a full day of 18 Professional Development Courses and three special/ panel sessions on Tuesday. The Tuesday morning Applied Reliability subcommittee special session on "Material and Package Reliability Needs/Challenges for Harsh Environments" opened the ECTC with invited speakers from Boeing Research & Technology, Bosch, Schlumberger, Heraeus, General Electric, and NXP Semiconductors. The afternoon special session on "Flexible Hybrid Electronics - Electronics Outside the Box," a panel of experts from the Air Force Research Laboratory, U.S. Army RDE-COM ARDEC, Boeing, Jabil, and IBM discussed how innovation in thin silicon device integration and packaging will deliver new electronics for medical and asset monitoring. The Tuesday evening ECTC Panel Session on "Panel Fan-Out Manufacturing: Why, When, and How?" included perspectives from global leaders from TSMC, DECA, NANIUM, IZM Fraunhofer, and Qualcomm. All these special sessions drew an audience of over 100 people each, a very good showing for the Tuesday of the conference.

The ECTC Plenary Session on Wednesday evening titled "Packaging for Autonomous Vehicle Electronics," featured key technologists from Georgia

Tech, Texas Instruments, Velodyne, Nvidia, and Qualcomm sharing their views on the evolutionary requirements for packaging and reliability challenges to support widespread implementation of self-driving vehicles on the road. The CPMT seminar on Thursday, "3D Printing Tools, Technologies and Applications," featured speakers from Georgia Tech, Zuken SOZO Center, Nano Dimension, and Fuji Machine Mfg. Over 100 attendees participated even until the late hour of 9:30 PM – a promising sign for a successful 67th ECTC.

General Chair Henning Braunisch of Intel Corporation commented: "We were very pleased to see the 67th ECTC be so highly attended. Building off the incredible success of 2015 in San Diego and 2016 in Las Vegas, we were thrilled to welcome 1,439 attendees this year, our third highest attendance ever. I think this is a clear indication of the importance that packaging and interconnect technologies have in helping the industry to realize more highly functional products and systems. ECTC's main mission has always been to showcase the most up to date technologies and trends in electronic packaging and the wide array of topics that our program committee put together

this year was no exception."

Dr. Braunisch continued: "ECTC truly is a four-day event, kicking off the conference on Tuesday with the Professional Development Courses, three special topic sessions, along with the iNEMI and CPMT Heterogeneous Integration Technology Roadmap meetings. It's gratifying to see so many attendees taking advantage of these. Once again this year, our Technology Corner exhibit area was a tremendous success and all 110 booths - a record number - were sold out. Having so many decision makers and technical professionals at ECTC provides a lot of opportunity for interactions between suppliers and end users. We are very appreciative of all the volunteers. sponsors, presenters, exhibitors, and attendees that helped make ECTC 2017 a great success."

#### Mark Your Calendar for the 68th ECTC

Planning is already underway for the 68th ECTC, which will be held May 29 – June 1, 2018, at the Sheraton San Diego Hotel & Marina, San Diego, California, USA. The first call-for-papers has been issued and abstracts must be received by October 9, 2017. For more information, visit ectc.net. ◆

#### COLUMN

## COUPLING & CROSSTALK

By Ira Feldman

Electronic coupling is the transfer of energy from one circuit or medium to another. Sometimes it is intentional and sometimes not (crosstalk). I hope that this column, by mixing technology and general observations, is thought-provoking and "couples" with your thinking. Most of the time I will stick to technology but occasional crosstalk diversions may deliver a message closer to home.

## "We are **on fire!**"– Good News, Bad News, or Both?

**WHEN A BUSINESS IS SAID TO BE** on fire does strategy go out the window? It is curious that fire or fire-related terms are used to characterize two extreme states of business. A business on fire may think they are like a professional athlete who, when is said to be "on fire", is unstoppable and at the top of their game. The business may have too much of a good thing, i.e.: more orders than they can handle which is a problem in itself. At the other extreme, a business faced with a disaster (actual fire, product safety issues, etc.) quickly goes into "firefighting" mode. In "firefighting mode" the entire organization is consumed with containment, stabilization, and recovery. And a successful recovery will keep the business from heading to a "fire sale".

How to avoid being burned regardless of good news or bad news? Use a solid strategic planning process and follow that plan. Good strategy does not change on a daily basis. Only the tactics to achieve the strategy should be "tuned" in response to the current situation. Significant issues involving insufficient resources and prioritization typically challenge a company on fire. The company exclusively focuses on delivering against commitments to avoid dissatisfied customers and without thought of the future. Production "war room" anyone? As a result, it is too easy to ignore strategy while focusing on execution.

Businesses are tempted to respond similarly when there is a disaster. One

might argue that when an organization is facing a potentially fatal crisis it is appropriate to suspend organizational strategies to focus on improvised shortterm tactics to navigate the crisis. If the business doesn't survive what does next year's plans matter? Better are corporate strategies that contemplate contingencies for crises that may arise. Simply put: you need strategic planning **now** to have a workable strategy for both growth and to avoid tragedies.

Mature and successful companies understand the need for strategic planning and staying focused on their objectives to survive long term. There are "successful" companies that do not plan strategically and it is not simply a confusion between strategy and tactics (the actions that you take to achieve the strategy or other objectives). These companies tend to either have immature management or operate in a transactional manner where success comes from basically doing more of the same (think credit card processing). In the world of high technology, many companies start as or function in a transactional manner like a "job shop." Yes, the technology is complex and the products are sophisticated. With rapid advances of technology and lacking a proper long-term strategy to expand into other markets, many of these businesses enjoy short-term success but don't survive long-term. How many purveyors of floppy diskettes and drives are still in business?

Is strategic planning the province of only the largest companies with armies of strategic planners? No! All it takes is a commitment to create and follow the plan. Even though a company lacks strategic planning as a core discipline, they can implement strategic planning as their management processes mature. Strategic planning can help grow the smallest organization (think sole proprietorship or "mom & pop") operation to a much larger concern. And it will keep a large organization relevant and competitive. The team at Feldman Engineering has worked with organizations of all sizes and business models ("job shops" to multi-national) and quality of management processes (the good, the bad, and the ugly) to deploy strategic planning. After overcoming the initial skepticism and inertia, these organizations realize they can be even more successful with a systematic on-going strategic planning program.

What about companies that are always

in crisis mode cycling from the extremes in industries that have frequent cycles and/ or very deep boom & bust cycles (feast to famine)? The semiconductor supply chain was historically characterized by both and the business cycle was described as "the roller coaster". Companies enjoyed a great year or two during the booms while fearing the inevitable bust that not all companies survived. Hope is definitely **not a strategy**, so the long-term survivors developed strategies that either reduced the cycle or found non-cyclic / countercyclic business to smooth out the peaks and valleys. The strategic companies also completed the consolidation necessary to stabilize their businesses.

Why does strategy get brushed aside and ignored? Is it simply a case of being too busy? Lack of resources? Or is it the result of confusing the urgent with the important? Has management given up their responsibility to manage so they can jump in and be a hero by putting out today's fire? The answer may be a mix of these reasons exacerbated by human nature. What is clear is that management and individuals who allow this to happen do not comprehend the implications of ignoring strategy. Most importantly these are missed opportunities to make progress on strategy. When an organization is too busy with orders - i.e. business is "great" and revenue is at the top end of the scale - they can most afford to implement strategic change. Yes there may be a shortage of resources (manpower and/ or equipment) since "everyone" is busy fulfilling demand. But perhaps the current financial situation permits hiring, renting, or subcontracting to provide the required resources? And when an organization is in crisis mode, making strategic changes - especially to prevent future recurrence of pain – is when the organization may be most motivated to change. In either case the strategy should be established beforehand to allow the proper research and planning to take advantage of the situation and avoid over compensation.

What about strategic planning for startups? Companies started with a strategic vision are more likely to succeed as demonstrated by disruptive innovators like Qualcomm, Nvidia, and others. A company lacking a solid strategic plan will find it extremely difficult to obtain venture capital or other funding. Once the strategy is set, a startup should become laser focused on tactics. Their only role becomes one to discover or develop a new business for their technology by executing a properly-scoped business plan that was designed to support the strategy. If a startup is not successful with their initial target market(s), they can "pivot" to a new market or adjust their business model but their core strategy should remain constant. Long term strategic activities are beyond the scope and funding of a startup. Once the startup has proven itself by demonstrating a functioning product or service with a market of willing customers, the startup team either generates an "exit" (selling via a corporate acquisition or initial public offering) or raises additional funds. At this point the startup needs to transition from focusing only on tactics to regular strategic planning to drive their tactics.

**Operating without a strategic plan** is like sailing without a destination in mind. You may spend a lot of time and energy tacking as a reaction to how the wind is blowing. But without a plan you don't know how to adjust each tack to efficiently arrive at the desired destination. The good news is that any organiza-

tion can be taught how to implement and execute a strategic planning process. We have done this successfully for both high technology and non-technical companies and organizations. With the discipline to execute strategic planning regularly and to not abandon the principles during a crisis, an organization will become better and more efficient at achieving its desired goals.

For more of my thoughts, please see my blog http://hightechbizdev.com.

As always, I look forward to hearing your comments directly. Please contact me to discuss your thoughts or if I can be of any assistance.

IRA FELDMAN is the Principal Consultant of Feldman Engineering Corp. which guides high technology products and services from concept to high volume manufacturing. He engages on a wide range of projects including technical marketing, product-generation processes, supply-chain management, and business development. (*ira@feldmanengineering.com*)

#### INFO@NAMICS-USA.COM 2 (408) 516 4611

**DAM & FILL ENCAPSULANTS**

Trust in the unmatched protection, reliability & convenience of our CHIPCOAT globtops

Amtech MICROELECTRONICS. INC.

**Advanced Microelectronics Manufacturing**

#### SMT ASSEMBLY (RoHS/Non-RoHS)

#### DIE ATTACH and FLIP CHIP DATACON 2200 EVO Plus.

- Die-Attach, Flip-Chip and Multi-Chip.

MICROELECTRONICS (Cleanroom)

#### **WIRE BONDING**

- KNS Ultra Fine Pitch Ball Bonders.

- **HESSE Fine Pitch Wedge Bonders.**

- ASYMTEK Precision Dispense.

- Glob Top, Dam & Fill, Underfill, UV.

#### BOND TEST and METROLOGY

- DAGE Wire Bond Pull & Die Shear Test.

- MICRO-VU Precision Measuring System.

#### **PROTOTYPE to PRODUCTION**

- SMT ASSEMBLY with YAMAHA Automation.

- 01005, BTC, BGA, uBGA, CSP, Flip Chip.

#### NEW PRODUCT INTRODUCTION (NPI)

- Complex Microelectronic Assemblies.

- PCB, Rigid-Flex and Flex substrates.

#### PROCESS DEVELOPMENT

- SMT, Flip Chip, Die Attach, Wire Bonding.

- R&D, Process Engineering on-site.

#### OUAL ITY

- YESTECH Automated Optical Inspection.

- YXLON-FeinFocus 160 kV XRAY System.

www.amtechmicro.com | (408) 612-8888 | info@amtechmicro.com

#### COLUMN

## INDUSTRY INSIGHTS

By Ron Jones

## Planning for Success

THE SEMICONDUCTOR INDUSTRY is chock full of people with educational backgrounds in engineering and the sciences. They design IC's from relatively simple power management circuits to microprocessors with billions of transistors. They develop fab processes at 7 nm and design packages that can dissipate huge amounts of power while protecting a fragile chip. They do sales, marketing and business development because they understand the technical nuances of the products. It is typically the case that these employees rise through the ranks to lead their companies as executives and CEO's. The importance of these people cannot be overstated.

There is another class of semiconductor professionals that typically have much different beginnings. They usually have a 4 year non-technical degree, while some have a 2 year degree or a high school diploma. They often have backgrounds in business administration or liberal arts. If they do have a technical background, it will likely be in industrial engineering. They may have started in the industry as a purchasing agent or a manufacturing supervisor.

I lump these into a category of <u>plan-</u><u>ning and supply chain management</u><u>professionals</u>. They draw inputs from throughout the company as well as from the supplier base and the customer base. These people are often the unsung heroes that make the monthly revenue numbers happen and keep the customer base satisfied.

As an engineer, I didn't have an appreciation for the role that planners played. As I progressed into general management and took on P&L responsibility, their value became obvious. A good planner was worth his or her weight in gold; making sure there were minimal revenue hiccups and customer delivery surprises.

At a seminar at Crosby Quality College in the early 80's, I was introduced to the concept of Ballet vs. Hockey. In

ballet, the drop of the conductor's baton starts a progression of music and movements that are essentially the same with every performance. With hockey, the drop of the puck starts a sequence of unpredictable events that is different each time the game is played.

The life of a planner doesn't fit either model, but is somewhere in between. They live in a world that changes every day. At the beginning of a new production period, there is a plan in place. It includes a sales forecast for customer demand, work in process inventory, commitments from manufacturing partners on capacity, schedules from direct materials suppliers on piece parts, etc.

A good planner was worth his or her weight in gold; making sure there were minimal revenue hiccups and customer delivery surprises.

Then the month actually starts and unplanned events begin to occur:

- A customer wants to change priorities or get an upside

- A fab lot gets put on hold due to out of limit PCM or probe data

- Lots mysteriously drop off or reappear on the daily WIP report

- A fab or assembly lot is scrapped for a yield or reliability issue

- An assembly lot can't be launched because there are no BGA substrates

- A package delamination problem puts all 8 lead SOIC devices on reliability hold

- And an infinite number of other possibilities involving customer demand, inventory errors, weather, machine downtime, power or labor outages, yield, capacity, quality, reliability,

direct materials, die availability. . . and the beat goes on.

Things seldom go completely as planned. If a situation arises that may impact a committed delivery, the planner must identify and highlight the problem as early as possibly to maximize the opportunity to have it corrected. The planner must also notify the customer as soon as possible to allow him or her to make plans to minimize the impact. On time delivery is one of the major factors in customer satisfaction and loyalty and the planner has prime responsibility for making it happen. A line down situation can have a negative financial impact to the customer that is hundreds of times the cost of the parts that caused it.

There are various customer profiles, each with a different set of parameters. Some customers order standard off-theshelf parts (build to stock) and others have custom products (build to order). Some customers take delivery directly or have their products shipped to EMS providers like Flextronics. Some buy parts through distribution (which triggers ship/ debit transactions) and some have the supplier hold inventory in their factory and pay for product as needed. All these are part of the calculus of planning the supply chain.

There are supply chain management software applications that can help manage the myriad details. These are only as accurate and timely as the data that is fed into them. It must be a closed loop to ensure that the system reflects what actually happened.

The responsibilities of planning and supply chain management professionals go far beyond the examples I have listed. They touch most functions inside the company including engineering, production, purchasing, sales, customer service and accounting. They interface with the manufacturing partners and with the customer base. They bring together all these efforts to ensure revenues are met and customers are satisfied. If things are running smoothly . . . hug a planner.  $\blacklozenge$

RON JONES is CEO of N-Able Group International; a semiconductor focused consulting and recruiting company. N-Able Group also utilizes deep semi supply chain knowledge to provide Conflict Mineral Compliance support services to companies throughout the semiconductor supply chain. Email ron.jones@n-ablegroup.com.

# **MEPTEC 2017**

HOSTED BY

30.2017

HETEROGENOUS INTEGRATION - THE ROAD TO IMPLEMENTATION

## NOV. 30, 2017 | SEMI GLOBAL HEADQUARTERS | MILPITAS, CA SYMPOSIUM 8:00AM - 5:00PM | EXHIBITS 9:30AM - 6:30PM | RECEPTION 5:00PM - 6:30PM

s the growing need to integrate disparate semiconductor technologies in a cost effective way with rapid cycle time and the driving demands of our increasingly connected world, we find many key hurdles in mainstreaming heterogeneous technology packaging solutions. In

01010

#### **KEYNOTE SPEAKER**

#### Wilmer R. Bottoms, Ph.D.

Chairman, Third Millennium Test Solutions Co-chair, Heterogeneous Integration Roadmap

010101010

GOLD SPONSOR

#### **KEYNOTE SPEAKER**

David Armstrong Director of Business Development Advantes particular, this event will explore three issues central to the successful execution of heterogeneous integrated packages:

- Can the packaging community establish a real design for heterogeneous integration ecosystem?

- Should we rethink the reliability standards for these heterogeneous integrated SIP packages?

- What are the best test strategies for these heterogeneous integrations, or at least what are the guiding principles?

The program will include three keynote presentations from industry experts outlining these three issues in more detail, each followed by an interactive panel discussion on these same topics. The panels will be populated with industry experts with diverse and perhaps conflicting views on these important topics.

Be sure to join for what promises to be an exciting and educational day as we debate the issues central to successful heterogeneous integration implementation!

Sponsorship Opportunities and Exhibit Spaces Available

Third Keynote to be Announced

**REGISTER ONLINE TODAY AT WWW.MEPTEC.ORG**

## ANALYSIS

# Where is the Semiconductor Manufacturing Sweet Spot?

Rick Vogelei, Business Development Semico Research Corporation

WHERE IS THE SEMICONDUCTOR manufacturing sweet spot? Two recent Semico Research Corp. studies provide the information to not only determine the overall sweet spot but to dig even further to find which products and technologies are the driving forces behind the growth or decline.

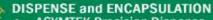

Chart 1 was developed from data in the fab database study. It shows the number of fabs operating and planned by wafer size.

Surprisingly, there are still almost 300 fabs operating at 150mm or smaller. Many manufacture trailing edge devices, especially discretes, while others manufacture relatively new devices, including analog, power, MEMS and LED devices. These semiconductors are not leadingedge devices, but they are essential to many electronics industry end-use products. The die size for many is quite small, and they do not scale well to smaller geometries. Many may continue to be manufactured in 150mm fabs for the immediate future. Others will undoubtedly migrate to 200mm fabs.

In 2017, there are over 190 fabs manufacturing devices on 200mm wafers. Many are producing MOS Logic semiconductors, but there is a sprinkling of 200mm fabs producing a wide variety of other semiconductor product types including analog semiconductors, MEMS devices, power semiconductors, and SRAM. Ten more 200mm fabs are planned, with one under construction.

There are more than 150 300mm fabs operating or under construction in 2017. These fabs are focused on high-volume devices manufactured at leading-edge technology nodes, including MPUs, DRAM, and NAND Flash. Following the usual pattern, many semiconductor product types will migrate from 200mm to 300mm fabs. Almost 30 additional 300mm fabs are planned.

Chart 1. Number of Fabs, Operating and Planned, by Wafer Size

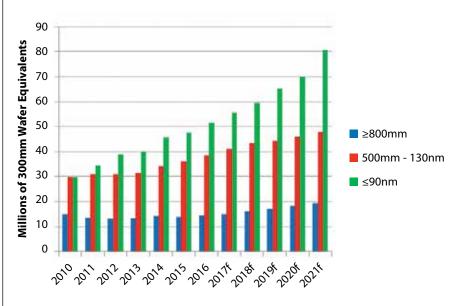

Chart 2. Wafer Demand by Technology Node

Source: Semico Research Corp.

Chart 2 developed from data in the wafer demand study, shows wafer demand by technology node.

The first category, greater than or equal to 800nm, was chosen because it represents most manufacturing in 150mm or smaller fabs. The second category, 500nm through 130nm, was chosen because it represents most manufacturing in 200mm fabs. The CAGR for 2016 through 2021 for this category is 4.6%. Most 300mm fabs are at technology nodes beyond 100nm, the third category. The CAGR for 2016 through 2021 for this category is 9.3%.

So, where is the semiconductor manufacturing sweet spot? It depends. The sweet spot for new fabs is 300mm. The sweet spot for wafer demand is 300mm wafers. However, there continues to be significant demand for 200mm capacity for MEMS and Sensors, microcontrollers, analog, etc. A variety of factors are impacting the sweet spot. Material costs are increasing, specifically silicon wafers. If the price of 300mm wafers increases faster than 200mm wafers, the shift to 300mm production will be slower than expected. The challenge for 200mm wafers is the concern over availability and cost of 200mm equipment. The continued operation of 40+ years old 200mm fabs is becoming more challenging as equipment and maintenance become scarcer and more expensive. Will the cost associated with 300mm production finally push 450mm wafer development forward? Wherever your sweet spot is, Semico's fab database and wafer demand studies have the data to help you find it. These studies are:

- Semico Fab Database: Update Summary, First Half 2017

- Semico Wafer Demand: Q2 2017 Highlights

Contact Rick Vogelei at rickv@semico. com for more information. ◆

## MEPTEC 2017 SEMICONDUCTOR PACKAGING SYMPOSIUM HETEROGENOUS

INTEGRATION: THE ROAD TO IMPLEMENTATION 11.30.2017

SAN JOSE, CA

### May 29 - June 1, 2018 Sheraton San Diego Hotel and Marina San Diego, California, USA

As the premier event in the semiconductor packaging industry, ECTC addresses new developments, trends and applications for fan-out & fan-in packages, 3D & 2.5D integration, TSV, WLP, flip-chip, photonics, LEDs, materials and other integrated systems packaging topics.

Abstract submissions and Professional Development Course proposals for the 68th ECTC are due by **October 9, 2017**.

## Call for Papers Opens August 8!

We welcome previously unpublished, non-commercial abstracts in areas including, but not limited to:

Advanced Packaging Applied Reliability Assembly & Manufacturing Technology Emerging Technologies High-Speed, Wireless & Components Interconnections Materials & Processing Optoelectronics Thermal/Mechanical Simulation & Characterization

## TECHNOLOGY

# Heterogeneous Integration Roadmap – The First Year

*Wilmer R. Bottoms, Ph.D., Chairman, Third Millennium Test Solutions Co-chair, Heterogeneous Integration Roadmap (HIR)*

#### Introduction

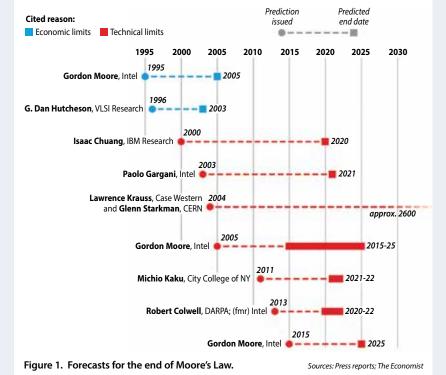

WE HAVE HEARD FOR DECADES THAT the end of Moore's Law was near but for more than 50 years the observation that the number of transistors in a dense integrated circuit doubles approximately every two years continued. Forecasts of the end of CMOS scaling started with Gordon Moore's response to a question in 1965 of how long the observation would continue. His response was maybe 10 years. Figure 1 shows some predictions made for the end of Moore's law made since 1995.

The Economist identified, in a March 2016 article, forecasts driven by technical limits and some by economic limits. Most were based on the technical limits. After 2012 the rate of scaling began to slow and the advantages were decreasing. The historical scaling advantages of increasing performance, reduction in power, reduction in size and reduction in cost were not maintained.

#### A Brief History

THE INTERNATIONAL TECHNOLOGY Roadmap for Semiconductors (ITRS) had it's beginning as the National Technology Roadmap for Semiconductors (NTRS) in 1991 sponsored by the Semiconductor Industry Association in the United States. The first edition was published in 1992. The name was changed to ITRS when the World Semiconductor Council was established in 1998 and the major centers of electronics at the time in Europe, Japan, Taiwan and Korea joined the US SIA as sponsors. The primary driver of progress was CMOS scaling and the ITRS identified difficult challenges and

potential solutions. Their work enabled pre-competitive collaboration addressing these problems before they slowed the pace of progress. The increasing cost and decreasing rate of performance improvement was significantly slowed after 2010 and, on a per transistor basis the cost of a transistor has been increasing with each shrink since 2012. It was clear that the economic end of Moore's Law was approaching. By 2014 it was known that a Roadmap with a new focus was needed to maintain the pace of progress. The Heterogeneous Focus team of the ITRS took the initiative and signed an MOU with the IEEE CPMT Society

in early 2015. This agreement formalized on-going collaboration in support of roadmapping for Heterogeneous Integration (HI). The CPMT Society formally initiated the Heterogeneous Integration Roadmap (HIR) in March of 2016 to provide the institutional sponsorship essential to ensure quality and continuity for any sustainable roadmap activity. The HIR has accomplished a great deal in the first year and this article reports on that progress.

#### What Do We Mean By Heterogeneous Integration?

The declining benefits of scaling

#### **Heterogeneous System Integration**

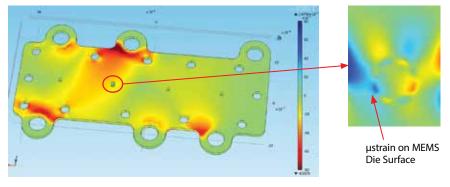

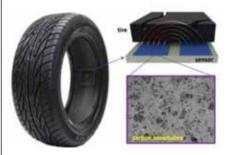

Figure 2. An example of HI with diverse materials, device types and integration architectures in a 3D-SiP.

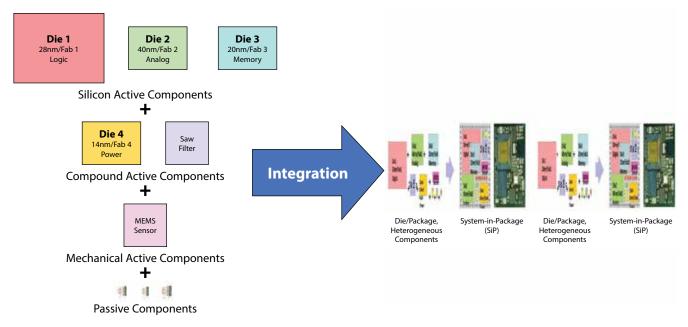

CMOS demanded an expanded approach to technologies that could maintain Moore's Law pace of progress that drove growth the price elastic growth in electronics. The "low hanging fruit" for the expanded approach is HI. It is defined as:

"Heterogeneous Integration refers to the integration of separately manufactured components into a higher-level assembly such as System-in-Package (SiP), that, in the aggregate, provides enhanced functionality and improved operating characteristics."

#### (from the final edition of ITRS)

Heterogeneous integration will incorporate continued scaling where it adds value and integrate new component types with new approaches to system integration providing enhanced functionality at lower cost. This includes heterogeneity by material type, process node for silicon memory and logic, device type and new integration architectures. This is illustrated in Figure 2.

#### **Progress Our First Year**

The activity in 2016 was focused on developing governance, expanding sponsorship and engaging industry, academia, government and research institutes as active participants in the HIR.

#### Governance

The initial sponsorship by the IEEE CPMT society was intended to establish a base with a global institution having a local presence in every region with significant development activity in the electronics industry, a respected peer review processes for quality control and an existing schedule of conferences in Asia, Europe and the United States providing venues for face-to-face meetings in each region. This initial base with IEEE CPMT Society was rapidly expanded and today there are 5 institutional sponsors:

- IEEE Electronic Packaging Society (Formerly the CPMT Society)

- IEEE Electron Devices Society (EDS)

- IEEE Photonics Society

- SEMI

- ASME Electronic and Photonic

Packaging Division

Each sponsor appoints a member to the HIR International Roadmap Committee (IRC) which is the executive Board that manages the preparation and publication of the HIR. The IRC defines the number and focus of the Technical Working Groups (TWGs) and appoints the Chair persons for each TWG.

HIR has established a Global Advisory Council currently composed of three members. The purpose of the Council is to guide the IRC with a long-term industry vision, support HIR Outreach with Industry visionaries and leaders and advise the HIR on the value proposition for stakeholders in industry, commerce, academia and government.

The number of sponsors will increase, additional members will be appointed to the Global Advisory Council and both the number and focus of the TWGs will be adjusted as the penetration of electronics into every aspect of our lives continues.

#### **Technical Working Groups Today**

HIR began the year with a smaller number of TWGs than we have today and it was reviewed in our workshops. The list was adjusted as we learned of other needs in our face-to-face meetings. The number was expanded and the focus revised to incorporate the learning from these meetings. Today there are 22 TWGs organized into 5 groups. Each TWG listed below is preparing a Chapter for the 2017 Edition of the HIR focused on system level heterogeneous Integration.

## TECHNOLOGY

#### **Technical Working Groups**

## Heterogeneous Integration of Components

- Single Chip and Multi Chip Packaging (including Substrates)

- Integrated Photonics

- Integrated Power Devices

- MEMS and Sensors

- RF and Analog Mixed Signal

#### **Cross Cutting Topics**

- Materials and Emerging Research Materials

- Emerging Research Devices

- Interconnect

- Test

- Supply Chain

#### **Integration Processes**

- System in Package (SiP)

- 3D +2.5D

- Wafer Level Packaging including fan in and fan out (including panel processing)

#### Heterogeneous Integration for Specialized Applications

- Smart Mobile Devices Smart Phone

- High Performance Computing

- IoT and Wearable

- Medical and Health

- Automotive

- Aerospace and Defense

#### **Design Methodology and Tools**

• Co-Design and Modeling and Simulation

Aerospace and Defense was added due to input from our face-to-face workshops during the year. Industry and government groups asked for this addition and contributed professionals to work on preparing the Chapter.

Design methodology and tools has 2 subgroups; one focused on co-design issues unique to HI and a second focused on modeling and simulation. In a world largely consumer driven the historical path to produce a high-volume system level product is no longer viable. It involved building and characterizing prototypes, modifying the design to incorporate learning from characterization and

Figure 3. HIR Workshop Tokyo, Japan, August 9, 2016. (110 participants)

Figure 4. HIR Workshop, Hsinchu, Taiwan, August 11, 2017. (102 participants)

repeating this cycle until a product meeting the design specification with economic yield was achieved. This process imposes unacceptable design cost and time to market. Resolving this "difficult challenge" requires conducting design verification experiments in the computer without going to the factory.

Integrated photonics addresses both photonics and plasmonics with focus on increasing the physical density of bandwidth and decreasing time and energy associated with massive data traffic. The explosive growth in data traffic is projected to continue as logic, memory and applications migrate to the Cloud.

We believe HIR is the first industry wide effort to include a roadmap for the supply chain. This was suggested by participants in or face-to-face meetings from some of the largest companies in the world. It is clear that the supply chain of tomorrow will be very different from what we use today as robotics, massive sensor arrays and artificial intelligence take over the task of optimizing the supply chain and the factories they supply.

#### **Global Outreach**

The NTRS renamed to ITRS in 1998 recognized the silicon IC business as a global activity. It is much more so today with sources for materials, equipment and processing technologies distributed around the world. HIR sponsoring institutions have membership across the globe and hold technical conferences in venues around the world providing increased outreach for our Roadmap and local venues for face-to-face meeting at their conferences. We took full advantage of this during our first year and the result was a total of 947 cumulative participants in our workshops.

## There were 15 Face-to-Face Workshops in 2016

- 1. ECTC + ITHERM Las Vegas, NV USA 05/31- 06/04

- Palo Alto Workshop before SEMICON WEST, July 10, 2016

- 3. SEMICON WEST San Francisco, CA USA, July 11, 2016