#### QUARTER TWO 2004

A Publication of The MicroElectronics Packaging & Test Engineering Council

**INDUSTRY NEWS**

**ENTEGRIS, INC.** has announced that **IC INTERCONNECT (ICI)** has joined the Entegris Final Manufacturing Partner program. *page 14*

**STATS** and **CHIPPAC** have announced the signing of a definitive agreement for the companies to merge. *page 17*

**KULICKE & SOFFA** and **ASE GROUP** announce a strategic relationship between K&S's Test Products Group and ASE Test Limited. *page 18*

#### **TECHNOLOGY**

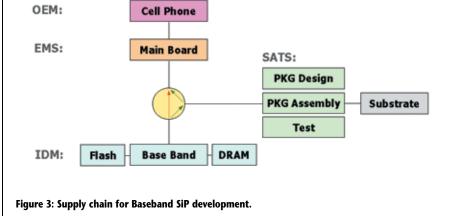

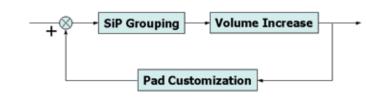

**Dr. Young Gon Kim** of **Tessera** reviews five infrastructure barriers to SiP development for achieving time-to-market goals, and possible solutions to overcoming those barriers in *"Solving SiP Time-to-Market Challenges"*. page 24

**Robert Rowland** of **RadiSys Corporation** discusses components from a process engineer's perspective. *page 28*

Kelly Linden and some of his colleagues from Microvision discuss "Wafer Scale Vacuum Packaging of a MEMS Optical Scanner". page 30

North America's largest exposition devoted to semiconductor equipment, materials, services, and technology returns to San Francisco and San Jose. page 40

# Wafer Level Packaging Interconnects:

Wafer Fabrication vs. Package Assembly

One Day Technical Symposium and Exhibits Coming to Santa Clara August 19th ... page 5

#### MEMBER COMPANY PROFILE

Born from the decision of National Semi-

conductor to reduce its offshore factory

base in the early 90's, **NSEB** was purchased by local Thai investors in 1993. It is now completely independent of National. Tak-

ing advantage of the core competence in IC assembly and test, the new management

team has developed NSEB into what may be the single best medium size IC assem-

bly/test house in the Far East. During the

last 4 or 5 years they have been ranked as

one of the top 5 or 6 subcons. page 20

ong considered one of the best kept secrets in the subcon world, NS Electronics Bangkok has developed a strong reputation for high quality, short cycle times, and excellent customer service. These attributes are the core of an overall strategy by NSEB management to create a superior subcon experience for major semiconductor manufacturers worldwide.

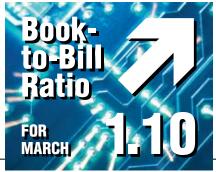

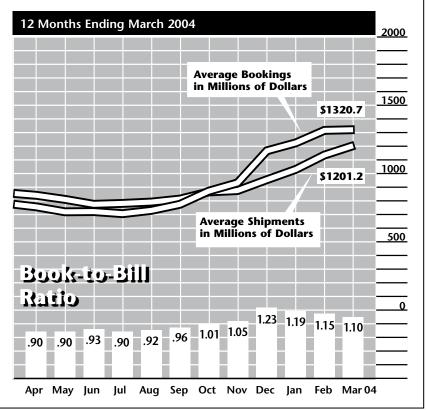

Semiconductor equipment bookings increase 70% over March 2003 level. *page 18*

#### METALS = CHEMICALS = DIELECTRICS PACKAGING = OPTOELECTRONICS

# Putting the Pieces Together

#### Providing the Most Complete Solutions for Your Interconnect Packaging Challenges...

Honeywell is established as a prime supplier in electrical and thermal interconnect products used in the manufacture of high performance BGA and flipchip packages. Our capabilities include design, prototyping, specialized fabrication, metal finishing and high volume manufacturing.

#### **Electrical Interconnect: Evaporation & Power Products**

Honeywell's core competencies include manufacture of the high-purity evaporation charges and electroplating anode products that are used for back metallization, underbump metallization and wafer bumping of flipchip die. We offer a comprehensive material set for the manufacture of high power devices.

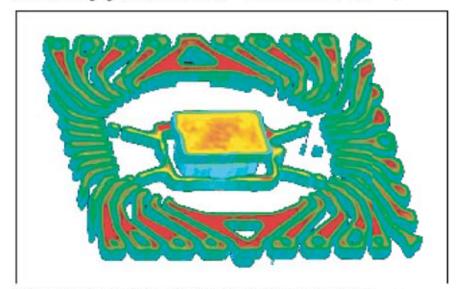

#### Thermal Management: Spreaders, Lids & Stiffeners

Honeywell provides a wide range of thermal heat spreaders, heat slugs and stiffeners used to overcome today's thermal management challenges. We specialize in providing novel thermal solutions for applications requiring the highest performance and tightest tolerances.

#### **Thermal Management: Thermal Interface–Phase Change Materials**

Our packaging science expertise allows us to address thermal management concerns at various levels within both die-to-package and package-to-system assemblies. Honeywell's PCM45 Series materials exhibit excellent surface wetting characteristics resulting in low contact resistance, but do not degrade with use.

#### Putting Together Added Value-

#### Combo-Spreader<sup>™</sup> with Pre-attached Phase Change Material

Available only from Honeywell, the Combo-Spreader is an innovative solution for today's advanced thermal challenges. By combining the benchmark thermal performance of PCM45 with our industry leading thermal spreaders, we provide a lasting solution well ahead of the ITRS roadmap, with fewer production steps required.

Our expertise in materials science, metallurgy and chemistry enables Honeywell to provide solutions to your interconnect packaging needs at a reduced cost of ownership...from layer one to package done.<sup>w</sup>

www.electronicmaterials.com 408-962-2055

#### 2004 Honeywell International Inc. All rights reserved. Combo-Spreader and "From Layer One to Package Done" are trademarks of Honeywell International Inc.

#### **ELECTRONIC MATERIALS**

#### Volume 8, Number 2 A Publication of The MicroElectronics Packaging & Test Engineering Council

801 W. El Camino Real, No. 258 Mountain View, CA 94040 Tel: (650) 988-7125 Eay: (650) 062 8684

Fax: (650) 962-8684 Email: info@meptec.org Published By

MEPCOM Editor

Bette Cooper Design and Production Gary Brown Advertising Mica Jones Marketing

#### **MEPTEC Advisory Board**

Phil Marcoux MEPTEC Executive Director

Seth Alavi

John Bubello Advanced Packaging Magazine Joel Camarda

Kullike & Soffa Gary Catlin Mulichip Assembly

Rob Cole FICO America

John Crane J. H. Crane & Associates

Jeffery C. Demmin Tessera

Mark DiOrio MTBSolutions, Inc

Bruce Euzent Altera Corporation

Skip Fehr Chip Greely

Anna Gualtieri SPEL

Bance Hom Consultech International, Inc.

Ron Jones N-Able Group International

Pat Kennedy GEL-PAK

Nick Leonardi Dynaloy, Inc.

Abhay Maheshwari Xilinx

Mary Olsson Dataquest Marc Papageorge

Doug Pecchenino Ray Petit Pacific Rim Technology

Jerry Secrest Secrest Research

#### Jim Walker Dataquest

Russ Winslow Six Sigma

Bob Hilton 1945 – 2003

MEPTEC Report Vol. 8, No. 2. Published quarterly by MEPCOM, 801 W. El Camino Real, Mountain View, CA 94040. Copyright 2004 by MEPTEC/MEPCOM. All rights reserved. Materials may not be reproduced in whole or in part without written permission.

MEPTEC Report is sent without charge to members of MEPTEC. For non-members, yearly subscriptions are available for \$75 in the United States, \$80US in Canada and Mexico, and \$95US elsewhere.

For advertising rates and information contact Mica Jones, Advertising Sales at (925) 846-0115, Fax (925) 846-0266. t's that time again, *SEMICON West*, when thousands converge on San Francisco and San Jose to see the latest and greatest technology in the semiconductor industry. In this column last year the question arose about how a big event like SEMICON West would fare in face of the many challenges our industry was facing such as the economic downturn, continued travel restrictions and concerns, and SARS. We're pleased to see that in the year since then, things have improved dramatically. We like to think that the worst is behind, and the best is yet to come.

Also in this column last year we talked about MEPTEC's success with our quarterly technical symposiums, and we're pleased to report that the success is continuing. Since July of last year we held an event in August 2003 on "Where the Component Meets the Board: Package Reliability Issues and Challenges"; in November we looked at "Packaging Industry Roadmaps: Overcoming Obstacles and Navigating Solutions"; in February it was "SiPs or SoCs? The Multi Million Dollar Question"; and in May we covered "MEMS and Wafer Level Packaging: Converging Technologies". Our next event will be on August 19, 2004 on "Wafer Level Packaging Interconnects: Wafer Fabrication vs. Package Assembly" (see page 5 for registration information). In addition, we added a new event - this time a non-technical, financial-oriented conference called "Interconnections Investors Conference". The five MEPTEC events since July of last year drew over 1,000 attendees. We're pleased to be able to continue to bring these excellent programs to the professional community. For summaries and updates on a few of these events check out our MEPTEC Events Follow-up section starting on page 6.

Our feature articles and even our editorial this issue reflect some of the topics from our events over the last year. Starting chronologically, we have a contribution from one of our presenters from our August 2003 "Where the Components Meets the Board" symposium, Robert Rowland of RadiSys Corporation. Rob discusses components from a process engineer's perspective. See his article on page 28.

Next we take a look at "Solving SiP Time-to-Market Challenges" (see page 24) that grew out of our "SiPs or SoCs" event, from Dr. Young Gon Kim of Tessera. Dr. Kim reviews five infrastructure barriers to SiP development for achieving time-to-market goals, and possible solutions to overcoming those barriers. He concludes by predicting "the SiP solution has a high potential and will impact the semiconductor significantly in the next

#### **Issue Highlights**

| page 4       |

|--------------|

| page 6       |

| page 11      |

| page 14      |

| page 20      |

|              |

| t<br>page 24 |

| page 28      |

| nggo 20      |

| page 30      |

| page 41      |

| page 42      |

|              |

## **MEPTEC Council Update**

# **From The Director**

# The Interconnections Investors Conference was a success!

n May 12, eighty-five attendees and speakers gathered to discuss the financial outlook for the semiconductor assembly and test services industry, or SATS companies.

The SATS Companies, also known as the "Backend Packagers and Testers", currently are the fastest growing in the semiconductor industry. Yet SATS companies have very little investor visibility, much as the EMS companies had in the early 1990's. Material, IP, and other semiconductor interconnection companies are enjoying equally strong growth and market demand.

MEPTEC's Executive Level Members and some key industry analysts want to help change this financial situation. As the SATS and other semiconductor interconnection companies are pressured to start expanding and looking for expansion money, they to want their financial picture to change.

The goal of this Conference was to as-semble several informative speakers and high market potential companies. Our speakers were leading industry analysts, publicly traded and late stage established SATS and Interconnection Companies. I would like to extend a thank you to the Showcase Presenter Companies at this inaugural event – ASAT, STATS, Chip-Pac, PSI Technologies, Ultratera, UTAC, Am-kor and ASE. I especially commend them for their adherence to our challenge of only ten minutes to present their corporate story.

The financial analysts were topnotch. Jim Walker, a VP of Gartner-Dataquest and one of the inspirations for this event provided an in-depth review of the market drivers for the SATS industry. Charles DiLisio of D-Side Advisors who discussed the value opportunity for SATS followed him.

Lucas Ward recently joined one of our IIC sponsors, WR Hambrecht + Co, leaving a comfortable family life in Italy. Lucas provided a broader view of some of the larger trends occurring in the semiconductor industry that will affect our portion.

I'm very appreciative of Eric Gomberg's time and presentation. Eric traveled from NY, specifically Wall Street. Eric, Senior Analyst with Thomas Weisel Partners, is one of the first analysts to cover our area, and he coined the term SATS. Eric provided an historical perspective and its potential for growth.

Our keynote speaker, Satya Chillara, is a former MEPTEC member and has successfully made the jump from the technical to the financial. He recently joined RBC Capital, an IIC sponsor and a large investment-banking firm that, along with the firms of our other analysts, were responsible for a significant amount of the greater than ten fold market value increase of the EMS companies.

Several event sponsors supported this conference. I would like to thank them for helping make this event successful and pleasurable. Our 2004 IIC sponsors included Dow Chemical, RBC Capital Markets, W R Hambrecht + Co, Gartner-Dataquest, KMZ Rosenman, and Advanced Packaging and SMT Magazines.

I want to particularly thank several people who put forth significant effort for this event. Thank you to Kim Barber, MEPTEC Executive Level Event Manager; Marc Papageorge of SOS and Charles DiLisio of D-Side Advisors, members of the IIC Advisory Board; Doug Molitor and Steve Begley who helped prepare our Showcase Presenters; and Jim Walker of Gartner-Dataquest who prompted the original concept. I also want to extend a thank you to Hans Sevierns. Hans was a very forceful supporter of this event right up to his passing in February of this year.

4

•

Phil Marcoux Executive Director MEPTEC

#### continued from page 3

five years".

Our third contribution is from Kelly Linden and some of his colleagues from Microvision from our "MEMS and Wafer Level Packaging" symposium on "Wafer Scale Vac-uum Packaging of a MEMS Optical Scanner" (see page 30). The packaging of MEMS (micro-electrome-chanical systems) is, in their words, "a critical challenge in creating a technically and commercially viable device". Microvision's work on wafer scale vacuum packages shows it is definitely a feasible technology.

Our editorial this issue is a contribution from one of our session leaders at our "SiPs or SoCs" symposium, and MEPTEC member, Mark Hartung of Chip Supply, Inc. with "Everybody's talking 'bout the new sound, funny, but it's still rock and roll to me..." (see page 42). His reference to singer/songwriter Billy Joel's hit from the 80s is a good analogy to explain the debate about multi-die packaging. It's an interesting take on what Mark calls "déjà vu all over again"!

We're pleased to highlight in our Member Company Profile this issue NS Electronics Bangkok, a longtime Corporate member of MEPTEC. As they state, they are "long considered one of the best kept secrets in the subcon world". They point out that a very important factor of their success lies in one of their most important assets, their employees. Their high quality in all facets of their operations, from their people to their equipment to their customer service, truly makes them a winner. See their story on page 20.

Our University News section this issue introduces the University of Maryland and its Nanoelectronics Research Group. They're doing some fascinating and ground-breaking technology there with their research on semiconductor carbon nanotubes that have been found to have the highest mobility of any known material at room temperature. This re-search could effectively revolutionize the semiconductor materials in-dustry. See their story on page 11.

We'd like to thank all of our contributors for making this a great issue. If you're reading our publication for the first time at the SEMICON West show we hope you enjoy it.

# MEPTECPresents

MicroElectronics Packaging and Test Engineering Council

#### ONE-DAY TECHNICAL SYMPOSIUM & EXHIBITS A

#### REGISTER NOWH

To register by phone, or for more information about this and other **MEPTEC** events, contact Bette Cooper at 650-988-7125, email bcooper@meptec.org or visit the MEPTEC website.

Ask Us About **Exhibiting at This** Event

August 19, 2004 • The Westin Santa Clara, Santa Clara, CA • 8:30 a.m. - 5:00 p.m. Table Top Exhibits 11:00 a.m. - 7:00 p.m. • Reception 5:00 p.m. - 7:00 p.m.

# Wafer Level Packaging **Interconnects**: Wafer Fabrication vs. Package Assembly

n the quest for smaller size, increased performance and lower cost, the semiconductor industry is rapidly migrating towards a "packageless" package, commonly referred to as Wafer Level Pack-aging (WLP). Markets that require small form factor, such as hand held and portable devices, are seen as the volume drivers for WLP, but WLP should expand to other applications as the technologies are developed. By definition, WLP consists of interconnections made at the wafer level. With WLP typically vielding the highest cost vs. performance advantage for interconnection of devices to substrate materials, the potential efficiencies gained in the WLP testing are seen as a bonus to utilization of these technologies. The question is not whether WLP will continue to build upon its current momentum in the industry; that is a given. Rather, where will it be done? Is WLP a part of wafer fabrication or a package assembly? The answer de-pends on the specific WLP technology chosen since some manufacturing processes can be easily streamlined into the wafer fabrication process while others may be more effectively done as part of assembly.

During the two years since the previous MEPTEC conference on WLP, development and implementation of WLP has continued and current industry growth is adding momentum to the area of WLP manufacturing, making another symposium very timely. The objective of this conference is to address WLP technologies and convergence of wafer fabrication and package assembly. This will be a fast-moving,

International

solutions-oriented event with session topics being covered in brief presentations by experts, followed by interactive question and an-swer panel sessions. Invited speakers at this focused symposium will share their wealth of knowledge in various areas of WLP technology. This symposium is a must for all the executives, managers, engineers and other decision makers who wish to improve the cost / performance of their products and have the opportunity to network within the industry.

#### Symposium Co-Chairs:

Nicholas Leonardi, President, TechDirect Rob Cole, Area Manager, North America **BE Semiconductor Industries**

#### Sessions will include:

- Applications Driving Wafer Level Packaging Session Chair: Dr. Tom Di Stefano, President Centipede Systems

- Wafer Level Packaging Equipment and Processes

Session Chair: Dr. Vivek Dutta, President Advenient Technology

- Wafer Level Packaging Test and Burn-in Session Chair: Leonette Stafford, Chapter President, American Society of Test Engineers

- Wafer level Packaging: Strategies for Industry Collaboration

## **Pre-registration only, please. Space will be limited!**

EVENT SPONSORS

Register online at www.meptec.org

#### Contributed by Julia Goldstein, Technical Editor Advanced Packaging Magazine

"SiPs or SOCs? The Multi-Million Dollar Question" was an appropriate title for MEPTEC's February 19 Symposium, because the answer depends on economics more than technology. Symposium Chair George Brathwaite (STATS) introduced the topic by explaining that the supply chain needs to address cost, convergence and shortened product lifecycles and asking, "Is SiP here to stay or is it a flash in the pan?" There was discussion about the definition of SiP, with most agreeing that stacked memory alone does not make a SiP, and that a SiP must include passive components (embedded or discrete) as well as semiconductor die.

Keynote speaker Charles DiLisio (D-Side Advisors) emphasized the importance of packaging by reminding people about how the plastic lid with a hole in top of it increases the value of a cup of coffee. Packaging needs to add value to semiconductor devices while providing profit to the SATS industry. The key to success, according to DiLisio, is to focus on value and profit rather than volume and cost, and one opportunity for SATS companies to add value to the supply chain may be SiPs. DiLisio warned that packaging needs to "get out from under the wheel" of Moore's Law by moving from supplying a service to providing a product. If the IC vendor becomes a supplier to SATS companies instead of the other way around, SATS can prosper. DiLisio also noted that SiP is an opportunity for EMS companies as well, who might take business away from the SATS companies.

Jim Walker (Gartner Dataquest) discussed SiP versus SOC, and other speakers made similar observations throughout the day. Important advantages of SiP are shorter time to market, lower cost and ease of combining mixed technologies, for example Si and GaAs or analog and digital. SOC can provide higher performance, smaller form factor and longer product lifecycles. Walker predicted that SiPs will make up 10 percent of all packages by the end of 2005.

Design cost is an important issue, particularly for SOC solutions, requiring a \$1B market to effectively amortize the cost. Morry Marshall (Semico Research) presented SiP as a great opportunity for unit volume in the range of 100K to 10M, with SOC feasible only for very high volumes. DiLisio's suggestion was to go after multiple niche markets rather than relying on a single large market or customer.

As many speakers noted, obtaining known good die (KGD) remains an issue for SiPs. Jan Vardaman (TechSearch International) mentioned the graveyard of defunct MCM companies and noted that many challenges are the same as they were ten years ago. Phil Marcoux (MEPTEC) asked panelists what has changed in the past ten years to enable SiP to succeed where MCM could not. Jim Rates (Chip Supply) said perhaps not much has changed: "The good news is our mature die don't require burn-in, the bad news is we don't have any mature die." Intel does, however, provide legacy products that are fairly close to being KGD. Larry Gilg (Bare Die Consortium) commented that test methods have improved, and structural test may allow use of die that have not been burned in. The problem remains that semiconductor manufacturers prefer to sell packaged die and will only sell bare die at a price equal to or greater than that of the packaged die. One solution is to use CSPs within modules (stacked packages instead of stacked die).

If SiPs can create value for the customer independent of die cost, for example by reducing footprint, they may still make money for the SiP manufacturer. The question of whether SiPs can be a money-making opportunity for SATS companies depends on their business model, which may need to change to be more like that of the EMS providers.

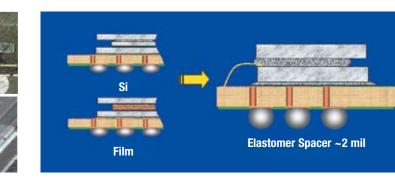

#### Contributed by Jody Mahaffey, JDM Resources

If you've been reading the trade-press these past couple months, you may think that MEMS (MicroElectroMechnical Systems) is one of the hottest topics in the industry today. It's been reported by varying sources that MEMS revenues are forecast to increase at a compound annual growth rate of 15-20% over the next few years, while units shipped are forecast to grow at a compound annual grow-th rate of 25-30%. MEMS devices are being used today in high volume applications such as accelerometers, gyroscopes, digital light processors (DLP), and printers. But this does not mean that all MEMS are yet considered mainstream or fully commercialized. One reason for that may be the issues related to packaging MEMS devices. Many people in the in-dustry believe that Wafer Level Packaging (WLP) is the ideal technology to deal with those packaging issues.

To discuss the issues related to the convergence of MEMS and WLP, MEPTEC brought some of the most prestigious names in the MEMS business together for a one-day technical symposium in May. Some of the speakers from the conference offered their insights into the quickly changing world of MEMS and WLP.

Long-time industry consultant Bance Hom acted as Symposium Chair for the MEPTEC conference. She believes that there are so many common skill sets and cross-linking packaging technologies that are easily translated bilaterally into both arenas, it seems obvious that tying the common links together will enhance the progression and agendas for both technologies.

When it comes to packaging MEMS, the lines between the front-end and the back-end of the industry become increasingly blurred. Many people believe that a partnership between the front-end and back-end is the most successful route in merging MEMS and WLP. Hom is one of those people. "With packaging becoming one of the biggest challenges for MEMS," she says, "it becomes a natural migration in the US for packaging professionals to find new challenges in this emerging MEMS field. In my own personal experience and expertise, plating, which has traditionally been a back-end operation in IC packaging, has migrated into the IC front-end (Damascene Process) and is now fully integrated into the MEMS front-end fulfilling purposes as functional device designs, sacrificial layers, etch resist and eutectic gold/tin layers for wafer bonding/lid seal operations. It also be-came a priority for MEMS technologists to have a fundamental understanding of packaging technology to design and sync up their devices to the outside world in a more cost effective and reliable mode. Wafer level packaging becomes a key enabling technology as packaging and fabs converge together."

Whether it is MEMS companies adding

packaging people, or through partnerships with back-end companies, most experts agree that packaging MEMS at the wafer level is a frontend responsibility. John Heck, Senior Engineer, MEMS & Packaging for Intel Corporation and Session Chair for the Enabling Technologies Session of the conference, believes that merging MEMS and WLP should fall to the front-end because there are critical steps which must be done in a clean room, and because the handling of MEMS wafers should be minimized with the fragile devices exposed.

Joe Brown, MEMS Director at SUSS Micro-Tec, whose company presented in the Enabling Technologies Session, agrees with Heck saying, "For the most part MEMS have been front-end process centered and for this reason have suffered by lacking advanced packaging solutions. With packaging integrated by front-end processing (prior to CMOS) MEMS can take a big step toward meeting cost targets by utilizing novel processing techniques."

Anthony Flannery, Director of Development, MEMS Gyroscope for Invensense, was a speaker in the Assembly Processes Session of the conference. Flannery believes that Wafer Level Integration, the term he prefers over WLP, must absolutely be addressed by the MEMS foundry.

According to Flannery, "The trend in the MEMS industry is moving towards a fabless model for most new companies. It is difficult for the new MEMS startup to tackle the packaging. While it may be an enabling technology, investors no longer have the stomach to invest in the capital infrastructure necessary to bring it up in-house. The cost of development and implementation must be amortized over the company's specific product line. In contrast, the foundries can leverage their infrastructure and development costs over many customers and product lines. It just makes better financial sense."

Flannery adds, "It is also doubtful that wafer level integration will be successfully addressed at the packaging level. The infrastructure does not exist there. The level of precision and control is greater than what they or their infrastructure is used to dealing with. And perhaps most importantly, many times the wafer level integration step is not the last. Additional MEMS processing must be done. That would mean it would have to go back to the MEMS foundry which smacks of inefficiency and the possibility for errors and contamination."

So assuming the answer to MEMS packaging is WLP and that this is a front-end responsibility, we asked our expert speakers what they believed were the most significant technical and nontechnical issues facing the integration of MEMS de-vices and Wafer Level Packaging and possibly holding them back from being fully commercialized. Cost and a lack of standardization (which affects cost) were common answers regarding non-technical issues.

Joe Brown of SUSS MicroTec believes, "The most significant non-technical issue is cost. This can in many ways relate to other issues such as standards but it usually comes back to cost. Most MEMS today are commodity products used in cost sensitive markets such as automotive and consumer electronics. In many ways cost adders to provide wafer level packaging must be targeted at pennies per die."

With respect to commercialization, Brown adds, "Fully commercialized would infer the 800 lb. gorillas have accepted this path for technology. Here standards and other key elements for cost reduction are needed to fully realize the potential of MEMS and WLP."

John Heck of Intel says, "I believe the lack of standard, commoditized wafer level packaging materials is the biggest problem to address. Every MEMS company is forced to develop their own proprietary solution for packaging MEMS at the wafer level since there are no standardized processes."

"Cost is clearly one of the most significant issues," agrees David Fork, Principal Scientist with the Palo Alto Research Center who presented in the Assembly Processes Session. "Wafer level packaging has the potential to lower cost in

comparison to conventional packages, but this will require a large application in volume production in order to achieve the economy of scale possible with batch fabrication."

According to some, cost isn't the only issue to be considered. Anthony Flannery of Invensense believes that available infrastructure in the areas of equipment and training is a critical issue for the convergence of MEMS and WLP. "Because of the (justifiable) reluctance of MEMS foundries to spend on anything that looks like capital investment, there is a shortage of places MEMS companies can go to get wafer level packaging services, and when they do exist, there is a usually a lack of breadth or understanding on the part of the foundry. All the technical pieces exist out there (bonders, plating setups, wafer aligners, etc.) but it is up to the foundry to put it together. Right now that has been lagging."

As far as technical issues are concerned, the answers are wide ranging. Joe Brown of SUSS believes, "The most significant technical issue is to be able to provide "0" level packaging with hermetic sealing, maintaining vacuum < 1 x 10 -3 or controlled environments with 99.999% accuracy for 10 years, having electrical feed thru, with high yield of >95%."

David Fork of Palo Alto Research Center be-lieves the protection of fragile MEMS components at the dicing step is a critical technical issue for all MEMS devices and that wafer level packaging may be just the solution.

Dr. Marc Madou, Professor of Biomedical Engineering and Integrated Nanosystems Research at UC Irvine gave the keynote address at the conference. Dr. Madou says there is just too much variability from one MEMS device to another to come up with one overall strategy that works for everything.

Flannery agrees, "I don't see any major technical issues. Many different bonding technologies have been demonstrated in the last several years. They all have their own challenges and strengths, but I don't believe there are any show-stoppers."

Along with the potential problems and pitfalls, there are also some real advantages to integrating MEMS and WLP. Most of the speakers agreed that cost can be one of the biggest advantages. John Heck of Intel feels that parallel packaging of all devices on the wafer at once will re-duce packaging cost dramatically. In addition, sealing delicate MEMS devices in the cleanroom will increase yield significantly which ultimately reduces cost.

Dr. Madou explains, "It is obvious that if we succeed to make more of the back-end processes front-end, we will drive costs down. We will also save space/volume and materials."

Most of the speakers at the May 11th conference discussed new technology that their companies have developed to help solve some of the issues relating to the integration of MEMS and WLP. But they all agree that even as new solutions are developed, there are still many issues that need to be addressed before MEMS can become fully commercialized.

"They (MEMS) will become mainstream when they get into the typical conventional computer industry, which will be in communication – RF MEMS," states John Heck.

Dr. Madou feels, "Only consumer applications really make MEMS worthwhile in the long run."

"If we can figure out ways to lower cost," adds David Fork, "there would be more MEMS applications and larger sales volumes, bringing it closer to becoming fully commercialized. There are many more novel processes and approaches than the current infrastructures can support. Only some will be adopted. Sorting this out will take time and a mixture of success and failure."

Ultimately, the goal of the MEPTEC conference was to address some of these issues and begin discussions on some of the remaining ones so that MEMS and WLP can help each other get to a fully commercialized stage.

To learn more about upcoming MEPTEC technical symposiums, as well as past symposium proceedings now available on CD, visit MEPTEC at www.meptec.org.

# We Have Complete Solutions for All Your IC Packaging Requirements.

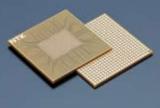

Look to NTK Technologies, a world leader in semiconductor substrates and pack-

ages, for your most demanding requirements.

Our ceramic components span the gamut from ceramic PGAs and flip chips, to lead-less chip carriers and low-temperature co-fired ceramics.

Ceramic Flip-Chip LGA and PGA

To find out how we can help you, please visit our web site at www.ntktech.com or

contact an NTK sales office today.

Let us prove that we have solutions to simplify even your most complex packaging tasks.

Organic Flip-Chip LGA

## Positive pictures of the SATS market presented at MEPTEC conference

#### Julia Goldstein, Technical Editor Advanced Packaging Magazine

MEPTEC is expanding beyond its traditional audience of Semiconductor Assembly and Test (SATS) engineers. Last year, it introduc-ed executive level membership (ELM) to reach out to top decision-makers in the SATS community. On May 12, MEPTEC held its first Interconnect Investors Conference. MEPTEC Executive Director Phil Marcoux was delighted to present "the world's most knowledgeable collection of analysts" at the conference, as well as presentations from large and small SATS companies.

There was some debate over how to view the forecast increases in capital expenditures (capex). Jim Walker (Gartner Dataquest) expressed concern about capex going too high in 2004 and then crashing in 2005 or 2006, similar to what happened in 2001 after an 84 percent growth in capex during 2000. Lucas Ward (WR Hambrecht) wasn't worried about oversupply, stating that the increase in capex comes from a low base because of decreased spending in recent years. Both Satya Chillara (RBC Capital) and Ward noted that the expected ratio of capex to revenue was in a healthy 18 to 23 percent range, suggesting that overcapacity would not be a problem.

The increased trend in outsourcing is a significant driver in the growth of the SATS market. Eric Gomberg (Thomas Weisel Partners), who coined the acronym 'SATS' for this market, noted that this outsourcing trend needs to be demonstrated to analysts before Wall Street will look kindly on SATS companies. Investors will also react positively to in-creases in R&D spending, such as Amkor's recent announcement.

Robert Krakauer from ChipPAC, and Drew Davies and George Brathwaite of STATS, discussed the upcoming ChipPAC/ STATS merger, due to be completed in June. Krakauer described it as a "most perfect" fit because of the minimal overlap in customer base and geographical footprint between the two companies. Once the merger is complete, one goal of the combined company is to identify cross-revenue synergies, with the goal of increasing the percentage of ChipPAC's assembly customers who also use the company for test services from 45 to 75 or 80 percent. Similarly, ChipPAC/STATS will work on selling assembly services to STATS' test customers.

Analyst presentations tend to focus on the top tier SATS companies, but many smaller companies are doing well in their niches. Another upcoming merger is that of UltraTera and UTAC in the area of memory test services. Jack Snyder described UTAC as "test-centric and proud of it," and expects that the merger will allow them to expand their product offerings. PSi Technologies, focused ex-clusively on the power semiconductor market, stands to benefit from growing demand for power devices. Jim Knapp discussed transfer of ON Semiconductor's technology into PSi and expanding PSi's line of QFN packages.

While the analysts presented overall positive pictures of the SATS market for the next one to two years and many SATS companies are thriving, wafer-level packaging (WLP) was mentioned as a threat to the survival of SATS companies. It is possible to envision a future in which manufacturing goes from wafer fabrication, including WLP processes, directly to board assembly, squeezing out the packaging houses. It will be interesting to see what a SATS investor conference looks like a few years from now.

# UTC

System in Package

DRAM Stack

# UltraTera Corporation

# **Stack-Die Assembly Solutions**

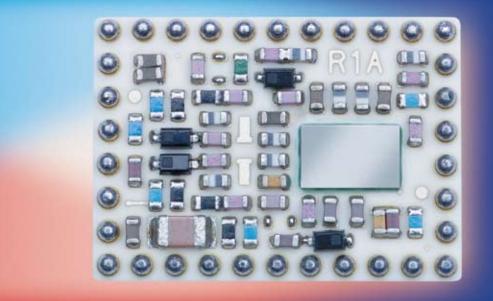

#### **Multiple Any-Size Die Stacking**

UltraTera Corporation (UTC) has developed a patented portfolio of materials and processes that enables the thinnest multi-die stacking wire-bonded solutions. The dieattach material is selectively applied with our 3D stencil-printing process, while the die stack is encapsulated with traditional molding automated equipment and materials.

UltraTera stack-die/SiP portfolio includes the unique capability to stack on top of silicon dice with centerline of bond pads, enabling compelling solutions for SiP with standard DRAM components.

UltraTera provides full in-house package development and volume production, including laminate substrate design services.

- Flexibility in stacking order, easier routing

Thinnest spacing between dice

In-house wafer thinning capability to 50µm

- Low profile wire bonding

Unlimited overhang capability

#### Taiwan Headquarters

No.2 Li Hsin Road 3, Science-Based Ind. Park Hsinchu, Taiwan, ROC Mr. Sam Au +886 3 578-8780 x6610 Sam\_Au@utc.com.tw California Office 46848 Lakeview Boulevard Fremont, CA 94538 Mr. Emilio Salvioni 510 354-6683 esalvioni@utca.com Korea - Seoul Office

601, #945-15, Janghak Foundation Bldg., Daechi-Dong Gangnam-Gu, Seoul, Korea Mr. Anthony Roh +82 2 557-4277 okroh@utckorea.com

# University of Maryland Physicists Show Nanotubes are Best Semiconductors

Lee Tune, Senior Media Relations Associate, Science and Technology and Michael S. Fuhrer, Assistant Professor, Department of Physics and Center for Superconductivity Research University of Maryland at College Park

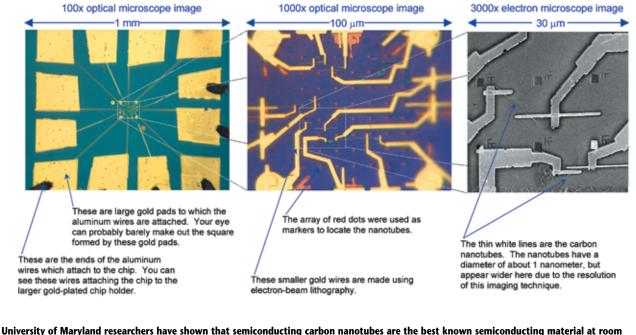

he University of Maryland's Nanoelectronics Research Group recently found that semiconducting carbon nanotubes have the highest mobility of any known material at room temperature. Mobility is a measure of how well a semiconductor conducts electricity. The finding provides new evidence that semiconducting carbon nanotubes hold great promise for replacing conventional semiconductor materials in applications ranging from computer chips to biochemical sensors.

The group, led by Michael Fuhrer, assistant professor of physics in the university's Center for Superconductivity Research, fabricated a semiconducting nanotube transistor that shows a mobility almost 25 percent higher than any previous semiconducting material and more than 70 times higher than the mobility of the silicon used in today's computer chips. These record-breaking results, which were published in the journal Nano Letters in December, have attracted wide attention.

"This was the first measurement of the intrinsic conduction properties of semiconducting nanotubes," says Fuhrer, assistant professor of physics in the university's Center for Superconductivity Research. "It is an important step forward in efforts to develop nanotubes into the building blocks of a new generation of smaller, more powerful electronics."

The International Technology Roadmap for Semiconductors, an assessment of the semiconductor industry's technolThe University of Maryland's first "smart building" is the soon to be completed Jeong H. Kim Engineering and Applied Sciences Building. This innovative and interactive building will be home to education and research in information technology, bioengineering, microelectronics and MEMS, sensors and actuators, environmental engineering, transportation systems and space research.

Students work in the Maryland MEMS lab on a university-developed polymer biochip that contains thousands of microchannels for analyzing protein signatures.

ogy requirements, says that a replacement material for silicon with higher mobility will be necessary by the year 2010. According to Fuhrer, the new findings by he and his colleagues indicate nanotubes could fill that role.

"It's true that many challenges remain before nanotubes can be used instead of silicon in computer chips," notes Fuhrer. "The contact resistance between nanotube and metal electrodes must be controlled. Nanotube batches must be prepared that contain only semiconducting nanotubes. And nanotubes must be placed with precision on substrates."

However, significant progress is taking place in all these areas, and the challenges do not seem insurmountable," he says.

Fuhrer's group, in research supported by the National Science Foundation, found that the mobility of their carbon nanotube exceeds 100,000 square-centimeters per volt-second at room temperature. Mobility is the conductivity of a material divided by the number of charges, which carry the current, and is the number typically used to compare the conduction properties of one semiconductor to another. The previous record for room temperature mobility was 77,000 square-centimeters per voltsecond in indium antimonide and was first measured in 1955. The mobility in the silicon used to make today's computer chips is only about 1,500 squarecentimeters per volt-second.

To perform their measurements, the team had to prepare extremely long nanotubes, and be able to place metal wires precisely on one single nanotube. They synthesized nanotubes with lengths up to 0.3 millimeters, or about 100,000 times the nanotubes' diameter. This is some 100 times longer than nanotubes previously studied in electronic measurements. The nanotubes were grown directly on flat silicon chips. A special technique using a scanning electron microscope had to be developed in order to locate the nanotubes on the chip so

# **University News**

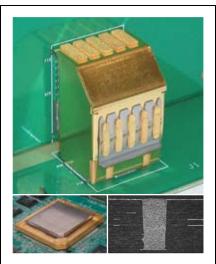

University of Maryland researchers have shown that semiconducting carbon nanotubes are the best known semiconducting material at room temperature. Carbon nanotube transistors, like those shown here, were used to make a memory cell that stores a bit of information in a single electron. One trillion of these nanotube transistors could fit on a 1 cm<sup>2</sup> chip, storing 100 gigabytes of information, or about 100 times the *Encyclopedia Britannica*. Above are micrographs of the actual device in the accompanying box.

that wires could be connected to them.

Carbon nanotubes can be thought of as a single atom-thick sheet of graphite, rolled into a seamless cylinder. Nanotubes were discovered in 1991 by Sumio Iiijima (NEC, Japan), and since then have been the subject of research around the world. Today nearly every major research university has at least one group studying carbon nanotubes.

Nanotubes are being considered for many applications in electronic devices including field-effect transistors, memory cells, and chemical and biochemical sensors. In each of these applications mobility is the key to how well the device can perform. Mobility dictates how fast the charges move through a device, so it determines the ultimate speed of a transistor.

Mobility also determines the change in conductivity that is caused by a nearby electrical charge. Thus, mobility also is a measure of the sensitivity of a transistor for detecting charge (as in a memory cell) or detecting a nearby molecule (as in a chemical or biochemical sensor).

Fuhrer's group demonstrated last year that high-mobility semiconducting nanotube transistors could detect single electrons in a memory cell. This suggests that chemical sensors made from nanotubes could detect a single molecule of a target compound.

Fuhrer's Nanoelectronics Research Group focuses on several different aspects of nanoscale electronics. The unifying theme is the use of "pre-assembled" nanoscale components to build structures, which are useful for studying the fundamental physics of electrons or pho-nons (lattice vibrations) in small structures, and also are likely to lead the way to new technologically relevant devices. "Preassembled" means materials, which are made using macroscopic techniques but are naturally structured at the nano-meter scale in one or more dimensions. As an example, consider the mineral mica: this naturally occurring layered material may be cleaved (peeled apart) using ordinary Scotch tape to obtain nearly atomically flat pieces which are only a few nanometers thick.

Research in the group combines these pre-assembled nanoscale materials with state-of-the-art lithography and analysis tools to build and study new nanoscale electronic and electromechanical devices.

Fuhrer's nanoelectronics group is part of the Center for Superconductivity Re-search (CSR) at the University of Maryland. The center conducts interdisciplinary research in the fields of superconductivity, magnetism, ferroelectricity, quantum computation, nanoscale electronics, the synthesis of advanced electronic materials, and the development of scanning probe microscopes. Center research impacts technology in areas such as communications, digital and analog electronics, medical instrumentation, and computers.

CSR is one of many centers at the University of Maryland bringing together researchers from numerous areas (physics, engineering, computer science, materials science, mathematics, etc.) to conduct research at both micro and nano scales. Other university units leading this research include the Institute for Re-search in Electronics and Applied Phy-sics, the Materials Science and Engineering Research Center, Institute for Ad-vanced Computer Studies, the Small Smart Systems Center and the Micro El-ectro Mechanical Systems Lab. And like the nanotube research of Fuhrer and his colleagues, the advances being developed in these units promise to help shape a new future for electronics.

# August Technology Appoints Cory Watkins Chief Technology Officer

Technology leader joins August Technology's strategic team

MINNEAPOLIS, MN – August Technology Corporation, a leading supplier of inspection and metrology solutions for the microelectronic industries, announced that Cory Watkins has been appointed Chief Technology Officer. In this role Watkins will oversee strategic technology and product roadmaps as well as the development of new products and technologies.

Prior to being appointed CTO, Watkins most recently served as August Technology's Director of Advanced Technology Development and was directly involved in evaluations of the Company's 2003 acquisitions of Semiconductor Technologies and Instruments and Counterpoint Solutions, Inc.

Additional information can be found at www.augusttech.com.

## Hume Integration Software Appoints Vice President of Business Development

Charbonnet named to lead major marketing and sales growth

AUSTIN, TX – Hume Integration Software has announced the appointment of Clark Charbonnet as Vice President of Business Development. Mr. Charbonnet has over 25 years of engineering, marketing, and sales experience in the high-tech arena, most recently as the head of Marketing with NewsStand Inc., a digital publishing startup.

Hume Integration Software specializes in developing software for Network Integrated Manufacturing in the semiconductor, flat-panel display, and electronic industries. Hume software enables new levels of integration efficiency, flexibility, and reliability. By carefully combining creative development efforts with selected open source software, Hume is able to provide superior function and value. The company's products are deployed in the latest semiconductor fabrication and test equipment, and are also used to integrate the diverse mix of equipment in established factories and test floors.

# Rohm and Haas Electronic Materials Names New President Microelectronic Technologies

MARLBOROUGH, MA – Rohm and Haas Electronic Materials has named Yi Hyon Paik, to succeed Stephen Robinson as President Rohm and Haas Electronic Materials Microelectronic Technologies. Most recently, Paik was President Rohm and Haas Electronic Materials Asia. Robinson will lead the company's Architectural and Functional Coatings business.

Paik joined Rohm and Haas in 1990 as a senior scientist in the Research Division in Spring House, Pennsylvania. Assignments with Rohm and Haas have included leadership roles in Strategic Planning and Electronic Materials Korea. In 1999, Paik was named to lead the Electronic Materials Asia-Pacific regional business and elected Vice President of Rohm and Haas in 2002. He holds B.S., M.S. and PhD degrees in Chemistry.

Additional information about Rohm and Haas may be found at www.rohmhaas.com.

# Maxtek Components Signs Ferrian Sales & Associates as Midwest Representatives

BEAVERTON, OR – Maxtek Components Corporation, a Tektronix, Inc. company and a custom microelectronics assembly and test service provider, has announced a formal agreement with Ferrian Sales & Associates (FSA), a manufacturer's representative firm, to act as Maxtek's agent in the Midwestern United States.

"As representatives of a variety of manufacturers, our success is directly dependent upon our ability to select partners who complement our current offerings and aid us in meeting the needs of our customers," said Greg Ferrian, president, Ferrian Sales & Associates. "Needless to say, we're excited to be working with an assembly and test service provider of Maxtek's caliber and expertise."

Maxtek Components Corporation is a proven microelectronics assembly and test company providing a complete range of custom design, prototyping, manufacturing and test services to equipment manufacturers. Headquartered in Beaverton, Oregon, Maxtek can be found on the web at www. maxtek.com.

# IC Interconnect Joins the Entegris Final Manufacturing Partner Program

CHASKA, MN – Entegris, Inc., a leader in materials integrity management, announced that IC Interconnect (ICI), an industry leader in electroless nickel/gold under-bump-metallurgy joined in the Entegris Final Manufacturing Partner program. Through this partnership, Entegris, ICI and other companies will work closely together in the development of world-class solutions for protecting bumped wafers during shipping.

The Final Manufacturing Partner program is an alliance between Entegris, OEMs and service providers to demonstrate compatibility between high-performance semiconductor handling and shipping products and process equipment. Current global partners of the program include: Entegris, Accretech, Disco, ESEC, IC Interconnect, IC Services, Integrated Dynamics Engineering, NEXX Systems, Inc., Teikoku Taping Systems Co. LTD. and Tru-Si.

IC Interconnect is ISO 9001 and QS 9000 certified and prides itself in providing strong customer service and engineering support to customers in the Americas, Europe and Asia. Additional information about ICI can be found at www.icinterconnect.com.

Entegris is ISO 9001 certified and has manufacturing or service facilities in the US, Germany, Japan, Malaysia and Singapore. Its advanced research laboratories are located in Minnesota and Colorado. Additional information can be found at www.entegris. com

# Hestia Awarded Patent for Fingerprint Sensor Package

SANTA CLARA, CA – Hestia Technologies, Inc. has been awarded a US patent # 6,667,439 titled "*Integrated Circuit Package Including Opening Exposing Portion of an IC*". This technology is presently being used in volume manufacturing of fingerprint touch sensor packages with an exposed portion of the die. Although the initial application was for touch sensors, this technology will have other applications where a portion of the die needs to be exposed.

This advanced technology provides a packaging solution and makes it possible to produce a low cost plastic molded package with an opening exposing a selected portion of the die.

Hestia Technologies continues expanding its patent holdings by utilization of its unique core technologies and capabilities.

For additional information on this and other packaging solutions provided by Hestia Technologies, Inc. Please visit their website at www.hestiatechnologies.com or contact: Hestia Technologies, 990 Richard Ave. Suite 109, Santa Clara, CA 95050

## Henkel Honored with Vision Award

Wins soldering materials category with new lead free solder paste

INDUSTRY, CA – Henkel Corporation received the 2003 SMT Vision Award in the category of soldering materials products for Multicore<sup>®</sup> LF320<sup>TM</sup>, a lead free solder paste with a minimum peak reflow temperature of only 229°C.

Designed to facilitate the transition to lead free processing, Multicore<sup>®</sup> LF320<sup>TM</sup> offers electronics manufacturers three-fold cost savings. 1) The 10°C advantage reduces damage to temperature-sensitive low Dt boards, and 2) requires less energy to power reflow ovens. 3) Multicore<sup>®</sup> LF320<sup>TM</sup> reflows higher Dt designs at temperatures up to 260°C, allowing many types of boards to be easily processed using one product.

Henkel Corporation is one of 15 companies honored with 2003 Vision Awards. SMT Magazine created the Vision Awards 12 years ago to acknowledge meaningful new products that meet significant industry challenges, creatively apply new or existing technology, represent outstanding quality and performance, and answer current economic throughput demands.

# Taiwan Sunball Acquires Advanced Precision Technology

SANTA CLARA, CA – Taiwan Sunball announced that it has acquired Advanced Precision Technology Co. (APT). The acquisition involves the purchase of APT's production technology and certain manufacturing equipment. Sunball will also take over APT's existing customers which include Carsem and UTAC and take care of relevant customer service and support.

According to Chihmin Chou, Country Manager of Sunball, "Sunball has switched from propriety cutting technology to APT's jetting technology on partial production lines and this move helps to lower production costs by increasing yield rate."

"Together, our customer base is now broader and more comprehensive" Chou noted. "This means we are capable to handle all types of customers from assembly house, IDM to IC testing company." Chou also reported that companies' product lines have been consolidated, resulting in a wide range of specification of solder balls now available from a single source.

Taiwan Sunball, established in 1999, is an ISO14001 and QS9000 certified solder sphere manufacturer. Sunball products have been certified by Amkor, ASAT, ChipPac, Hynix and ST Micro.

Sunball products are available in the US through Cumulative Technologies in Santa Clara, California. For more information call 408-969-9918 or e-mail Hal@cusjca.com.

# Carsem Receives Special Achievement Award from Analog Devices

CITY OF INDUSTRY, CA – Carsem, a leading provider of turnkey packaging and test services to the semiconductor industry announced that they each recently received a Special Achievement Award for calendar year 2003 from Analog Devices, Inc. (ADI).

During a ceremony held in Boston on March 10, 2004 the award was presented to David Comley, Carsem's Group Managing Director by John Hassett, Vice-President of Assembly and Test; and Gene Hornsby, Director of External Assembly & Test Foundry Quality.

Out of thousands of ADI suppliers around the world Carsem was among only ten to receive an achievement award.

"Analog Devices chose to recognize Carsem for their collaboration on the successful Plastics Assembly Project," said Gene Hornsby. "ADI was able to make a significant strategic change without affecting customer service or manufacturing metrics. We really appreciate the hard work and focus displayed by Carsem on helping us redeploy some of our assembly manufacturing."

# Harris Approves Maxtek Components as Quality Supplier

BEAVERTON, OR – Maxtek Components Corporation, a Tektronix, Inc. company and a custom microelectronics assembly and test service provider, today announced that Harris Government Communications Systems Division (GCSD) has surveyed, and approved, Maxtek's quality control process.

The quality assurance of Harris GCSD products, along with components and materials received from suppliers, is a vital aspect of Harris' success in fulfilling their role as a provider of mission-critical government and military communication systems. Verifying the quality control capabilities of vendors is also important to Harris' product development programs. Working with high-quality vendors eliminates the added time and expense of micromanaging vendors, applying additional controls to verify incoming quality and, at worst, the selection of and transfer of work to, a new vendor.

"Ensuring the quality of product provided by our vendors is a key component of Harris' success in consistently exceeding our customers' requirements and expectations. We regularly survey our suppliers to confirm they have the requisite quality processes in place, and are executing to those procedures," said Jeff Smith, supplier rating systems supervisor at Harris GCSD.

Headquartered in Beaverton, Oregon, Maxtek can be found on the web at www. maxtek.com.

# Asymtek and Cookson Materials Group Work Together on Jetting Underfill Project

CARLSBAD, CA - To obtain optimal process solutions for their customers, Asymtek teamed with Cookson Electronics' Semiconductor Products Division on a new project to jet underfill. Cookson Electronics Semiconductor Products of Alpharetta, Georgia visited Asymtek's application labs to test their fluid materials on Asymtek's X-1000 Series, configured with the new DJ-9000 DispenseJet<sup>®</sup>. "Many of our customers use Asymtek's technology," explains Mandar Painaik, Technical Services Engineer at Cookson Materials Group. "We wanted to learn about Asymtek's equipment so we can recommend the best materials for our customers." This collaboration enables the in-vestigation of new and innovative jetting methods and material optimization.

The two companies work together as a part of Asymtek's "Win3" program, in which key fluid formulators, technology institutes and equipment suppliers join together for the benefit of customers, each other and the industry as a whole. The combined expertise results in a "Win-Win-Win" situation that increases business for all.

Asymtek supplies award-winning automated fluid dispensing systems, specializing in semiconductor, surface mount, and electronics packaging applications. Find out more at: www.asymtek.com.

For more information about Cookson Electronics visit www.cooksonsemi.com.

# SunSil Inc. Appointed to Represent JDS Uniphase Fiber Laser Marking Systems

ALAMO, CA – The JDS Uniphase Commercial Laser Division of Santa Rosa, Calif., has appointed SunSil Inc. to represent its complete line of fiber laser marking (FLM) systems in North America.

The FLM offers many unique advantages in marking applications, according to Seth Alavi, SunSil president. "Unlike conventional solid-state lasers, the FLM systems em-ploy a double-clad optical fiber that has been doped with a rare-earth lasing material.

"The FLM has also been pumped with multiple, high-power laser diodes. This combination of technology, that fuses all the components together through to the fiber, makes the laser immune to misalignment and optical contamination," Alavi added.

The FLM is the ideal marking system for a wide variety of semiconductor package types. The fiber laser produces marks in the continuous wave operating mode that provide great uniformity, making it highly desirable for today's thinner semiconductor packages.

The FLM can be easily integrated with a wide range of other OEM parts and products. The unit is rack-mountable and includes software that enables the FLM to be integrated and controlled by most standard marking systems and test handlers.

## March Plasma Systems Opens Offices in Japan

March Plasma Systems has recently established direct operations in Japan. The new March offices are located in the Nordson facility in Tokyo, Japan. "With a growing customer base in Japan, our new offices in Tokyo allow us to provide our customers with local sales and service support," reports Peter Bierhuis, President, March Plasma Systems.

The Japan facilities will be equipped with March plasma treatment systems for customer training, demonstration and applications support. To manage their Japanese op-erations, March appointed Terumitsu Tsuji as Business Manager, Japan and named Yuji

Takai their Regional Sales Manager. Other recent activities include the appointment of new distributors for the semiconductor and PCB market segments, and the formation of strategic alliances with key allied equipment partners in the Japanese market.

With over 20 years of continuous innovation, March designs and manufactures a complete line of award winning and patented plasma systems that support all markets.

See the March web site for more details: www.marchplasma.com.

# STATS and ChipPAC Agree to Merge

ST Assembly Test Services Ltd (STATS) and ChipPAC, Inc. have announced the signing of a definitive agreement for the companies to merge in a stock-for-stock transaction to create one of the world's premier independent semiconductor assembly and test solutions company.

The combined company expects to have over US\$1 billion in revenues in 2004. It will be the 2nd largest test house and will have leadership in mixed signal testing. It will also have one of the broadest portfolios of assembly products and leadership in advanced packaging technologies such as stacked die, SiP and wafer level packaging.

Charles Wofford, Chairman of STATS, will remain Chairman of the combined company, Dennis McKenna, Chairman and Chief Executive Officer of ChipPAC, will be the Vice-Chairman, and Tan Lay Koon, President and Chief Executive Officer of STATS, will be the President and Chief Executive Officer of the combined company. The Board of Directors of the combined company will have 11 members, with STATS designating 7 members, and ChipPAC designating 4 members. The new company is proposed to be named STATS ChipPAC Ltd, and it will be headquartered in Singapore.

## ASM Receives Wire Bonder Order from Major New US Customer

BILTHOVEN, THE NETHERLANDS – ASM International N.V. has announced that its 54%-owned subsidiary, ASM Pacific Technology, Ltd., received its first Eagle-60 gold wire bonder order from an American top five manufacturer of semiconductors principally used in a broad range of ad-vanced communications applications. The equipment is scheduled for immediate delivery to an Asian factory of this new customer.

According to Patrick Lam, managing di-rector of ASMPT, the equipment will be

used in a copper wire application. "In certain ap-plications with wires of larger diameters, copper can be an efficient replacement for gold wires. Our Eagle-60 gold wire bonder platform offers the flexibility to extend process recipes to copper. We believe ASM is the world leader in copper wire bonding technology, having delivered over 200 machines to a variety of customers for applications requiring one to six mil wire diameter copper capabilities."

Launched in 2002, the award-winning, Eagle-60 gold wire bonder is the industry's first production machine capable of 35-micron fine pitch bonding. It also offers 20-percent higher productivity than its predecessor model. ASM has gained market share with each generation of new gold wire bonders since introduction in 1998. Continued market penetration, particularly in bonders, has made ASM the leader in the global semiconductor assembly equipment market since 2002. For more information, visit ASM's web site at www.asm.com.

# A Revolution in X-Ray Inspection

#### Dage Launches the Future of Xray Inspection at Semicon West

SEMICON WEST, SAN JOSE, CA, Booth 10316 – Building on their globally accepted superior image quality and ease of use, Dage Precision Industries is again setting the mark for X-Ray Inspection Technology. Dage has announced the launch of its revolutionary new flagship system the XiDAT XD7600. The XD7600 will be featured and formally introduced at Semicon West, July 14–15, 2004 in San Jose, CA.

The XD7600's innovative look and manipulator design provides for oblique angle views of up to 70-degrees for any position 360-degrees around any point of the entire 18" x 16" (458 x 407 mm) inspection area. This precise manipulation allows the XD7600 to inspect all interconnections – ball, bond and wire – on BGA and CSP devices. But Dage hasn't stopped there – the enhanced viewing capability of the XD7600 platform is further enhanced with Dage's revolutionary new 'filament-free' x-ray tube, the Dage NT250.

The NT250 x-ray tube, the first of its kind in the semiconductor packaging market, provides feature recognition down to 0.25 microns (250 nanometers) in a unique maintenance-free package. This innovative x-ray tube, coupled with a standard 'active anti-vibration control' raises the bar for the highest resolution, the best image quality available in the market and in a maintenance free package.

Visit Booth 10316 at Semicon West to see the future of x-ray inspection.

# STATS Introduces Design-for-Test to Reduce Cost of Test and Time-to-Market

DFT capabilities extend STATS' total turnkey solutions

SINGAPORE and MILPITAS, CA – ST Assembly Test Services Ltd. (STATS) has expanded its integrated turnkey solutions with Design-for-Test (DFT) capabilities that will assist customers in improving testability and throughput of their devices for a lower cost of test and faster time-to-market.

Drawing from its test expertise in the areas of wireless, broadband, networking and high end digital consumer, STATS can engage with customers upstream in the design and test process to improve test coverage and quality, reduce overall cost of IC test as well as shorten time to volume production.

As part of its DFT capabilities, STATS will provide consultation and technical training to share the advantage of deploying DFT and various DFT techniques including Scan Insertion and Automatic Test Pattern Generation (ATPG), Built-In-Self-Test and Boundary Scan (JTAG). A leader in mixed signal test, STATS is also one of the few assembly and test service providers in the industry offering Mixed Signal DFT consultation, which is a design methodology that incorporates design with test considerations.

In addition to DFT consultation, STATS provides other upstream services as part of its total test solution. These services include multi-site test, concurrent test, tester platform selection, test hardware and software as well as test program development and

pre-engineering test services.

# K&S and ASE Group **Establish Test Operations Partnership**

WILLOW GROVE, PA - Kulicke & Soffa (K&S) and The ASE Group are pleased to announce a strategic relationship between Kulicke & Soffa's Test Products Group and ASE Test Limited. As part of the agreement, K&S will provide onsite services at ASE Test's facilities in Taiwan.

The establishment of K&S probe card re-pair services at ASE Test's Taiwan facility will give ASE continuous access to K&S technical support. In addition to supplying standard epoxy probes for wafer test, K&S

Test Taiwan will also provide ASE Test with industry-leading Cobra probe card repair services, assisting ASE in offering best-in-class, rapid turn-around services to its customer base, which comprises major international wafer manufacturers.

For more information about the ASE Group visit www.aseglobal.com. Kulicke & Soffa's web address is www.kns.com.

# Asymtek Introduces the DispenseMate® 550 **Benchtop Dispensing** System

CARLSBAD, CA - Asymtek has introduced its newest compact dispensing system, the

DispenseMate<sup>(K)</sup> 550 series. The powerful benchtop unit offers advanced capability with a small footprint. Ideal for many batch dispensing operations including potting, gasketing, solder paste and adhesive dispensing, the DispenseMate 550 features a precision motion system with closed-loop brushless DC motors. It also features control for Asymtek's pumps and valves, digital gages for precise fluid delivery and ease of setup, and an optional vision system.

Two models of the DispenseMate 550 Series are available with different dispensing areas. The 555 model has a dispense area of 525 x 525 mm, or 20.7 x 20.7 in. The DispenseMate 553's dispense area is 325 x 325, or 12.8 x 12.8 in. Configured with the DJ-9000 Dispense-Jet<sup>®</sup>, the DispenseMate offers the latest, most advanced dispensing technology in a cost-effective system.

Find out more at: www.asymtek.com.

# North American Semiconductor Equipment Industry Posts March 2004 Book-To-Bill Ratio of 1.10

SAN JOSE, CA- North American-based manufacturers of semiconductor equipment posted \$1.32 billion in orders in March 2004 (three-month average basis) and a book-to-bill ratio of 1.10, according to the March 2004 Express Report published by SEMI. A book-to-bill of 1.10 means that \$110 worth of new orders were received for every \$100 of product billed for the month.

The three-month average of worldwide bookings in March 2004 was \$1.32 billion. The bookings figure is even with the revised February 2004 level of \$1.32 billion and 70 percent above the \$777 million in orders posted in March 2003.

The three-month average of worldwide billings in March 2004 was \$1.20 billion. The billings figure is five percent above the revised February 2004 level of \$1.14 billion and 40 percent above the March 2003 billings level of \$857 million

"Stable bookings levels are indicative of healthy growth as companies invest in capacity expansion that is rational," said Lubab Sheet, research development director of SEMI "Looking forward, guidance from companies points to continued strength in bookings and billings."

three-month moving average bookings to millions of U.S. dollars. three-month moving average shipments.

The SEMI book-to-bill is a ratio of Shipments and bookings figures are in

Data compiled for SEMI by the independent financial services firm of David Powell, Inc.

# K & S Announces WaferPRO plus<sup>™</sup>

# *Next generation in stud bumping technology*

WILLOW GROVE, PA – Kulicke & Soffa Industries, Inc. introduces a new high-speed, single-pass stud bumper that handles wafers up to 300 mm. The WaferPRO plus bonds 22 bumps-per-second, depending on bump type, size and pitch. It offers + 5  $\mu$ m positional accuracy at 3 sigma and can bump down to 65  $\mu$ m. This next-generation K&S stud bumper offers large table travel to handle 12" wafers in a single pass.

K&S is also offering the new WaferPRO plus kit that provides a fast upgrade path for all existing WaferPRO customers. By in-stalling the kit, which includes hardware, specialized servo code, and motion profiles, customers can increase the performance of their existing WaferPRO stud bumpers to 22 bumps-per-second.

K&S offers a wide selection of manual chucks and fully automatic wafer handling options with the new WaferPRO plus.

K&S released the WaferPRO plus for full production in May 2004. Upgrade kits will be shipped upon request from WaferPRO customers globally.

# STATS Expands Quad Leadless Package Capabilities with Dual Row Design

SINGAPORE and MILPITAS, CA - ST

Assembly Test Services Ltd. (STATS) has introduced a new dual row version of its popular Quad Leadless Package which delivers higher input/output (I/O) performance in a cost effective package for wireless and other hand held applications.

Compared to the current Quad Flat Nolead (QFN) style of packages available in the industry today, STATS' Dual Row Quad Leadless Package (QLP-DR) features a significantly higher number of I/O terminal pads in a smaller footprint. The key to the increased performance capability of the QLP-DR is in the leadframe design featuring two rows of staggered I/O terminal pads with an exposed die pad for die grounding and im-proved thermal performance. STATS QLP packages are also available with nonex-posed pad to enable higher density board level routing.

Utilizing the same assembly and test process as the standard Quad Leadless Package, QLP-DR offers a high performance device with high yield and reliability at a lower cost than many laminate or tape substrate based chip scale packages and wafer level chip scale packages. In terms of environmentally friendly solutions, QLP-DR is a lead free/ green package which is more cost effective than laminate based packages. ◆

# WHY PUT OFF TODAY WHAT A CONSULTANT COULD HAVE DONE YESTERDAY?

# Outsourcing, Planning, Analysis, Quality and other management tasks require skilled resources.

When the resources aren't readily available use an experienced consultant. **Phil Marcoux** of **PPM Associates**, and Executive Director of MEPTEC provides this experience. Past experience includes executive management, including CEO and Board positions, engineering and quality management positions within leading corporations. Clients have included NASA, USAF, Harris Semiconductor, Cypress Semiconductor, National Semiconductor, Ericsson, Cisco, 3Com, Dupont and other multinational companies.

## Phil Marcoux • PPM Associates

650-961-7909 • email: pmarcoux@ppmassoc.net

# **MEPTEC Member Company Profile**

Long considered one of the best kept secrets in the subcon world, NS Electronics Bangkok (NSEB), has developed a strong reputation for high quality, short cycle times, and excellent customer service. These attributes are the core of an overall strategy by NSEB management to create a superior subcon experience for major semiconductor manufacturers worldwide. A well balanced portfolio of packages and services serve the entire community of IC manufacturers whether in memory, linear, logic, or RF products.

ith more than 30 years experience as an IC assembly and test facility, the NSEB team can easily argue that they may be the single most experienced collection of assembly and test engineering expertise available in the Far East. Their collective experience means that they can speak the lingo needed to support top-of-the-line semiconductor companies in the US who are seeking competent support for their production needs. This applies to the smallest start-up company up to the largest Fortune 500 company; all their customers deserve the best in service available. The most frequently heard complaint from our visiting customers? "Why can't our other subs perform as well as NSEB?"

Born from the decision of National Semiconductor to reduce its offshore factory base in the early 1990's, NSEB was purchased by local Thai investors in 1993. It is now completely independent of National. Taking advantage of the core competence in IC assembly and test, the new management team has developed NSEB into what may be the single best medium size IC assembly/test house in the Far East. During

NSEB engineers review MSL sonoscan results.

the last four or five years they have been ranked in the top five or six subcons world-wide in terms of units shipped. Under any circumstances, to ship this volume (averaging about 67M units per day, including turnkey) to world-class customers throughout the world, indicates a system which is both tightly controlled as well as motivated to achieve best-in-class performance. The test floor, currently running at capacities of about 4M to 5M units per day, must be considered one of the largest, and most successful, independent test floors in Asia. Additionally, extra services available include burn-in, wafer sort, failure analysis and reliability labs, and creates an environment very much like the large IDM companies in the US.

At least part of the success of NSEB can be attributed to the fact that the company has not strayed from its primary capabilities. Due to the fact that the many smaller conventional packages in their portfolio tend to be more manual intensive, NSEB has found they are much more competitive than some of the larger SATS companies in Korea, Singapore, Taiwan, and Japan. Also, they have found that the popularity of these products is growing, primarily due to the natural trend in semiconductors to continually decrease the die size.

These days what used to require a package like an 8 SOIC, can easily fit into a smaller package like an SC70 or a SOT23.

NSEB utilizes only the best production equipment available in order to satisfy its world class customer base with reliable high-volume capacity.

NSEB technician reviews leadframe quality check.

A world class test floor makes NSEB a leader in turnkey assemb; y and test solutions.

Similarly, these packages require less material, and therefore offer a more cost-effective solution to their customers.

Being ranked "best-in-class" by several of NSEB's most important customers is not simply a consequence of setting strategy. Due to the high-volume nature of the core business, it's necessary that they create a factory which utilizes the best, highest quality equipment available. This equipment is specifically designed to handle the high quality, and short cycle time nature of this volume driven IC business. NSEB cannot achieve anything if their equipment breaks down at the wrong time, and they have to tell their customer... "sorry, but we can't deliver." For this reason they only work with equipment suppliers who provide them with the most reliable, best made equipment available world-wide. It may cost a little more, but if the customers are happy with the end results, then it's well worth it.