A Publication of The MicroElectronics Packaging & Test Engineering Council

#### **INDUSTRY NEWS**

**Rudolph Technologies** and **Entrepix, Inc.** have announced that Rudolph has granted Entrepix an exclusive license to manufacture, sell, service and support the Rudolph AutoEL<sup>®</sup> series of thin-film ellipsometers. *page 12*

**MIG** (MEMS Industry Group), the trade association representing the microelectromechanical systems (MEMS) and micro-structures industries, and **MEPTEC** have announced a strategic alliance that will benefit companies designing and packaging MEMS devices. *page 12*

**SEMI**, along with **Freiburg Wirtschaft Touristik und Messe GmbH & Co** (FWTM) and **Solar Promotion GmbH**, organizers of Intersolar, the world's largest trade fair for solar technology, have announced a partnership to host Intersolar North America. *page 13*

**Asymtek** has introduced its next generation conformal coating platform, the Select Coat<sup>®</sup> SL-940E. *page 15*

**SUSS MicroTec** has announced that it has received the first order for its new Gamma XPress coat/ develop cluster from **Rohm and Haas Electronics Materials**. *page 16*

The Pan Pacific Microelectronics Symposium and Tabletop Exhibition, sponsored by SMTA, will be held January 22nd through the 24th at the Sheraton Kauai Resort. *page 17*

## The 4th Annual The Heat is On: Thermal Solutions for Advancing Technology

One Day Technical Symposium and Exhibits Coming to San Jose February 28th ... page 5

#### **MEMBER COMPANY PROFILE**

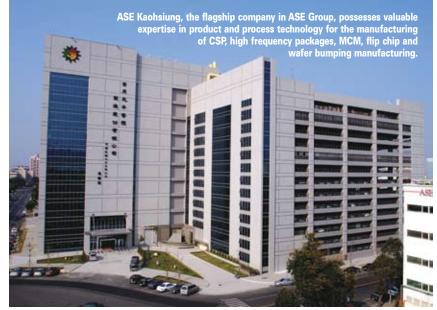

**ASE**'s manufacturing was initially carried out in Taiwan, and later expanded into seven countries spread over four continents. From an original employee headcount of just one hundred, ASE now employs over 28,000 people worldwide. Today, ASE has achieved market leadership, and is the world's largest provider of independent semiconductor manufacturing services in assembly and test. With key customers spanning the consumer, computing, and communication sectors, ASE serves both the IDM and Fabless communities, to meet the electronic industry's growing needs. *page 18*  he ASE Group was established in 1984 as a semiconductor assembly company headquartered inTai-

wan. Over the course of 23 years, ASE has gradually evolved into a \$3.1 billion company, offering a broad range of services including IC packaging, test, material, with complete turnkey capabilities.

Semiconductor equipment bookings remain even with September 2007 level. *page 16*

## the right fit

With the right investments in the right places at the right time, we're uniquely positioned to help you make the connection from idea to product success.

Honeywell's ongoing research and development in chemistry, metallurgy, and the processes that bring them together—from our new packaging R&D facility in Spokane, Washington, to our

technology center in Shanghai, China—ensure that wherever challenges arise, we'll continue to create solutions that solve them. And as a partner to most of the top semiconductor houses worldwide, our technology portfolio is consistently at the forefront of invention, empowering the global leaders of innovation. Honeywell Electronic Materials—bridging the path to accelerated success.

Contact Honeywell for solutions to your puzzle... visit www.honeywell.com/sm/em or call 1-408-962-2000.

Volume 11, Number 4 A Publication of The MicroElectronics Packaging & Test Engineering Council

P. O. Box 222 Medicine Park, OK 73557 Tel: (650) 714-1570 Email: info@meptec.org

> Published By MEPCOM

Editor Bette Cooper

Design and Production Gary Brown

Sales and Marketing Kim Barber

Contributing Editor Jody Mahaffey

#### **MEPTEC Advisory Board**

Seth Alavi SunSil Jeffrey Braden sors. Inc **Philippe Briot** P. Brio Joel Camarda Exar Corporation Gary Catlin Plexus Tom Clifford Rob Cole John Crane J. H. Crane & Associates Jeffrey C. Demmin Tessera **Bruce Euzent** Altera Corporation Skip Fehr Julia Goldstein Advanced Packaging Magazine **Chip Greely** Oualcomm Anna Gualtieri Elle Technology Lan Hoang Xilinx Bance Hom

Consultech International, Inc Ron Jones

N-Able Group International Pat Kennedy

Gel-Pak Nick Leonardi

remier Semiconductor Services Phil Marcoux

> TPL Group Bhavesh Muni

Henkel Corporation Mary Olsson Gary Smith EDA

Marc Papageorge Semiconductor Outsourcing Solutions

Rich Rice ASE (US) Inc. Jim Walker Gartner Dataquest Russ Winslow Six Sigma

MEPTEC Report Vol. 11, No. 4. Published quarterly by MEPCOM, P. O. Box 222, Medicine Park, OK 73557. Copyright 2007 by MEPTEC/MEPCOM. All rights reserved. Materials may not be reproduced in whole or in part without written permission.

MEPTEC Report is sent without charge to members of MEPTEC. For non-members, yearly subscriptions are available for \$75 in the United States, \$80US in Canada and Mexico, and \$95US elsewhere.

For advertising rates and information contact Kim Barber, Sales & Marketing at 408-309-3900, Fax 1-866-424-0130.

### **Council Update**

t's hard to believe that another year is coming to a close. It seems just a short time ago we were wrapping up our last issue of 2006, and now it's upon us again! Here at MEPTEC we're looking forward to an exciting 2008. One of our biggest efforts is a brand new website – we'll be launching it on January 1. We look forward to continuing to bring you our high quality services which include our popular technical programs, as well as networking and marketing opportunities. We've got several new programs in the works that you'll be hearing about soon.

See pages 6 and 7 for summaries of our last two technical symposiums. Our 2nd Annual "Medical Electronics Symposium – Growth Opportunities for the Microelectronics Industry" is covered by Jody Mahaffey of JDM Resources/e-Reach Communications. We'd like to thank Arizona State University again for hosting this event. They have invited us back, so we'll keep you posted on our third annual event covering this important area of the microelectronics world.

Our most recent event, "Substrates – The Foundation of Semiconductor Packaging", is covered in this issue by Jeffrey Demmin of Tessera, and contributing editor for Advanced Packaging Magazine. In this event cost and co-design topics came across as crucial issues of semiconductor packaging. Both event synopses include presentation summaries. CDs of both symposiums' proceedings are available – contact the MEPTEC office for details.

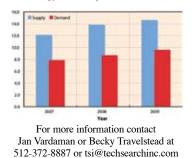

Our Industry Analysis this issue came about as a result of our Substrate event's keynote speaker. The article is a joint effort by MEPTEC supporters TechSearch International, Inc. and SEMI. In "Laminate Substrates Lead the Growth in the Semiconductor Packaging Materials Market", Jan Vardaman of TechSearch and Dan Tracy of SEMI give us a summary of their new study called the Global Semiconductor Packaging Materials Outlook (see page 10). The market for semiconductor packaging materials is expected to reach \$15.5 billion in 2007 and grow to \$20.2 billion by 2011. The article covers the importance of laminate substrates, flip chip laminate substrates and substrate supply and demand. Thanks to both parties for this important study.

Our Company Profile this issue is from longtime Corporate member, the **ASE Group**, a truly impressive organization. It was established in 1984 as a semiconductor assembly company, and has since grown and evolved into a \$3.1 billion business offering not just assembly but also test services, systems and materials design and service, among many others. This profile focuses on their China facilities and markets, and their expansion in that area. See their story on page 18.

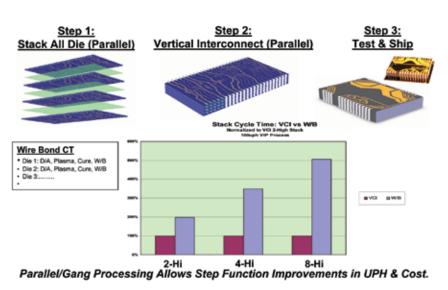

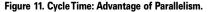

Our first feature article is from Vertical Circuits, Inc. (VCI) on "A Low Cost Alternative to Thru Silicon Via – Can Packaging Technology Provide the Missing Link?" In this article it is discussed that current interest has been focused on thru-silicon via, which according to VCI is in essence a front-end solution. VCI sees the solution remaining in the back-end through the use of virtual vias. See page 20 for this informative article.

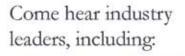

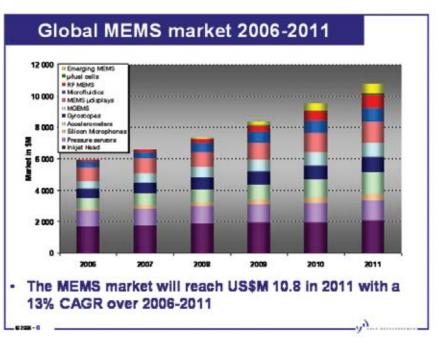

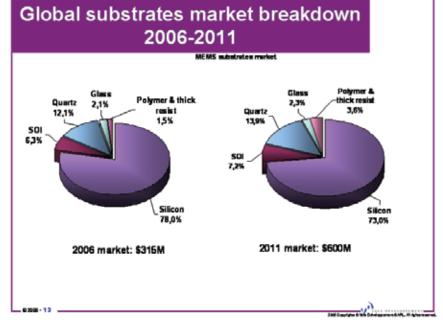

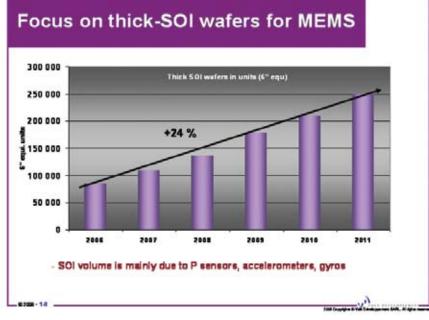

Our next feature article is from Jean-Christophe Eloy of Yole Développement. Yole is a market research and strategy consulting company, and Eloy has been a speaker at several MEPTEC events. He presented at our recent Substrates event, and we asked him to follow up with an article on the same topic: *MEMS Substrates – Going to 6 Inch and 8 Inch.* See page 26 for his breakdown of the substrates market, and how the 2006 market was \$315 million, with a look forward to 2010 at \$600 million. We'd like to thank Mr. Eloy for traveling

#### **Issue Highlights**

| Industry Analysis                               | 10 |  |

|-------------------------------------------------|----|--|

| Industry News                                   | 12 |  |

| Member Company Profile                          | 18 |  |

| Feature Articles                                |    |  |

| A Low Cost Alternative to<br>Thru Silicon Via   | 20 |  |

| MEMS Substrates –<br>Going to 6 Inch and 8 Inch | 26 |  |

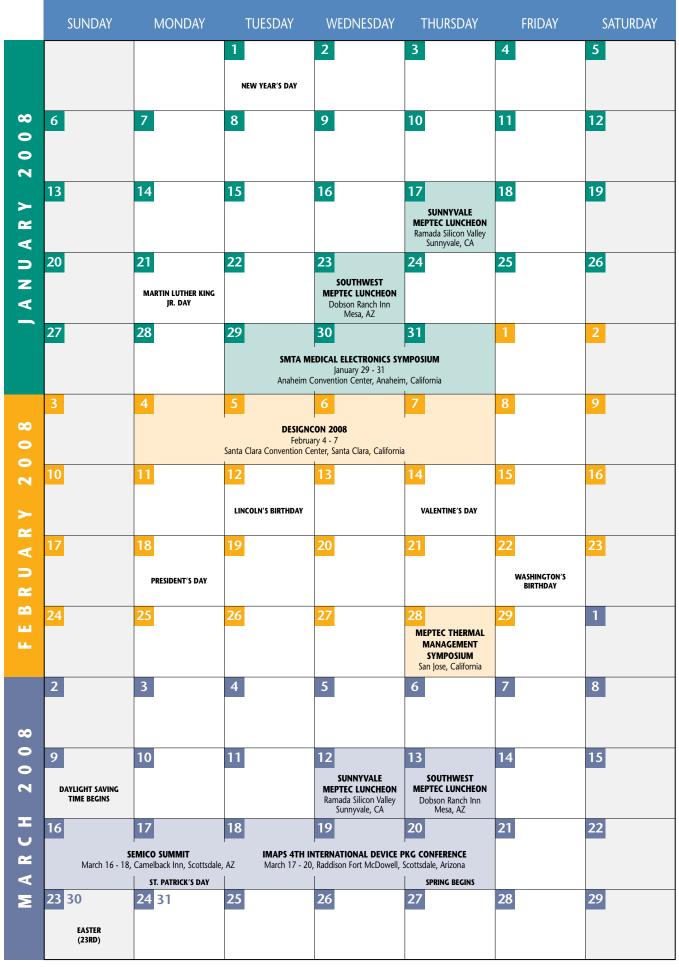

| Events Calendar                                 | 37 |  |

| Editorial                                       | 38 |  |

|                                                 |    |  |

from France on many occasions to speak to our members about all things MEMS.

Our Editorial this issue is from MEPTEC Advisory Board member **Bhavesh Muni** of **Henkel Corporation**. In *"Why Film Will Make the Final Cut for Stacked Die Applications"*, Bhavesh makes the case for advanced integrated package technology. He maintains that die attach film materials, specifically Dicing Die Attach Film (DDF) and Flow Over Wire (FOW) will be the driving force for successful integrated package production. He describes the benefits of DDF, and ends by saying "As always, consumers will be the big winners". See his enlightening piece on page 38.

This issue is one of our biggest "bonus distribution" issues annually, meaning that in addition to our regular circulation to our members and at MEPTEC events, this issue is also being distributed at several other industry group events. We're pleased to be sponsoring two SMTA programs (their Medical conference and Pan Pacific), as well as IMAPS Device Packaging, DesignCon 2008, and the Semico Summit.

We'd like to thank all of our contributors for making this a great issue. If you're reading our publication for the first time at one of the many events where we distribute, or if you're a new member, we hope you enjoy it. Thanks for joining us!

- Free Wireless Internet Access

- 176 Spacious Guest Rooms

- Full Service Restaurant

- In Room Coffee Makers, Refrigerators, Hairdryers, Irons and Ironing Boards, AM/FM Clock Radios and Digital Safes

- On Demand Movies

- Voice Mail

- Heated Outdoor Pool and Jacuzzi

- Banquet/Meeting Space for 250

- Japanese Tatami Rooms

- Minutes from Light Rail, Santa Clara Convention Center and Paramount's Great America

- 24 Hour San Jose Airport Transportation

- Special Group Rates and Packages

## The only full services Ramada in Silicon Valley 408-245-5330

1217 WILDWOOD AVENUE • SUNNYVALE, CA 94089

#### ONE-DAY TECHNICAL SYMPOSIUM & EXHIBITS A

February 28, 2008 • Wyndham San Jose • San Jose, California

## The 4t<u>h Annual</u> The Heat is On: **Thermal Solutions for Advancing Technology**

PLATINUM SPONSOR

#### Honeywell ELECTRONIC MATERIALS

**GOLD SPONSORS**

Sessions will include:

- Thermal Solutions for **Tomorrows ICs**

- LEDs and Solid State Lighting **Bright Future for Hot Products**

- Telecommunications Power Users are Power Hungry

- Portables Things Are Getting Faster, Smaller and Hotter

#### ONLINE REGISTER TODAY АТ WWW.MEPTEC.ORG

MEDIA SPONSORS

## Maine Event Follow-up

### 2nd Annual Medical Electronics Symposium – Growth Opportunities for the Microelectronics Industry

#### Jody Mahaffey JDM Resources/e-Reach Communications

he opportunities available for microelectronics packaging to fit into the growing field of medical electronic products was the focus of MEPTEC's 2nd Annual Symposium on Medical Electronics held on September 25th, 2007, at Arizona State University. This year's Medical Electronics symposium was once again presented in association with the MacroTechnology Works and co-chaired by Nick Leonardi of Premier Semiconductor Services and David Ruben of Medtronic who led an interesting and diverse list of experts through the presentations of the day.

Celeste Null of Intel began the program with a lively keynote presentation showing many of the breakthrough technologies being developed between the medical and electronics communities that could virtually revolutionize the way our healthcare system works. According to Null, our healthcare system must evolve quickly to keep pace with global aging, a growing clinician shortage and the technology expectations of our next generations. Many people in the healthcare area are looking to the electronics industry as the path to an integrated implantable for a total endto-end solution.

The first session, a business and technology overview, chaired by Dan Nienhauser of ASU's MacroTechnology Works included views by several of Arizona's academic experts, including Dr. Bruce Towe of ASU. Dr. Towe's presentation showed the many opportunities for microelectronic implants being developed today. For our military personnel, implantable bio sensors are being developed which may one day be able to track a soldier's health and external environmental situations, such as biohazards, as an early warning detection system. Injectible bio sensors could be used for getting immediate health information in emergency situations. For a more everyday purpose, implantable bio sensors can be used to continuously monitor blood glucose levels rather than invasive monitoring, such as blood draws.

Many of the envisioned sensors must be packaged to endure many years of relatively hostile conditions inside the human body while communicating wirelessly through the skin. One of the issues to solve in order to further facilitate the usage of implantable devices, is finding a power source other than batteries, which eventually wear out. For example, piezoelectric microstimulators (powered by motion like watches) are being developed at ASU for use in pain management and possibly treatment for Parkinson's disease. Other power options being developed include RF inductive and transcutaneous solar.

Dr. Jerzy Rozenblit and Dr. Allan Hamilton of the University of Arizona presented a fascinating example of how the medical and electronics communities can work together in their presentation, Virtually Assisted Surgical Training: Concepts, Foundations and Sensor-Based Techniques. The first half of this presentation was a little depressing, focusing on the many mistakes made by our medical community which are classified as Medically Adverse Events (MAEs). The numbers were quite frightening, showing that one out of every six patients will suffer from an MAE and medical errors are the fifth leading cause of death in the United States. Knowing the full scope of the problem proved the importance of the research presented in the second half of the presentation. Research is currently underway at the University of Arizona to develop computerized and sensor technology to teach surgeons how to perform surgical procedures with more accuracy. The system being developed, the microBIRD<sup>™</sup> 6, uses virtual tissue and organ models and is capable of high fidelity motion tracking of surgical instruments to provide tracking of the trainee's dexterity and skill level while offering computer aided movement guidance.

Ending session one, **Sayfe Kiaei** of **Connection One NSF Center** gave a more in depth look at the development of wireless sensors and MEMS for bio-implants and biotelemetry. Some examples discussed were; MEMS microphones used in hearing aids, implantable wireless neural-sensors and controls used to send information to prosthetics, and 3-axis MEMS accelerometers used to locate movement and sense health. These last being used for fireman, elderly and the military.

The second session, *Packaging Medical Electronics* focused on the special challenges that packaging systems must solve to be used in medical applications.

Session leader **Dr. Roger Emigh** of **STATS ChipPac** started his session with **Randal Schulhauser** of **Medtronic** who showed us the unique packaging challenges that Medtronic faced while developing their family of implantable Reveal<sup>®</sup> monitor systems to diagnose cardiac arrhythmias and the solutions they implemented to bring these products to market.

Eric Beyne, Program Director of IMEC next presented information on new products being developed to allow embedding ultrathin die and die stacking as an alternative for through-silicon vias in 3D stacking. In this process, ultra-thin die are embedded in silicone ribbon and stretchable substrates to create a flexible electrode array for use in medical devices such as cochlear implants. According to Beyne, one of the largest problems associated with developing new technology is the narrow scope of approved materials due to the stringent regulations involved.

Lisa Murphy of Ansoft Corporation finished off the session with a look at how advances in three-dimensional (3D) electromagnetic simulation software using the fullwave finite-element method (FEM) are moving out of the traditional applications areas and emerging into the biomedical engineering field. Case studies were presented including Duke University's design of microwave heating elements for hyperthermia treatment, the design of a directional microwave heating element used in photodynamic cancer therapy, and a joint program between Ansoft and Philips to analyze and improve MRI systems using a human-body model created by Ansoft.

More enabling technologies were discussed in the third session led by **Bruce Bowers** of **Flip Chip International. Bob Gosliak** of **HEI** started off the session showing how high-density interconnect (HDI) flexible substrates are used in many medical applications such as medical imaging, cardiac devices and neurostimulators. The advantages of HDI flex increase as the size of the devices decrease. With advancements in flex circuits such as Fold-Over Flex and Rigid Flex technology, flexible substrates are poised for continued growth for use in medical applications to provide a space-efficient packaging solution.

In the next presentation, Gary Dashney of IceMOS Technology showed how Silicon-On-Insulator (SOI) substrates are being used to further enable MEMS devices for the medical market. According to Dashney, SOI substrates offer greater control of the mechanical properties of MEMS structures and enable more complex designs due to embedded structures in multi-layers. The third session finished with an interesting presentation by Kent E. Dicks of MedApps. MedApps is developing a wireless system that will take data from several different bio devices (including implantables), using Bluetooth technology and make them communicate to each other and to external media. This new technology is designed to help those patients who suffer from one or more chronic diseases such as diabetes, congestive heart failure (CHF), COPD, asthma or other diseases, lead a more active lifestyle by allowing their medical records and monitoring data to be disseminated through wireless devices to physicians and physician's offices and can help monitor and react to changes in individuals' medical conditions.

The final session of the day, led by John Crane of J. H. Crane and Associates brought together some leading medical products companies to discuss their products and developing technologies. D. Nguyen of Bioptics, started off the session with a look at the design of an innovative X-ray active pixel sensor in CMOS technology to help advance Digital Mammography. Among other advancements, the new technology will allow for immediate testing during surgery to make sure all cancer cells have been removed.

We found that packaging issues don't stop at the semiconductor IC level when the next speaker, **Joan Vrtis** gave a fascinating presentation on a "Palm-Size Breath Analyzer for the Detection and Monitoring of Metabolic States" being developed by **Kemeta**. This product is used to directly monitor an individual's fat burn rate by analyzing breath acetone which is a biomarker of fat metabolism. One of Kemeta's obstacles to overcome in bringing this product to market was userfriendly packaging with easy to understand readings. In order to meet these demands, semiconductor and portable hand-held application knowledge had to be leveraged.

As a perfect wrap up for the session and the day, **Ken Bobis**, Director of Technology for the **Mayo Clinic** presented, "Advancements in Hospital Technology" to show how the electronics and medical industries are joining together to automate the healthcare industry with developments in electronics medical record systems, expanded use of RFID and systems such as the Healthy Home. The Healthy Home is a new system being developed that will put sensors into a patient's home and connect them with an outside monitoring system. Sensors showing shuffling feet (indicating an increased risk of tripping) and sensors in a patient's bed that periodically takes the person's vital statistics are among those being developed.

The audience seemed to be very pleased with the speakers, topics and symposium as a whole. "This symposium has again highlighted that the medical industry will continue to leverage state-of-the-art electronic technologies to advance the capability of implantable devices, diagnostic equipment and other types of medical systems," according to Nick Leonardi, Symposium General Co-Chairman and Business Development Director for Premier Semiconductor Services.

One of the major unresolved questions that came out of the symposium was, "Who will pay for advancements in medical electronics?" If there are not monetary incentives for doctors and hospitals, they will be less likely to spend the extra money needed to put some of these new systems in place. Perhaps this will be a session topic for MEPTEC's 2008 medical electronics symposium.

Jeffrey C. Demmin Tessera

EPTEC's final technical symposium of 2007, "Substrates: The Foundation of Semiconductor Packaging," identified cost and co-design as pivotal issues for the most critical component of semiconductor packaging.

Jan Vardaman, president of TechSearch, opened with a keynote titled "Markets and Trends in Laminate Substrates." She highlighted the growing importance of laminate substrates, noting that they represented 37% of the \$15B packaging materials business in 2006, easily surpassing leadframes at 20% of the market. In terms of volume, the shift of DRAM from TSOPs to laminate CSPs was a big driver of that trend. Another part of the equation was flip chip substrates, which didn't have as much volume but accounted for over half of the dollar value of the substrate market. As she usually does, Vardaman provided a list of significant substrate suppliers with comments on their current status. Ibiden in Japan was identified as the largest, while Endicott Interconnect was cited as the only remaining major U.S. supplier of flip chip laminate substrates.

Vardaman also discussed cost issues, including the impact of gold and copper prices, as well as energy costs, which affect the whole supply chain. The cost of highdensity, thin core substrates remains high, but the technology has developed and suppliers are waiting for demand to catch up and drive the prices down. Overall, prices for flip chip laminate substrates have improved as a result of increased capacity in the factories. Her last bullet – "co-design key to future success" – was a preview of a point made by many of the speakers to follow about the increasing complexity of semiconductor products and their substrates.

Symposium co-chairs Joel Camarda of Sipex and Rich Rice of ASE structured the event along the lines of the supply chain, and the first session, chaired by Lan Hoang of Xilinx, covered "Substrate Manufacturing and 1st Level Interconnection." The first talk of the session, "Buildup Technology Requirement Roadmap: An FPGA Sector Perspective," was given by Paul Wu of Xilinx. This was an excellent choice to lead off the symposium program – a significant user of a technology presenting its upcoming needs is an ideal conference talk. A key point made by Wu was that, although Xilinx does not shrink its silicon technology too fast because of cost and yield issues at the leading edge, the increasing density and performance still puts a lot of pressure on the package technology. He cited power integrity as a serious challenge, requiring co-design of the power distribution network linking the silicon, package, and board. He also gave some numbers for the upcoming progression of linewidths and other substrate features and explained that all of these design features affect the cost.

Following Wu's talk from the user perspective was a representative from the supplier's side, James Lin of Kinsus. His talk, "Example of a Substrate Technology Roadmap," provided the Kinsus view of upcoming requirements and capabilities. The range of products shown - wire bond and flip chip versions of CSP, SiP, PBGA, and very-high density PCB - was an indication of the challenges that the suppliers face. Lin's roadmap charts were quite detailed and complex, illustrating the trends in manufacturing processes, layer count, surface finish, bump pitch, dielectric material, linewidths, and many other variables. Those charts also showed that new developments are needed every year in virtually every area. The technology is indeed moving very quickly. Lin wrapped up his talk with some interesting cross-sections showing their approach for embedded passives.

The last talk of the first session, "Flip Chip Packaging Applications Using Advanced Substrates," was given by **Bernd Appelt** of **ASE**. ASE, as a packaging subcontractor that also has in-house substrate

## Maine Event Follow-up

manufacturing capability, should have excellent insight into both the requirements and the capabilities. Appelt presented quite a bit of manufacturing, design, and reliability data on thin core and coreless substrates for large-die flip-chip applications. Some key results of the analysis showed why electroless nickel / electroless palladium / immersion gold has become a popular choice for surface finish on advanced substrates (... in spite of the unfortunate acronym ENEPIG). A key advantage is that it works well for both wire bonded and soldered connections.

Bruce Euzent of Altera chaired the second session, "Design and Simulation: Silicon, Substrate, System," with speakers from a chip company, a packaging company, and a design specialist. Hong Shi of Altera led off with "Deliver Electrical Performance to FPGA and ASIC Applications by Die-Package-System Co-Design." He highlighted application challenges, including dramatic shrinking of timing margins, and analyzed key issues in the die, package, and board that affect the performance. Like the Xilinx speaker in the first session, he cited power distribution as the dominant factor in timing margin performance. Shi then showed some elements of co-design strategy, including optimized package floorplanning, I/O vs. ground distribution, and decoupling strategies. On-package decoupling was shown to be a good approach for reducing power noise.

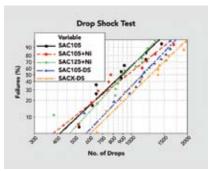

Sean Moran of Tessera presented mechanical and reliability issues in substrate design in his talk "Substrate Topologies and Mechanical Reliability Analysis for Miniaturized Mobile Systems." He summarized the drivers for thin components and substrates, as well as the various factors affecting the mechanical, electrical, reliability, and environmental properties of the materials. A good example on the reliability side is cyclic bending resulting from the rise of texting with mobile devices. Moran noted that the material requirements are often in conflict with each other, but that low cost is the one constant in the list of desirable attributes. He reviewed some thin substrate approaches, including Tessera's copper post technology, and illustrated some of the best ways to compare technologies. One key conclusion is that material improvements are needed from material suppliers to continue meeting the needs.

Some detailed electrical design and simulation work was presented by **Manoj Nachnani** of **Enabling Solutions**. His talk, "*Challenges in Design and Electrical Analysis of Low Cost Wi-Fi 802.11 System in Package*," started by highlighted the significant challenges of SiP design. Design tools for pieces of the process exist, but they still fall short of an integrated design capability. The set of skills required of a SiP designer are also prohibitively diverse, covering layout, RF analysis, digital design, and manufacturing knowledge. Better quick-turn prototyping capabilities would also help the industry. Nachnani suggested that designers should use the simplest possible available, highvolume technologies whenever possible to minimize risks and maximize the chance of design success. His 802.11 case study illustrated his approach to SiP design challenges.

Bhavesh Muni of Henkel chaired the third sessions, titled "2nd Level Interconnect and Reliability," which included the diverse perspectives of an EMS provider (Jabil), an IC company (LSI), and an OEM (Cisco). Quyen Chu of Jabil presented "Ultra-fine Pitch SMT Assembly – Assembly Challenges of Product Miniaturization to the EMS." This included extensive design-of-experiments (DOE) work on SMT process and design. It was a good reminder for the chip and package designers out there what the next company in the supply chain has to think about. One interesting outcome was that the DOE approach can be used to maximize the stencil thickness while allowing for 0.4 mm pitch CSPs.

Kishor Desai of LSI Logic followed Jabil with "IC Package Design, Materials, and Assembly Ensuring System Level Solu-

*tion.*" He started with the concept that you need to understand the needs of your customer's customer to achieve the best design. LSI has spoken prominently on the topic of co-design, and Desai showed here how the substrate is that center of co-design. He presented electrical, mechanical, thermal, and reliability evaluations of complex designs, illustrating the many factors that go into identifying the best design for a particular application. Board level assembly challenges are also a significant part of the equation.

The messaging in this session was consistent, with Mudasir Ahmad of Cisco Systems presenting "Impact of Package Substrate Design and Material Changes on 2nd Level Interconnect Reliability." A key point from Ahmad was the value of doing a second level qualification earlier in the design process to identify any issues that might appear downstream from the package-level design. This would not need to be a full daisy-chain qualification, since a fairly simple second-level qualification can identify the majority of issues. He also reviewed high-performance requirements, including low-k dielectric effects and warpage with large devices. In his summary, he relayed Cisco's recommendation that "the substrate and packaging industry needs to transition to an iterative, concurrent qualification process that spans silicon level, substrate level, and board level reliability in ever shrinking design cycles." There is plenty of work for everyone in the supply chain.

Finally, the fourth session covered "Emerging Substrate Technologies," following the MEPTEC tradition of looking ahead in the final session of its technical symposia. Session chair Tom Clifford recruited Joe Fjelstad of Verdant Electronics, Jean-Christophe Eloy of Yole Developpement, and Tuomas Waris of Imbera to give some excellent talks on new technical solutions to industry challenges.

Verdant is the high-profile start-up that serial entrepreneur Joe Fjelstad launched to develop and proliferate an intriguing embedded technology. Nearly any kind of device - packaged or bare - can be embedded in the substrate, with the exterior contacts eliminating the need for solder. Fjelstad emphasized the low cost and simplicity of his "Occam Process," and challenged the industry to think of electronic assembly in some significantly different ways. He showed some of the design and process options for embedding devices in a single molded component, and he drew an analogy to Lego block assembly. Verdant's technology is arguably the most intriguing development of 2007, and after Fjestad's inspiring talk, it is possible to envision the approach gaining some traction. It should be interesting to see what happens over the next year or two.

Yole's founder and general manager Jean-Christophe Eloy provided a view from the MEMS world with "Status of the MEMS Industry: Substrate and Material Markets." He described the maturing markets and rapid growth in areas such as RF MEMS and silicon microphones. The MEMS foundry business is also healthy – some MEMS foundries are actually profitable – and 8" wafer processing is on the rise. Silicon is still the dominant MEMS substrates, but SOI, quartz, glass, and polymer substrates are all finding more applications too.

The last talk of the day was worth the wait, with Tuomas Waris of Finland's Imbera Electronics presenting "Further Miniaturization Utilizing IMB Technology." Waris gave some background on Imbera's integrated module board (IMB) technology for embedding active components in substrates. He had some of the same messages as Verdant's Fjestad - high design freedom, no custom materials, very high yield, supply chain integration - and he also showed approaches for EMI shielding, thermal performance, and package-on-package stacking with Imbera's substrates. Imbera's technology was introduced five years ago, but it seems to be getting more attention now with others investigating the embedded approach.

|                                                                                                                                         | kages, Assembly & Prototype Ser                                                                                                            |                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                         | Assembly Solutions in 24                                                                                                                   | 11/11/                                                                                                                                     |

| Wafer Official of State         Backgrinding to State         Wafer Official of Including MPW         Die sort via wafer map or ink dot | Unimited Plastic Package Types         Δatest packages including dual         tow MLF, DFN, μBGA, etc         Marken District Package Ages | Assembly Services<br>Plastic or ceramic<br>Sold wire bonding<br>Stacked die, MEMS, etc<br>Banding to JEDEC spec<br>Branding<br>BGA Balling |

| 10987 Via Fr                                                                                                                            | ontera • San Diego, CA 92127 • 858-674-4676 • Fax 8<br>a division of Delphon                                                               | 858-674-4681                                                                                                                               |

## Made Industry Analysis

## Laminate Substrates Lead the Growth in the Semiconductor Packaging Materials Market

E. Jan Vardaman - TechSearch International, Inc. Dan Tracy - SEMI

riven by performance and form factor requirements, semiconductor packaging is now recognized as one of the most important factors in the growth of advanced packages. Materials are key to the success of semiconductor packaging for today's devices as well as future products.

The market for semiconductor packaging materials, including thermal interface materials, is expected to reach \$15.5 billion in 2007 and grow to \$20.2 billion by 2011, according to a new study by SEMI and TechSearch International. Laminate substrates remain the largest segment of the market, worth an estimated \$6.2 billion globally in 2007, and on a unit basis are projected to grow at a compound annual growth rate of over 12 percent over the next five years. Table 1 shows the semiconductor packaging materials market by segment.

#### Importance of Laminate Substrates

Laminate substrates represent a large dollar value today, more than double the value of the leadframe market. While the number of units for leadframe packages remains larger that the number of laminate substrates, the complexity and type of materials used make the value greater in the laminate segment. This has not always been the case. Historically ceramic substrates and leadframe substrates were major choices for IC packages. The transition to organic laminate substrates has been driven by the shift from the era of ceramic packages to the plastic ball grid array (PBGA). Motorola and Citizen Watch share the early patent for the over molded pad array package (OMPAC), the first PBGA. Motorola first adopted the package in two-way radios and pagers. Disk drive applications followed with a major push from Compaq (now part of Hewlett-Packard). As CSP enabled the introduction smaller, lighter mobile phones, the volume of laminate-based CSPs also increased.

Intel's shift from ceramic to lami-

nate substrates for its central processing unit (CPU) microprocessors facilitated this migration to organic substrates by providing a volume application that enabled the technology to mature faster for flip chip applications.

Personal computers (desktops, servers, and laptops) remain the largestvolume application for BGAs – almost exclusively for plastic BGAs (PBGAs). Game machines such as Sony's PlayStation, Microsoft's Xbox, and Nintendo's DS and Wii systems use PBGAs for processors and graphics chips. Computers, network systems, and telecommunications equipment remain the major applications for high-pin-count BGAs.

Mobile phones remain the major driver for growth in CSP unit shipments and laminate substrates are commonly used. Consumer products such as watches, digital camcorders and cameras, PDAs, DVDs, MP3 players such as Apple's iPod, games, and flash memory cards also use laminate CSPs. Laminate CSPs in mobile phones typically contain package pin counts range from 32 balls to 399 balls. Today's camcorder may contain 10 or more CSPs.

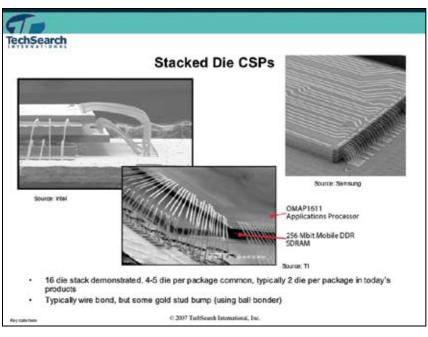

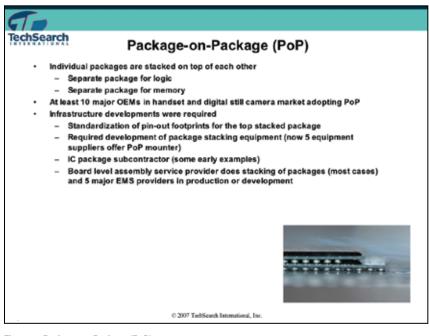

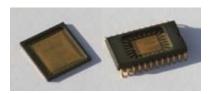

Stacked die packages have been common for many years, with as many as five die found in production today. While the two-die stacks are very common, die stacks with many more die are increasingly common (see Figure 1). These packages typically use laminate substrates. Mobile phones from companies including Apple, Motorola, Nokia, and Samsung use package-on-package (PoP). The PoP features two laminate substrates in each package (see Figure 2).

DRAM has made the transition from wire bonded leadframe-based packages (TSOPs) to wire bonded laminate CSPs (FBGA). With increased demand for memory, shipments of laminate substrates will grow dramatically.

#### **Flip Chip Laminate Substrates**

Within the laminate substrate market, high-density substrates for flip chip represent a large share of the dollar value. The availability of flip chip substrates is key to the growth of flip chip for many applications.

| Semiconductor Packaging<br>Materials Segment | Estimate of 2007 Global Market<br>\$M |  |  |  |

|----------------------------------------------|---------------------------------------|--|--|--|

| Laminate Substrates                          | \$6,196.0                             |  |  |  |

| Flex Circuit/Tape Substrates                 | \$262.5                               |  |  |  |

| Leadframes                                   | \$3,118.0                             |  |  |  |

| Bonding Wire                                 | \$3,178.3                             |  |  |  |

| Mold Compounds                               | \$1,371.0                             |  |  |  |

| Underfill Materials                          | \$138.0                               |  |  |  |

| Liquid Encapsulants                          | \$117.0                               |  |  |  |

| Die Attach Materials                         | \$562.2                               |  |  |  |

| Solder Balls                                 | \$265.0                               |  |  |  |

| Wafer Level Package Dielectrics              | \$9.8                                 |  |  |  |

| Thermal Interface Materials                  | \$303.0                               |  |  |  |

Table 1. Semiconductor Packaging Materials Market.

Source: SEMI and TechSearch International, Inc.

The drivers for flip chip continue to be performance, on-chip power distribution, pad limited designs, and form factor requirements. Microprocessor makers and high-performance logic suppliers such as ASIC, field programmable gate array (FPGA), DSPs, chipset, graphics, and microprocessor makers are expanding their use of flip chip in package (FCIP).

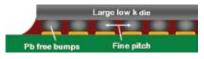

Driven by form factor, many wireless products are adopting flip chip interconnect. To achieve small package body sizes, an increasing number of companies use flip chip inside the package, especially for the bottom die in a package of a PoP. Flip chip also provides a reduction in pitch for the top package of a PoP, and improved electrical performance for devices such as baseband processors by delivering power directly to the processor core, along with reduced IR drop and reduced EMI. There are examples of both gold stud bump and solder bump in production today.

While the shift to flip chip and WLP did not materialize in high volume for DDR2 DRAM, performance requirements are expected to generate a shift in interconnect methods from wire bond to bumps for some high-performance DDR3 and DDR4.

#### **Substrate Supply and Demand**

Laminate substrate suppliers include Access (formerly AMITEC), ASE, CMK, Dai Nippon Printing, Daisho Denshi, Eastern, Endicott Interconnect Technologies, Fujitsu Interconnect, Hitachi Chemical, Ibiden, JCI, Kinsus, Kyocera, MicroCircuit Technology, Mitsui Chemicals, Nan Ya PCB, NEC Toppan Circuit Solutions, NTK, Phoenix Precision Technology (PPT), Ryowa, Samsung Electro-Mechanics, Samsung Techwin, Shinko Electric Industries, SMIED Globetronics Technology Industries (SGTI), a subsidiary of Sumitomo Metals Industries Electronic Devices, Sumitomo Metal Mining-Shinko, Tripod, and Unimicron.

IC package substrate production has transitioned from Japan to Taiwan and will slowly expand into China. Companies in Taiwan such as ASE, Kinsus, Phoenix Precision Technology, and Unimicron, have all expanded production capacity to meet growing demand.

The substrate shortage experience in 2005 has been replaced by an oversupply of capacity for 2-2-2 layer structures. This is the result of capacity expansion by companies in Taiwan in response to

Figure 1. Stacked Die CSPs.

Figure 2. Package-on-Package (PoP).

Intel's projected move from wire bond to flip chip for its ICH (Southbridge) chipset. The transition has been delayed, creating an over capacity situation. While there is no oversupply of more complex substrates, the industry has seen delivery times return to normal.

#### Conclusions

Laminate substrates will continue

to be a key enabler in advanced semiconductor packaging. Communications between suppliers of the raw materials for the substrate, substrates, semiconductor manufacturers and IC packaging assembly houses, and the system maker or assembly service provider are critical in maintaining the required infrastructure and supply chain to meet product demand.

## MEDIC Industry News

#### Indium's Corporate Communications Director Earns SMTA Award

Indium Corporation's Director of Corporate Communications, Rick Short, was honored with the Excellence in International Leadership Award by the Surface Mount Technology Association (SMTA) on October 10th, 2007. This award recognizes Rick's global achievements in the industry and his support of the SMTA over his career of nearly 25 years.

Since joining Indium Corporation in 1984, Rick has played an active role in the SMTA. He helped launch regional chapters in Australia and Malaysia, and has supported the SMTA's presence in China. Rick serves as a member of the SMTA Marketing Committee and the SMTAI Exhibitor committee.

JoAnn Stromberg, of the SMTA, commented "Rick has truly captured the meaning of our 'international excellence in leadership' award. His influence will benefit the SMTA for years to come."

Based at Indium's global headquarters in Clinton, NY, Rick is an innovator in his field. He has received the Pro-Comm Award for the world's first electronics assembly materials online video advertisement, titled "INDIUM CORPORA-TION: We Know SMT Inside and Out". He is the author of Rick Short's B2B Marcom blog on new media and businessto-business Marcom practices worldwide.

For more information about Indium Corporation visit www. indium.com or email abrown@ indium.com

#### Rudolph Technologies and Entrepix, Inc. Announce License Agreement

FLANDERS, NJ - Rudolph Technologies, Flanders, NJ, and Entrepix, Inc., Tempe, AZ, have announced that Rudolph has granted Entrepix an exclusive license to manufacture, sell, service and support the Rudolph AutoEL<sup>®</sup> series of thin-film ellipsometers. The AutoEL® was the first microprocessorbased automated ellipsometer and is recognized worldwide as a high-performance, highprecision instrument used in the measurement of film thickness. Thousands of AutoEL tools have been placed in universities, semiconductor research labs and semiconductor production lines since it was commercialized in 1977, with many of those tools in continuous use today. All systems to be sold will be labeled "Rudolph Technologies Auto $\mathrm{EL}^{\mathbb{R}}$  - provided and supported by Entrepix".

"The AutoEL technology was the foundation of our overwhelming success in thin-film metrology," said Paul McLaughlin, chairman and chief executive officer of Rudolph. "We are confident that Entrepix will continue to maintain the high level of support for this product that our customers have expected over the past thirty years."

Entrepix provides CMP process outsourcing and equipment services, including refurbishment of CMP, post-CMP cleaning and thin-film metrology equipment. Due to the complementary nature of Entrepix foundry and equipment capabilities, many semiconductor industry OEMs have authorized the company to exclusively refurbish, service and support pre-owned tools on their behalf.

Under the terms of the Agreement, the transfer of assets and inventory will be completed sometime in the fourth quarter. Entrepix is licensed to market the AutoEL on a global basis (excluding Japan) beginning immediately. All inquiries for the AutoEL received by Rudolph will now be redirected to Entrepix.

Headquartered in Flanders, New Jersey, Rudolph supports its customers with a worldwide sales and service organization. Additional information can be found on the company's website at www.rudolphtech.com.

#### BESI Announces Packaging and RFID Die Bonding Equipment Orders

DUIVEN, THE NETHER-LANDS – BE Semiconductor Industries N.V. (BESI) has announced the receipt of orders in October 2007 aggregating approximately \$4.3 million for packaging and die bonding equipment.

The Company's Fico subsidiary received an order of approximately \$2.8 million for four AMS-I molding systems and two Compact Line trim and form systems from a leading Chinese semiconductor manufacturer. The customer intends to utilize Besi's equipment for the packaging of SOT/SOD discrete devices in conventional leadframe process applications as part of their expansion of discrete production capacity. Delivery is scheduled for the first quarter of 2008.

Besi's Datacon subsidiary also received orders recently aggregating \$1.5 million for its 8800 FC ("Flip Chip") Smart Line die bonding system. Datacon's 8800 FC Smart Line system is a fully automated, highperformance production line providing customers a complete Radio Frequency Identification Device ("RFID") chip assembly solution based on a highly cost-effective method of direct chip attach to RFID antennae. The orders were placed by three global smart card manufacturers and are anticipated to be delivered in the fourth quarter of 2007.

For more information about Besi, please visit their website at www.besi.com.

#### MIG and MEPTEC Announce Strategic Alliance

PITTSBURGH, PA and MED-ICINE PARK, OK - MEMS Industry Group (MIG), the trade association representing the microelectromechanical systems (MEMS) and micro-structures industries, and the MicroElectronics Packaging and Test Engineering Council (MEPTEC) have announced a strategic alliance that will benefit companies designing and packaging MEMS devices. Through a variety of marketing programs, MIG and MEPTEC will collaborate to eliminate the barriers that prevent the greater commercial use of MEMS and MEMS-enabled technology.

"MIG and MEPTEC have complementary goals," stated Karen Lightman, Managing Director, MEMS Industry Group. "MIG is the unifying voice of the commercial MEMS industry, and MEPTEC is a trade association of semiconductor suppliers and manufacturers, committed to enhancing the competitiveness of the back-end portion of the semiconductor business. During the coming year, we will work together to address the packaging issues that can further enhance the adoption and commercialization of MEMS.'

"Packaging of MEMS devices holds special challenges in the semiconductor business," said Bette Cooper, President of the MicroElectronics Packaging and Test Engineering Council. "MEMS devices must withstand electromechanical, thermomechanical and other stressors and still remain robust and reliable. Bridging the gap between standard semiconductor packaging and MEMS packaging is one way to address these challenges, and it is this convergence that has been our focus."

Ms. Cooper added: "MEMS is the new wave of the future, and our collaboration with MEMS Industry Group will help us to further explore this promising technology."

Through their alliance, MIG and MEPTEC will support each other's upcoming events:

• MIG was a co-sponsor of MEPTEC Substrates Symposium - The Foundation of Semiconductor Packaging, Thursday, November 8, 2007, San Jose, CA;

• MIG will conduct a packaging survey of its members at its annual members-only technical event, METRIC (May 7-9, 2008);

• MIG will present findings of its packaging survey at MEPTEC's 6th Annual MEMS Symposium on May 22, 2008; and

• MIG and MEPTEC will cross-promote each other's events to their respective memberships.

For more information contact MIG at 412/390-1644, info@memsindustrygroup. org or visit www.memsindustrygroup.org.

Contact MEPTEC via email at info@meptec.org or visit www.meptec.org.

#### Intersolar Joins SEMICON West to Form North America's Largest Solar Technology Exposition

SAN JOSE, CA – SEMI, along with Freiburg Wirtschaft Touristik und Messe GmbH & Co (FWTM) and Solar Promotion GmbH, organizers of Intersolar, the world's largest trade fair for solar technology, have announced a partnership to host Intersolar North America. The new exposition will be the largest trade event serving the full solar energy supply chain in the United States, and will be held at the Moscone Center in San Francisco on July 15-17, 2008, in conjunction with SEMICON West, the world's first and most prestigious industry event dedicated to microelectronics manufacturing.

Intersolar, held in Munich, Germany, has become the world's largest trade fair for solar technology and focuses on the areas of photovoltaic technologies, solar thermal technology and solar architecture. Currently, SEMI organizes a range of PV-related events including PVJapan, the PV Fab Managers Forum and PV-focused technical events at major expositions such as SEMICON Taiwan, SEMICON China, SEMICON Europa, and SEMICON West. This agreement comes as a response to the rapid expansion of solar energy markets worldwide and the need for cooperation between all the major industry participants to serve the increasingly global supply chain and customer base.

Intersolar North America will address the entire supply chain in solar energy including solar thermal energy and PV. Exhibitors will include PV cell, module and inverter manufacturers, polysilicon suppliers, equipment and material suppliers, components and subsystems, manufacturers of solar thermal applications for heating, process heat and cooling as well as architectural/construction services. Intersolar North America will be a co-located event with SEMICON West, occupying portions of the West Hall of Moscone Center. Registered visitors to SEMICON West and Intersolar will be able to attend the exhibition part of both events without additional fees or separate badges. Following the successful format of Intersolar Europe, a 1.5-day conference on PV technology and solar thermal energy will be held as part of Intersolar North America, requiring a separate conference fee.

For more information about Intersolar visit their website at www.intersolar.us.

For more information about SEMI visit www.semi.org.

Looking for the best insurance against flip chip defects?

An example of an actual Sonoscan C-SAM® acoustic scan showing a flip chip with die cracks and delamination defects.

## **Demand Sonoscan**

Cracks, voids and delaminations can elude electrical tests. And if left undiscovered, they may result in costly production shutdowns, quarantined products and very disappointed customers.

Sonoscan systems are widely relied upon for nondestructive inspection. Using the most advanced acoustic technology available, Sonoscan accurately locates and analyzes these hidden defects—*before* they lead to failures.

#### **Packaging Applications**

- Plastic Encapsulated IC

- Die Attach

- Flip Chip

- Stacked Die

- Smart Card

- Chip Scale Package

- and many others

To learn more about Sonoscan systems and AMI technology, visit www.sonoscan.com

Sonoscan—trusted for over 30 years by the industry's leading companies.

Sound Technology With Vision

800-950-2638 • 847-437-6400 • www.sonoscan.com Santa Clara, CA • Scottsdale, AZ • Elk Grove Village, IL • Burlington, MA England • Philippines • Hong Kong • Taiwan • Singapore • Shanghai

# IMAPS Presents the Fourth International **Device Packaging**

## **Conference & Exhibition**

(www.imaps.org/devicepackaging)

### Exhibits: March 18 - 19, 2008 Conference & Events: March 17 - 20, 2008

co-located with

Global Business Council Spring 2008 Meeting: March 16 & 17 (www.imaps.org/gbc)

> Raddisson Fort McDowell Scottsdale, AZ

**General Chair:** Larry Jacombsen, JH Technologies

MAPS

Sponsored by:

International Microelectronics And Packaging Society (IMAPS) www.imaps.org/devicepackaging

"Everything in electronics between the chip and the system!"

## MEDIC Industry News

#### Asymtek Introduces Select Coat SL-940 Conformal Coating Platform

CARLSBAD, CA – Asymtek has introduced its next generation conformal coating platform, the Select Coat<sup>®</sup> SL-940E. With up to 30 percent faster throughput, a vision system, closed-loop process controls, traceability, and advanced integrated software, the Select Coat SL-940 provides high quality and increased productivity in a high-speed, high-accuracy coating system.

With the Select Coat SL-940E, advanced monitoring makes it easier to keep the coating process in control. Fluid and air pressures are set and monitored through softwarecontrolled electronic regulators, allowing traceability for these critical parameters. Data logging and automatic adjustments of other parameters such as fan widths, fluid temperatures, and flow rates, further ensure the quality of the coating process.

The new, faster motion system of the SL-940E unleashes the performance capability of Asymtek's SC-104/204 Film Coater applicator, attaining 750 mm per second speed and 1g peak acceleration. It accommodates product sizes up to 500 mm for higher speed and faster cycle times.

The SL-940E has a large dispense area of 500 x 475 mm (19.7 x 18.7 in.). The enlarged work area enables flexibility during production to add multiple board arrays or to coat large substrates. Programming is made easier with the optional camera and pattern recognition system. The controls of popular options like Asymtek's Laser Fan Width Control, Viscosity Control System, Bar Code System, and Flow Monitoring have been fully integrated within the machine for a more seamless operation.

For more information visit Asymtek's website at www. asymtek.com.

#### IMEC Extends Its CMOS Device Scaling Program

LEUVEN, BELGIUM – IMEC launches research on nextgeneration DRAM MIMCAP (metal-insulator-metal capacitors) process technology as part of its (sub-)32nm CMOS device scaling program. This research will enable IMEC and its partners to address the material and integration requirements to scale DRAM MIMCAP to future technology generations. This newly added focus follows an earlier extension of its traditional logic- and SRAM-oriented program with a DRAM periphery transistor sub-program in November 2006. The objective of the latter sub-program is to

- Quick-turn and mass-production

- Highly competitive, low-cost bumping technology

- Exceptional quality through high-level expertise

#### PAC TECH

Pac Tech GmbH Tel: +49 (0)3321/4495-100 sales@pactech.de www.pactech.de

#### Pac Tech USA

Tel: 408-588-1925, ext. 202 sales@pactech-usa.com www.pactech-usa.com

Pac Tech Asia Sdn. Bhd. Tel: +60 (4) 6430 628 sales@pactech-asia.com www.pactech-asia.com

#### THE WORLD OF NAGASE

Tel: +81-3-5640-2282 takahiro.okumura@nagase.co.jp www.nagase.co.jp

#### **Available Processes**

- Electroless Ni/Au under-bump metallization

- Ni/Au bump for ACF or NCP assembly

- Solder paste stencil printing

- Solder ball drop for wafer-level CSP

- Solder jet for micro-ball placement

- BGA and CSP reballing

- Wafer backside thinning and wafer dicing

#### **Special Features/Technologies**

- Over 10 years experience

- U.S. Government Certified

- 4- to 12-inch wafer capability

- Wafer pad metallization: Al and Cu

- Solder alloys: eutectic SnPb37, lead-free, low-alpha, and AuSn

- Fluxless and contactless bumping for MEMS and optoelectronics

- Ni/Au interface for wire-bond applications

The leader in low-cost electroless wafer bumping.

## MELLE Industry News

research high-k and metal gate options sustaining a

DRAM-oriented process flow. In order to scale DRAM towards the 50nm node and beyond, MIMCAP dielectrics require materials with a higher dielectric constant compared to current industrial materials such as ZrO2. By mid 2008, an effective oxide thickness of 0.5nm is targeted for the MIM-CAP dielectric in the sub-50nm technology node, going down to 0.3nm in 2009 for the sub-45nm node. Scaling the dielectric equivalent oxide thickness while attaining very low leakage currents is one of the major bottlenecks DRAM industry is facing.

Building on its expertise in high-k dielectrics and memory research, IMEC expands its CMOS device scaling program to address these challenges.

Further information on IMEC can be found at www. imec be

#### Rohm and Haas **Purchases Coating Cluster** from SUSS

MUNICH - SUSS Micro-Tec has announced that it has received the first order for its new Gamma XPress coat/ develop cluster from Rohm and

Haas Electronics Materials, a world leader in the development and manufacture of electronic materials for the semiconductor markets. The system from SUSS MicroTec will be used by Rohm and Haas Electronic Materials to develop, characterize and optimize photodielectrics and both thick and thin photoresists. The SUSS Gamma XPress was chosen over alternative equipment due to its superior thick resist processing capability and its bridge tool design that permits concurrent handling of wafers with different sizes without mechanical changeover.

nology like InterVia<sup>™</sup> photoresists and photodielectrics to market requires our development labs to work with next generation processing equipment", says Mike Toben, Global R&D Director for Rohm and Haas Electronic Materials, Packaging and Finishing Technologies "Our goal in selecting a new coating cluster was finding a system with the combination of high throughput and state-ofthe-art control, and we believe we have found that with the new Gamma XPress. The SUSS MicroTec tool will significantly enhance our R&D and customer modeling capabilities."

"Bringing leading edge tech-

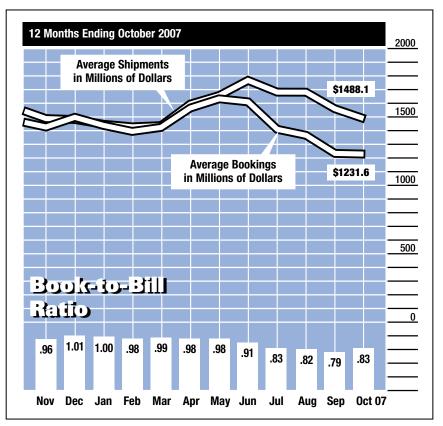

## North American Semiconductor Equipment Industry Posts October 2007 Book-To-Bill Ratio of .83

SAN JOSE, CA - North American-based manufacturers of semiconductor equipment posted \$1.23 billion in orders in October 2007 (three-month average basis) and a book-to-bill ratio of 0.83 according to the October 2007 Book-to-Bill Report published by SEMI. A book-to-bill of 0.83 means that \$83 worth of orders were received for every \$100 of product billed for the month.

The three-month average of worldwide bookings in October 2007 was \$1.23 billion. The bookings figure is flat with the final September 2007 level of \$1.24 billion and 16 percent less than the \$1.47 billion in orders posted in October 2006.

The three-month average of worldwide billings in October 2007 was \$1.49 billion. The billings figure is about four percent less than the final September 2007 level of \$1.56 billion and about five percent less than the October 2006 billings level of \$1.56 billion.

"Actual sales of new semiconductor equipment have generally followed the bookings trends, which have declined sequentially since the cyclic peak in early summer," said Stanley T. Myers, president and CEO of SEMI. "However, our expectation remains that 2007 equipment revenues will remain comparable to or slightly above 2006 sales."

three-month moving average bookings to millions of U.S. dollars. three-month moving average shipments.

The SEMI book-to-bill is a ratio of Shipments and bookings figures are in

## PAN PACIFIC

## Microelectronics Symposium and Tabletop Exhibition

#### 22 - 24 JANUARY 2008, SHERATON KAUAI RESORT

The Pan Pacific Symposium focuses on the critical business markets and technologies of microelectronic packaging, interconnection, microsystems technology and assembly.

The Pan Pacific Tabletop Exhibition puts you in contact with global key decision makers and provides access and international visibility for your company and products.

#### SPONSORED BY

www.smta.org | 952-920-7682 | smta@smta.org

## Maine Member Company Profile

he ASE Group was established in 1984 as a semiconductor assembly company headquartered in Taiwan. Over the course of 23 years, ASE has gradually evolved into a \$3.1 billion company, offering a broad range of services including IC packaging, test, material, with complete turnkey capabilities. Manufacturing was initially carried out in Taiwan, and later expanded into seven countries spread over four continents. From an original employee headcount of just one hundred, ASE now employs over 28,000 people worldwide.

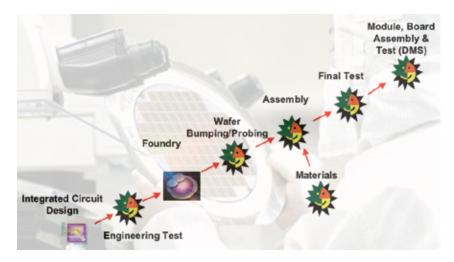

Today, ASE has achieved market leadership, and is the world's largest provider of independent semiconductor manufacturing services in assembly and test. With key customers spanning the consumer, computing, and communication sectors, ASE serves both the IDM and Fabless communities, to meet the electronic industry's growing need for faster, smaller, and higher performance semiconductor chips. The development of highperformance electronic products has spurred the innovation of semiconductor packages that have higher interconnect density and better electrical performance. As part of this technology migration, semiconductor packages have evolved from leadframe-based packages to substrate-based packages. The key differences of these package types are the size of the package; the density of the electrical connections the packages can support; and, the thermal and electrical characteristics of the package.

ASE's vast package portfolio meets existing and emerging market needs for both leadframe and substrate-based packages. To address increased pin counts, ASE has developed innovative packaging solutions with reduced footprint and higher electrical performance. Their leadframe-based package family includes offerings such as QFP and QFN that are packaged by connecting the die, using wire bonders, to the leadframe

with gold wire. ASE is the industry leader in fine-pitch wire bonding with the world's largest capability. The company also holds patents for tri-tier fine-pitch technology, and is ramping up quad-tier capabilities. In addition, ASE currently has more than 5,000 wire bonders in service, of which over 3,400 have fine-pitch bonding capabilities.

ASE's substrate-based package family generally employs the BGA design which utilizes a substrate rather than a leadframe. BGA package types place the electrical connection at the bottom of the package surface in the form of small bumps or balls, and benefits include smaller package size, higher pin-count, greater reliability, superior electrical signal transmission, and, better heat dissipation. BGA packages available from ASE include flip chip BGA, flip chip CSP, and wire bond BGA family groups covering die combination and package combination. Die combination packages include MCM BGA and Stacked Die Package (SCSP), while package combinations include Multi Package BGA (MPBGA) and Stacked Package BGA (SPBGA), such as Package-in-Package (PiP), System-in-Package (SiP), Package-on-Package (PoP), and so on.

ASE Singapore

ASE Shanghai, China (A&T)

ASE Shanghai, China (Substrate)

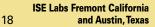

#### **ASE'S ROLE IN THE MANUFACTURING VALUE CHAIN**

ASE is the only assembly and test service provider with a sizable substrate operation. And with substrates becoming an increasingly important factor in the IC packaging process, customers are able to significantly reduce their costs and their cycle times by taking advan tage of ASE's state-of-art inhouse substrate capabilities. ASE has the capacity to supply laminate substrate for wire bonding innovations, as well as the build-up substrate for flip chip technology.

ASE is the clear leader in test service market share, front-end engineering test, multiplatform testing and test program conversion. They maintain more than 1,200 test systems, including the Agilent 93000, Teradyne Tiger, etc, and are also the largest probing service provider with a capacity approaching 80,000 wafers per month. ASE Group member ISE Labs has the largest engineering test customer base in Silicon Valley.

Rounding out ASE's complete service solution set are turnkey Design Manufacturing Services (DMS) – the final step that brings customers sub-assemblies to the marketplace. Again, ASE facilitates lower costs and shorter cycle times by deploying their module capabilities in Shanghai and Shenzhen, China, close to major manufacturing centers.

ASE's turnkey services provide customers a one-stop manufacturing solution, ultimately lowering overall costs and speeding time-to-market.

#### **Focus on China**

As ASE enters its next evolution of growth, the company is focused on expand

ing its commitment in a number of areas, particularly the China market. Strategically positioned within China's electronics cluster, ASE's newest facilities are located in the Greater Shanghai area - Zhangjiang and Kunshan - and are aimed at providing cost-effective IC manufacturing services to customers requiring supply chain support within the region. Operations commenced in 2005, as the first substrate manufacturing company in China. Today, ASE is the largest PBGA substrate supplier and continues to expand its business and product offerings. China, with its abundant resources and booming infrastructure, will be the next engine of growth for ASE. In 5 years' time, ASE estimates that its China operations will account for 50% of its total revenues. The company expects this steady growth to propel it to achieve total Group revenue of \$24B by 2013.

ASE has its customers' interests in mind as it responds to the continuing evolution and domination of the consumer market. Investing in strategic areas, such as China, and in particular the China infrastructure is a priority. The ASE facility in Zhangjiang, occupies 190,000 square meters of production facilities and has an employee population of 7,000. ASE plans to acquire another 200,000 square meters of land which is scalable to employing 54,000 people. Leveraging on China's vast consumer market and human capital, ASE devised a massive infrastructure development program offering customers low cost manufacturing, and a skilled, disciplined workforce including highly educated engineers and technicians from universities across the country.

To build a stronger foundation in its China operations, ASE carefully considered the needs of its employees who are relocated from other areas in China. ASE constructed dormitories on a 100,000 square meter land, within proximity of its production facilities to house 6,000 employees. By 2008, ASE will complete another housing project on a land space of 100,000 square meters, and a future expansion of another 200,000 square meters, offering accommodation for 30,000 employees. The Mainland Chinese government's strong support for business investments and people development, complements ASE's vision to serve customers with quality products and services.

With the China economy registering near double-digit growth, Shanghai is thriving and has established itself as the Chinese capital of commerce, industry, finance, and technology. Their new manufacturing facilities are located close to Shanghai Pudong airport and Shanghai's metro system, which is one of the world's newest, most rapidly expanding subway systems.

The China-based facilities are complementary to ASE's existing manufacturing facilities. In fact, ASE China serves as an operational unit of ASE factories in Korea, Japan, and Kaohsiung, Taiwan, providing additional capacity and services to meet growing customer needs.

The scale of ASE in China has enabled the company to embark on an expansion of its service offerings by including low pin count and discrete IC packaging and test into its portfolio. Leveraging on its manufacturing expertise, land and business operations, ASE will offer customers large scale and low cost manufacturing capacity. With an operational unit comprising skilled engineering and logistical teams, ASE China is well-prepared to assist and service customers, making their manufacturing experience in China as smooth as possible. Key to ASE's ongoing success is a steadfast commitment to support capacity ramp-up, while constantly improving cost structure and productivity.

The electronics industry landscape is undergoing major changes, in terms of consolidation, innovation, and China market growth, and ASE is transforming itself to better serve customers and positively impact the future of the electronics industry.

The ASE Group welcomes all to learn more about their China initiative, visit their facilities, and engage their local engineering teams. Go to www.aseglobal.com for more information about the ASE Group. ◆

ASE ChungLi, Taiwan

ASE Takahata, Japan

ASE Paju, Korea

ASE Penang, Malaysia 19

## MEDIEC SiP Technology

### A Low Cost Alternative to Thru Silicon Via Can Packaging Technology Provide the Missing Link?

#### Marc Robinson Vertical Circuits, Inc.

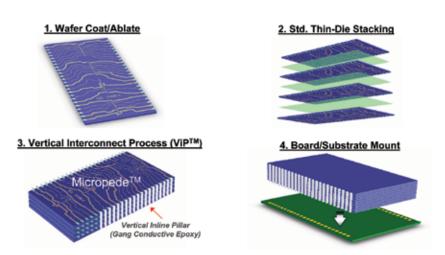

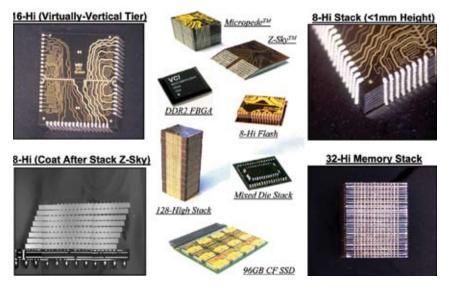

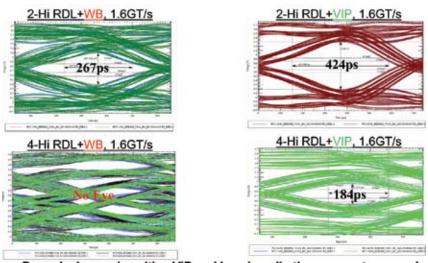

ecently there has been much interest focused on TSV (thru-silicon via) technology as a solution to a number of problems facing the electronics industry as we endeavor to continue increasing product complexity while simultaneously reducing cost. Essentially a front-end solution, TSV requires expensive equipment, and much process development, before it can be considered ready for reliable, low cost manufacture. Vertical Circuits (VCI), however, sees the solution remaining in the back end, through the use of virtual vias at the peripheral edges of the die stack, which offer a low cost, production ready solution today.

#### Why 3D?

Relentless increases in electronic product complexity has been fueled over the last half century by the semiconductor ind eature size shrinks, which occur approximately every 18 months, dutifully obeying Moore's law. Accompanied by significant reductions in cost, the increase in useable transistors per square millimeter, has brought many new products within financial reach of the average consumer, including cell phones, digital music players, digital cameras, and personal digital assistants, just to name a few. However, there are clouds on the horizon, as the cost of continuing along this 2-dimensional shrink path become too burdensome for all but the largest global corporations to bear.

There has always been strong interest in 3D solutions for increasing density, and improving performance. Small printed circuit boards have been stacked above other circuitry as daughter cards, and packaged devices have been stacked as well, especially for memory applications. Of late, there has been strong interest in moving the stacking focus from packaging and assembly based solutions into the wafer fabrication area to allow an "orders of magnitude" increase in the number of vertical interconnections, and hence creating significantly higher functional chip densities without the need to continue

#### A Voracious Appetite for High-Density 3D Integration

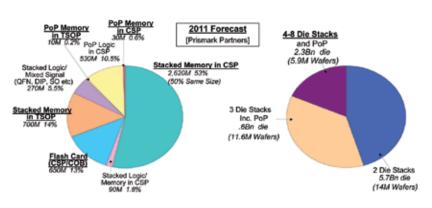

Figure 1. Market Drivers for 3 D Integration.

Over <u>50%</u> of Semiconductor Industry revenue now comes from <u>Memory</u>.

Of the 5yr forecast for stacked die, <u>75%</u> (4B units) is expected from <u>Memory-Only</u> stacks,

Approximately <u>60%</u> of this (2.5B units) is expected to be <u>Same-Size Memory</u> die stacks.

<u>25%</u> of these die will end up in <u>4+Die</u> stack configurations.

<u>Does the Industry have ALL the NECESSARY TOOLS in the TOOLBOX?</u>

Figure 2. The Overall 3D Market.

with relentless feature size reduction. As a wafer fab focused technique, "through silicon via", or TSV as it is known, is the key technology at the core of most wafer fabrication focused 3D solutions. TSV entails the use of complex wafer processing steps, and hence the use of very expensive wafer processing equipment, to create vias from the front side to the back side of the die. Due to the expense and complexity, TSV application is likely to be limited to the highest volume applications, and practiced by companies with the deepest pockets.

It is clear from market forecasts, that there is a voracious appetite for high density 3D integration driven by the need to put more functionality in a single package. (Figure 1) Applications abound in cell phones, portable music players, digital cameras, PDAs, and other consumer applications. Today, many such applications are addressed by stacked die packages utilizing wirebonds for interconnection of multiple die to a single substrate and by Package on Package solutions (PoP) solutions.

With all the hype surrounding TSV, one might conclude that stacking is about to move from the assembly house to the foundry, and will soon become a wafer processing "game". However, with forecasts showing that 75% of the stacked die products are likely to be memory-only stacks, (Figure 2) one must question if there is a missing link in the industry's 3D integration roadmap for the vast majority of the expected applications which will need more than today's packaging solutions can provide, but do not need the high number of vertical interconnections which are provided by TSV. We must ask ourselves if the semiconductor industry has all the necessary tools in the toolbox to address the growing 3D demand, and if some of those capabilities can be cost effectively provided by a packaging based solution.

#### The Laws of 3D SiP

Performance, form-factor, cost, and adoptability have always been the key attributes a technology must satisfy to be viable in the marketplace. Simply stated, any new technology must be a better mouse trap, or there will be no customer interest. (Figure 3)

Beyond the basic performance questions embodied by the question "Does it work?" the vertical interconnects must exceed the applications' electrical and routability requirements, the process must be robust as demonstrated by CpK data, and products must pass appropriate reliability and quality tests for the intended application.

From a form-factor perspective, the technology must enable significant increases in circuit densities, and be able to scale to support ever greater interconnect and die counts. For example, while 2 high stacks for DRAM memory cards

#### PERFORMANCE: "Better"

- · Does it Work? How Robust is the Process CpK Data?

- · Do the Interconnects Exceed the Market's Electrical & Routability Requirements?

- · Does the Product Pass Reliability Testing in its Applied Configuration?

#### FORM-FACTOR: "Smaller"

- Does the Technology Enable Much Greater Silicon Density (e.g. Gb/mm<sup>3</sup>)?

- · Does the Technology Easily Scale to Much Greater Interconnect & Die Counts?