A Publication of The MicroElectronics Packaging & Test Engineering Council

#### **INDUSTRY NEWS**

**SEMI** has announced the appointment of Jerry Coder as chairman of the industry association's International Board of Directors. The results of the association's annual elections were announced at the annual SEMI membership meeting, held during the SEMICON West 2007 exposition in San Francisco. *page 12*

**Precision Process Equipment**, a designer and manufacturer of custom plating and wet processing equipment, has opened a technical center in Boise Idaho. *page 13*

**Microbonds Inc.**, Mirror Semiconductor Inc., and **PROMEX Industries Inc.**, will blend their existing processes, products and expertise to develop advanced IC packaging. *page 14*

**Sonoscan** has unveiled the new D-9500<sup>TM</sup> update of its popular C-SAM<sup>®</sup> acoustic microscope system. The contemporary D-9500 replaces the widely used "gold standard" D-9000 system in Sonoscan's line-up, and like the D-9000 excels in failure analysis, product development, material characterization and low-volume production. *page 16*

RTI's 2007 Technology Venture Forum comes to the Hyatt Regency San Francisco Airport Hotel in Burlingame, CA on October 22 - 24. page 27

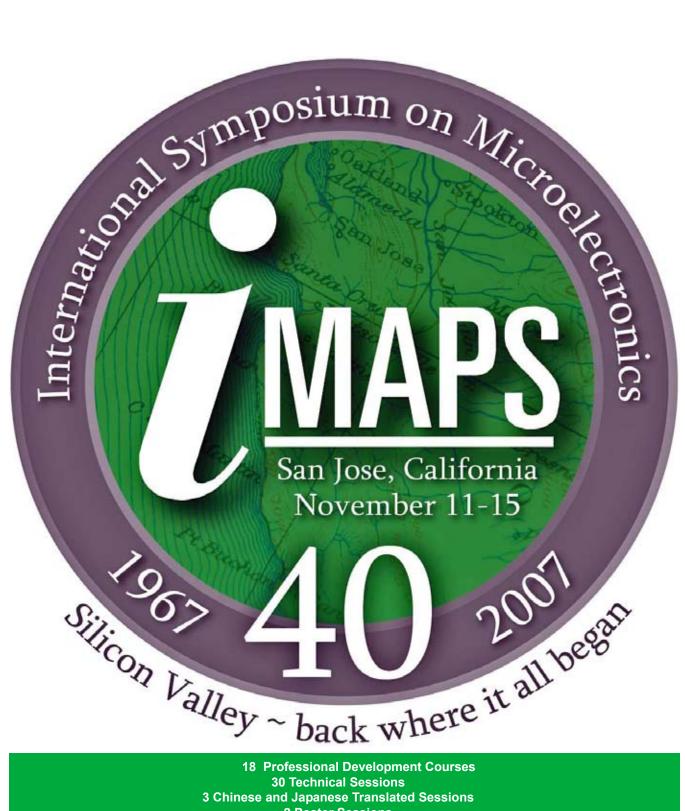

# Substrates: The Foundation of Semiconductor Packaging

One Day Technical Symposium and Exhibits Coming to San Jose November 8th ... page 5

#### **MEMBER COMPANY PROFILE**

United Test and Assembly Center Ltd. (UTAC) is a leading independent provider of test and assembly services for a wide range of semiconductor devices that include memory, mixed-signal/RF, analog and logic integrated circuits. UTAC offers full turnkey services that include wafer sort/laser repair, assembly, test, burn-in, mark-scan-pack and drop shipment, as well as value added services such as package design and simulation, test solutions development and device characterization, failure analysis, and full reliability test. page 18 ounded in November 1997, UTAC began full operations in January 1999. The Group is head-

quartered in Singapore, with seven manufacturing facilities in Singapore, Taiwan, China, and Thailand and sales operations in the US, Europe, and Asia. As of December 2006, UTAC employees number approximately 8,500.

Semiconductor equipment billings increase 4% over July 2006 level. *page 16*

# innovation

Finding new ways to solve problems—whether it's new obstacles that arise or the usual process challenges—we're here to offer a unique combination of strengths.

Recent example: our award-winning printable phase change material. Honeywell's ongoing research and development in chemistry, metallurgy, and the processes that bring them together—from our new packaging

R&D facility in Spokane, Washington, to our technology center in Shanghai, China—ensure that wherever challenges arise, we'll continue to create solutions that solve them. And as a partner to most of the top semiconductor houses worldwide, our technology portfolio is consistently at the forefront of invention, empowering the global leaders of innovation. Honeywell Electronic Materials—helping the manufacturers of today navigate the future.

# Honeywell

Contact Honeywell for solutions to your puzzle... visit www.honeywell.com/sm/em or call 1-408-962-2000.

Volume 11, Number 3 A Publication of The MicroElectronics Packaging & Test Engineering Council

P. O. Box 222 Medicine Park, OK 73557 Tel: (650) 714-1570 Email: info@meptec.org

> Published By MEPCOM

Editor Bette Cooper

Design and Production Gary Brown

Sales and Marketing Kim Barber

Contributing Editor Jody Mahaffey

#### **MEPTEC Advisory Board**

Seth Alavi SunSil Jeffrey Braden sors. Inc **Philippe Briot** P. Brid loel Camarda Sipex Corporation Gary Catlin Plexus Tom Clifford Rob Cole John Crane J. H. Crane & Associates Jeffrey C. Demmin Tessera **Bruce Euzent** Altera Corporation Skip Fehr Julia Goldstein Advan ced Packaging Magazine **Chip Greely** Oualcomm Anna Gualtieri Elle Technology Lan Hoang Xilinx Bance Hom Consultech International, Inc

Ron Jones N-Able Group International Pat Kennedy

Gel-Pak Nick Leonardi

CMC Interconnect Technologies Phil Marcoux

TLP Group Bhavesh Muni

Henkel Corporation Mary Olsson Gary Smith EDA

Marc Papageorge Semiconductor Outsourcing Solutions

Rich Rice ASE (US) Inc. Jim Walker Gartner Dataquest Russ Winslow Six Sigma

MEPTEC Report Vol. 11, No. 3. Published quarterly by MEPCOM, P. O. Box 222, Medicine Park, OK 73557. Copyright 2007 by MEPTEC/MEPCOM. All rights reserved. Materials may not be reproduced in whole or in part without written permission.

MEPTEC Report is sent without charge to members of MEPTEC. For non-members, yearly subscriptions are available for \$75 in the United States, \$80US in Canada and Mexico, and \$95US elsewhere.

For advertising rates and information contact Kim Barber, Sales & Marketing at 408-309-3900, Fax 1-866-424-0130.

elcome to our Q3 issue, and to the official end of summer, and time to kick off our monthly luncheon presentation series in September after a two month summer hiatus. MEPTEC Advisory Board member **Jim Walker** of **Gartner-Dataquest** has presented on the state-ofthe-industry at these kick-off luncheons for many years, and this year is no different. On September 6 in Phoenix and September 13 in Sunnyvale, Jim spoke on "Semiconductor Packaging: Leading the Shift in Semiconductor Cycles". For a copy of this presentation please contact the MEPTEC office.

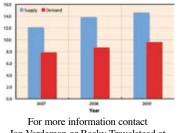

Our Industry Analysis this issue is also from our supporters at **Gartner-Dataquest**. **Mark Stromberg** and **Bob Johnson** write on the state of the semiconductor packaging and assembly equipment market, stating that the industry will face a lull in demand in '07, with modest growth expected for '08 (see page 6).

By the time you read this we will just have finished up our 2nd Annual Medical Electronics Symposium, with an emphasis on growth opportunities in the microelectronics industry. This was our second event outside Silicon Valley's borders and was again held in association with Arizona State University and MacroTechnology Works at ASU. ASU hosted the event at the historic Old Main building on the Tempe campus. We'd like to thank ASU for their great support in putting this event together. If you missed the event, our Q4 issue will contain a follow-up of the symposium, and a CD of the presentations will be available – just contact MEPTEC for information on ordering.

For our University News section this issue we cover the Materials Science and Advanced Packaging curriculum at Boise State Univer-We'd like to thank long-time MEPTEC sity. Advisory Board member Gary Catlin of Plexus Electronic Assembly in Idaho for introducing us to this impressive college. Boise State's microelectronics packaging research is a centerpiece of their undergraduate and graduate offerings. They state that unlike many engineering colleges in the nation where enrollment is declining, Boise State's enrollment is increasing rapidly for many reasons...check out their story on page 8. Thanks to Dr. Amy Moll and Patricia Pyke at Boise State University for this interesting report.

This issue is being distributed at our Q4 oneday technical event being held on November 8, 2007 at the Holiday Inn San Jose Hotel in San Jose, California. The event is entitled "Substrates: The Foundation of Semiconductor Packaging". We'd like to thank Advisory Board members Joel Camarda of Sipex, Rich Rice of ASE (US), Tom Clifford (formerly of Lockheed-Martin), Bruce Euzent of Altera, Lan Hoang of Xilinx and Bhavesh Muni of Henkel Corp. for their support as committee co-chairs and session leaders of this event. Again, if you missed the event, our Q4 issue will contain a summary of the symposium, and a CD of the presentations will be available.

The theme of Substrates is carried further with our editorial this issue called "Are Coreless Substrates Ready to be Mainstreamed?". Written by MEPTEC Advisory Board member Lan Hoang of Xilinx, it explains some different versions of "coreless" substrates and the typical drivers of this particular technology. We'd like to thank Lan for this contribution (see page 34).

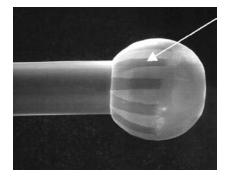

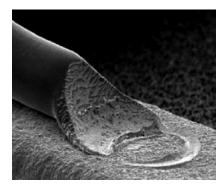

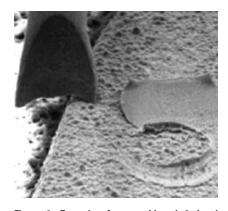

One of our feature articles this issue is from MEPTEC member company **Microbonds, Inc. Robert Lyn** and **Bud Crockett** discuss a new insulated bonding wire technology, which, according to the authors, is "rapidly gaining acceptance as a viable solution for assembling higher pin count, finer pitch, multi-row and multi-stack devices". They cover wire bonding considerations, design rules, cleaning, molding, and reliability testing of insulated wire. The technology was developed by an alliance of many other MEPTEC member

### **Issue Highlights**

| Industry Analysis                           | 6  |

|---------------------------------------------|----|

| University News                             | 8  |

| Industry News                               | 12 |

| Member Company Profile                      | 18 |

| Feature Articles                            |    |

| Automated Double-Sided<br>Overlay Metrology | 20 |

| New Bonding Wire Technology                 | 24 |

| Events Calendar                             | 33 |

| Editorial                                   | 34 |

companies such as **ASM Pacific Technol**ogy, **Small Precision Tools**, **March Plasma Systems** and **Nitto Denko**. Thanks to all contributors for this informative piece (see page 24).

The subject of our other feature article is on patterning technology; specifically automated double-sided overlay metrology. Written by **Keith Cooper** and **Thomas Huelsmann** of **SUSS MicroTec**, this articles explains how with the manufacturing of MEMS devices and other technologies increasingly using this type of patterning, it has led to a growth of MEMS manufacturing processes (see page 20).

Our Member Company Profile this issue is **United Test and Assembly Center, Ltd.** (**UTAC**). UTAC is a leading independent provider of test and assembly services worldwide. Founded in 1997, UTAC is headquartered in Singapore with several manufacturing and sales facilities throughout the world in Asia, Europe and the US. We'd like to thank UTAC for their great continued support – see their story on page 18.

Thanks to all of our contributors for making this a great issue. If you're reading our publication for the first time at one of the many events where we distribute, or if you're a new member, we hope you enjoy it.

Thanks for joining us!

- Free Wireless Internet Access

- 176 Spacious Guest Rooms

- Full Service Restaurant

- In Room Coffee Makers, Refrigerators, Hairdryers, Irons and Ironing Boards, AM/FM Clock Radios and Digital Safes

- On Demand Movies

- Voice Mail

- Heated Outdoor Pool and Jacuzzi

- Banquet/Meeting Space for 250

- Japanese Tatami Rooms

- Minutes from Light Rail, Santa Clara Convention Center and Paramount's Great America

- 24 Hour San Jose Airport Transportation

- Special Group Rates and Packages

# The only full services Ramada in Silicon Valley 408-245-5330

1217 WILDWOOD AVENUE • SUNNYVALE, CA 94089

### A SPECIAL ONE-DAY TECHNICAL SYMPOSIUM & EXHIBITS

## November 8, 2007 • Holiday Inn San Jose • San Jose, California

# Substrates: The Foundation of Semiconductor Packaging

ver the last decade, substrates for semiconductor packages, such as BGA, LGA, CSP, and SiP have evolved to become essential building blocks for silicon integration into electronic systems. In fact, according to TechSearch International, package substrates accounted for approximately \$5 billion in sales during 2006. Today, BGA packages can be found in most electronic systems, from handheld devices like mobile phones and digital cameras, to more expensive systems that move massive amounts of data through the internet, to high-reliability modules for harsh military environments.

The objective of this symposium is to identify technology requirements for the next generation of substrate technology, highlighting required innovations that will further enable IC component integration, and electronic system functionality.

### Sessions will include:

PAC TECH USA

- Substrate Manufacturing and 1st Level Interconnect Technology

- Design and Simulation: Silicon, Substrate, System

- Substrate Manufacturing and 2nd Level Interconnect Technology

- Testing Challenges for Substrate Manufacturing

GOLD SPONSOR

MEDIA SPONSORS

Advanced

Packaging

ChipScale

# MEDIC Industry Analysis

## Semiconductor Packaging and Assembly Equipment Market Faces Shallow Trough in 2007, Modest Growth Expected for 2008

#### Mark Stromberg and Bob Johnson Gartner Dataquest

he lull in demand for semiconductor equipment has arrived. New equipment orders are receding as dynamic RAM (DRAM) capital spending budgets are being exhausted, and other segments are not increasing their budgets to compensate. With annual growth in device sales anticipated at 2.5% (including solar revenue) and soft DRAM pricing, not much upside hope remains for 2007. Still, equipment spending has moved toward the upper end of our forecast scenarios laid out in April, pointing at a slow single-digit market expansion this year. As for 2008, we anticipate that DRAM spending will decline from this year's peak, and equipment market growth will originate from NAND, logic and foundry, which will drive a second year of slow single-digit growth. However, strong forecast DRAM unit demand in 2008 negates concerns of overcapacity and provides upside potential for next year.

Highlights of our forecasts for 2007 are as follows:

• Overall capital spending will rise 0.6% in 2007 and 4.8% in 2008.

• For 2007 and 2008 the wafer fab equipment market will increase about 5% each year.

• Revenue for the packaging and assembly equipment (PAE) segment will decline 5.7% in 2007 but grow 13.1% in 2008.

• Revenue for the semiconductor assembly and test services (SATS) market will increase 9.8% in 2007 and 16.5% in 2008.

#### **Back-End Process Picture**

Capacity utilization increased and was back at about 85% as the second quarter closed. Growth in package unit output continues to be strong, especially in the flash and DRAM memory markets. Packaging technol-

ogy remains in the forefront, as the industry tries to resolve shorter product life cycle and market-timing issues demanded by the consumer. Flip-chip usage has expanded in scope, but substrate costs continue to be the key issue in determining its widespread use across all product lines. Leadless-lead-frame packages - the quad flat no lead (QFN) and dual flat no lead (DFN) — continue to replace the leaded small outline integrated circuit (SOIC) and quad flat package (QFP) devices as cost-saving solutions for product miniaturization. Silicon integration via packaging solutions, such as system-in-package (SiP) and 3-D stacked die and packages, try to keep the industry on the path to continue Moore's Law.

The key, however, is substrate costs, which can be more than 70% of the total cost in some packages. Many of these new packages require improved substrate design and mate-

|                                                | 2005        | 2006        | 2007        | 2008        | 2009        | 2010        | 2011        | CAGR 2005-<br>2011 |

|------------------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|--------------------|

| Real GDP* — Indexed (Billions of 2000 Dollars) |             |             |             |             |             |             |             |                    |

| Worldwide GDP*                                 | 36,452.7    | 37,914.2    | 39,254.4    | 40,660.9    | 42,126.7    | 43,572.1    | 44,996.3    | 3.6%               |

| Growth                                         | 3.5%        | 4.0%        | 3.5%        | 3.6%        | 3.6%        | 3.4%        | 3.3%        | -                  |

| U.S. GDP*                                      | 11,048.7    | 11,415.3    | 11,651.2    | 11,982.1    | 12,366.7    | 12,723.3    | 13,050.2    | 2.8%               |

| Growth                                         | 3.2%        | 3.3%        | 2.1%        | 2.8%        | 3.2%        | 2.9%        | 2.6%        | -                  |

| Electronic Equipment Production (\$M)          | 1,258,170.3 | 1,313,162.6 | 1,377,171.3 | 1,430,999.2 | 1,466,406.7 | 1,522,143.3 | 1,573,907.8 | 3.8%               |

| Growth                                         | 9.0%        | 4.4%        | 4.9%        | 3.9%        | 2.5%        | 3.8%        | NA          | -                  |

| Semiconductor Revenue (incl. Solar) (\$M)      | 238,292.0   | 262,690.4   | 269,218.0   | 292,583.7   | 313,529.8   | 316,406.4   | 337,281.9   | 6.0%               |

| Growth                                         | 7.3%        | 10.2%       | 2.5%        | 8.7%        | 7.2%        | 0.9%        | 6.6%        | -                  |

| Semiconductor Capital Spending (\$M)           | 47,197.1    | 56,298.7    | 56,609.4    | 59,306.9    | 64,753.7    | 57,461.0    | 61,958.0    | 4.6%               |

| Growth                                         | -2.8%       | 19.3%       | 0.6%        | 4.8%        | 9.2%        | -11.3%      | 7.8%        | -                  |

| Capital Equipment (\$M)                        | 34,141.1    | 41,950.2    | 43,103.0    | 45,781.1    | 49,668.4    | 43,688.0    | 48,945.4    | 6.2%               |

| Growth                                         | -10.0%      | 22.9%       | 2.7%        | 6.2%        | 8.5%        | -12.0%      | 12.0%       | -                  |

| Wafer Fab Equipment (\$M)                      | 25,952.3    | 32,610.1    | 34,255.5    | 35,888.2    | 39,600.6    | 34,669.1    | 38,286.2    | 6.7%               |

| Growth                                         | -8.5%       | 25.7%       | 5.0%        | 4.8%        | 10.3%       | -12.5%      | 10.4%       | -                  |

| Packaging and Assembly Equipment (\$M)         | 4,415.9     | 5,217.8     | 4,921.2     | 5,564.7     | 5,642.9     | 4,872.9     | 5,755.3     | 4.5%               |

| Growth                                         | -7.7%       | 18.2%       | -5.7%       | 13.1%       | 1.4%        | -13.6%      | 18.1%       | -                  |

| Automated Test Equipment (\$M)                 | 3,772.9     | 4,122.3     | 3,926.3     | 4,328.2     | 4,424.9     | 4,146.0     | 4,903.9     | 4.5%               |

| Growth                                         | -21.2%      | 9.3%        | -4.8%       | 10.2%       | 2.2%        | -6.3%       | 18.3%       |                    |

| Other Spending (\$M)                           | 13,056.0    | 14,348.4    | 13,506.4    | 13,525.8    | 15,085.4    | 13,773.0    | 13,012.6    | -0.1%              |

| Growth                                         | 23.0%       | 9.9%        | -5.9%       | 0.1%        | 11.5%       | -8.7%       | -5.5%       |                    |

Table 1. The Big Picture: Capital Equipment Spending Forecast, 2005-2011 (Millions of Dollars)

\* All GDP data is from Global Insight.

rials, both plastic and metallic (lead frame). Costs for these packages have increased in parallel with increases in the commodity metal and oil markets. Thus, package prices, costs and margins can all be affected. To what extent they are affected will depend on the fluctuation in the commodity markets. The result has been a cautious capital spending outlook for capacity expansion for 2007 thus far.

#### **SATS Market**

The year-over-year monthly growth rate for the SATS industry began to increase again toward the end of the second quarter after slowing in the first quarter. The second-quarter revenue results for some of the larger SATS companies showed increases in the single- to low-double-digit range compared with the second quarter of 2006. Accordingly, month-to-month growth rates increased in April to May to June, with companies exhibiting increases in the moderate single digits. Monthly sales numbers from March and April indicate that a bottom to the current cycle was reached during this time. Revenue from the top five SATS companies showed positive gains for May and June, with increases above that of March. All these factors contribute to our forecast of 8.4% growth for the second quarter.

Utilization rates appeared to be at sustainable levels, at about 85%, as the second quarter ended. Pricing continues to be relatively stable for most packages. However, memory packages and test are becoming squeezed as the competition and ASP erosion in the final device market puts pressure on the packaging companies to lower their prices.

For the third quarter, the SATS market will show a moderate increase in July, followed by a rise in August and September. This will result in a growth rate of 9.8% for the quarter. For the fourth quarter, a moderated growth pattern will occur as the holiday buying season in some regions winds down, resulting in growth of 2.9% for the fourth quarter. For the entire year, the industry momentum

in the second half will result in SATS market growth of 9.8% for 2007.

#### PAE Market

After growing slightly more than 18% in 2006, PAE market revenue will decline about 6% in 2007. The market picture for PAE has improved from our previous forecast revision, when we expected a 12% decline. This was due to modest improvements in the spending picture for SATS players. After this expected decline in 2007, we project a slightly moderated PAE growth rate of 13% in 2008.

On a regional basis, Asia/Pacific will continue to increase its share of PAE consumption. From about 66% of PAE shipments in 2006, Asia/Pacific will account for more than threequarters of all PAE sales early in the next decade. China will be the largest individual consumer of PAE by 2011, accounting for about 24% of the total market and surpassing Taiwan in that year. ◆

# **MEPTEC** University News

# Materials Science and Advanced Packaging at Boise State University

Amy J. Moll, Ph.D. Chair and Associate Professor Materials Science and Engineering

Patricia Pyke Director of Education Research College of Engineering

student loads a silicon wafer into the reactive ion etcher to create a series of through wafer vias. Following etching the wafer, through several more process steps including diffusion and metallization with the goal of creating a solar cell with all metallization on the back side of the wafer, increases its efficiency. This application is one of the projects that takes advantage of the through wafer interconnect processes developed by Boise State University for 3-D packaging.

In a nearby lab, another undergraduate laminates together 300 layers of a flexible ceramic tape on which electronic components are printed, in order to create an integrated drift tube for an ion mobility spectrometer which will be deployed to measure contaminants in ground water in the subsurface. At Boise State, these students are learning firsthand what they can do with a degree in materials science and engineering, while also contributing significantly to the university's research mission.

Boise State University's Micron Engineering Center.

t Boise State University, microelectronic packaging is a centerpiece of research and of undergraduate and graduate education. Four years ago Boise State University was given a generous donation from the Micron Technology Foundation and a once-in-a-lifetime opportunity to build a materials science and engineering (MSE) B.S. program from scratch. Integrating teaching and research was a philosophy shared by the department's founding faculty. As the College of Engineering at Boise State was only six years old at the time, the faculty was unencumbered by "we've always done it this way" mandates. Only two years prior, an interdisciplinary program at the M.S. level in Materials had been created in conjunction with physics and chemistry departments. This interdisciplinary approach recognizes that the most promising technological solutions to global problems affecting health, energy and the environment now occur at the boundaries between fields - biology and materials, electrical engineering and materials, etc.

From the outset, the new MSE department was imbued with an entrepreneurial spirit and interdisciplinary focus. Additionally, the department's creation was guided by strong ties with the local electronics industry, ABET accreditation requirements, and the desire to build a topnotch program. The young MSE program now has eight well credentialed faculty with more than \$5 million in currently active sponsored research.

Unlike most engineering colleges where enrollment is declining, enrollment at Boise State is rapidly increasing, propelled partially by the university's location in one of the nation's fastest growing technology centers and metropolitan areas. Indeed, the Boise Metropolitan Area is listed frequently on Top Ten lists for business, careers, patents, manufacturing, and entrepreneurial energy, published by Forbes, the Wall Street Journal, Money magazine, the Milken Institute, and others. As a metropolitan institution, Boise State serves a diverse student population, including many non traditional students starting second careers. The average age for engineering undergraduates is 25, and 35% are 26 or older. These non-traditional students bring a wealth of experience that enables them to make contributions in the research lab much earlier in their academic careers than most students. In turn, the students gain hands-on knowledge that not only helps them in their academic studies but guides their career directions, with microelectronics a choice for many.

#### Through Wafer Interconnects (TWIs)

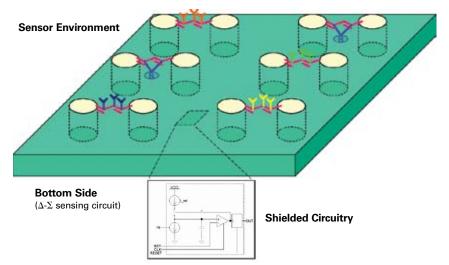

One area of focus or expertise at Boise State is the fabrication and use of through wafer interconnects for stacking silicon based devices. Research performed over the last six years in collaboration with RTI in North Carolina has resulted in an integrated process for the fabrication of 3-D integrated circuit (IC) devices and microsystems. Through wafer interconnects (TWIs) have distinct advantages to other advanced 3-D packaging schemes. Additional miniaturization, increased interconnection density, and higher performance is possible by stacking die with through wafer interconnects. Power consumption can be reduced by shortening the overall wire lengths, while also providing thermal vias for heat removal. Through wafer interconnects are of particular interest in (micro-electromechanical) MEMS and sensor packaging. (see Figure 1) TWIs address two challenges in MEMS packaging - cost and size. In MEMS, the package is often 75 to 95% of the cost. The package

size may also be significantly larger that the actual die. These 3-D integration processes, some of which are wafer-scale and some die-scale, enable a technology platform with a highly integrated electronic system containing multiple subsystems on a common "silicon circuit board". The use of the z-dimension in the integration enables a dramatic reduction in the area occupied by the circuitry, and massively parallel signal processing in pixilated device architectures. This advanced system integration concept has the potential to enable multifunctional electronic systems with dramatically reduced size, weight and power, as well as dramatically enhanced performance. (see Figure 1)

The capabilities of 3-D technology are being applied to several emerging areas, namely sensors and microactuators. Through wafer interconnect technology allows new devices to be fabricated that could not be built in any other way. In addition TWIs allow for significant improvement in passive devices such as

Figure 1. Technology platform that incorporates a sensor on the top side of the wafer and circuitry on the backside of the wafer connected with through wafer interconnects.

# MEDIC University News

3-D inductors that not only have better performance but also take up significantly less real estate on the wafer.

In addition to exploring new devices enabled by TWIs, Boise State faculty and student researchers are developing a fundamental understanding of materials processing required for fabrication. The relationship between microstructure and processing parameters for processes such as electrodeposition of copper and chemical mechanical planarization of copper are not fully understood. This understanding is important not only for optimization of TWI processing but also for standard IC processing.

#### **Ceramic MEMS**

Another research area at Boise State is the development of micro-electromechanical (MEMS) devices, micro-analytical systems and microfluidic packaging (see Figure 2) in ceramic tape technology. This materials system was developed for efficiently manufacturing interconnects and hybrid microelectronics circuitry through sequential printing and firing of conductor, resistor and/or dielectric paste formulations onto a substrate. The materials system is commonly used for the packaging of microelectronics particularly in the communications industry. Ceramic tapes can also be used as an efficient and convenient medium for the manufacturing of miniature analytical systems and MEMs devices because of their many advantages including:

- Ease of 3-D multi-layering.

- Integration of a wide variety of organic and inorganic materials results in the ability to incorporate many different properties and functions into individual layers which are then fired into a single substrate.

- Ability to achieve dielectric, capacitor, resistor, conductor, magnetic, piezoelectric, heater, thermal pipes and temperature sensor related functions within the material.

- In the green (unfired) state, tapes are soft, pliable and easily machinable.

Size features from 10 microns to 10 mm can easily be created by mechanical, thermal or chemical means.

- Straight forward integration of other devices including integrated circuits and micro electro mechanical (MEMS) devices out of Si.

- Adaptability to embedded fluidic structures.

- Elevated temperature fabrication allows for use of the devices in harsh environments both chemically aggressive as well as extreme temperatures.

- Robust thermal budget for joining technologies.

- Ability to quickly be scaled up to mass production.

- Communication between layers by vias (both fluidic and electronic).

- Rapid prototyping and batch processing for mass production readily available.

- Electronic circuits can be printed on and flow components can be machined in individual layers.

- Large number of layers can be laminated together (up to 100).

- Fabrication techniques are relatively simple and inexpensive.

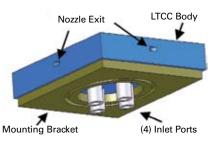

Boise State University has created a Ceramic MEMS lab with a principal focus on fabrication with low temperature cofired ceramic (LTCC) materials. The laboratory is exploring numerous devices and has had funded projects in a wide variety of areas, including the fabrication of a miniature Ion Mobility spectrometer for use in monitoring groundwater contamination, a small electrochemical cell in LTCC (see Figure 3) with multiple electrodes that could be functionalized to detect numerous substances, and energy scavenging devices. A three-year grant from the Air Force Office of Scientific Research has resulted in the design, fabrication and testing of a micropropulsion device in LTCC. (Figure 4) The device includes a catalytic chamber to decompose high purity hydrogen peroxide and a converging diverging nozzle. The device is targeted for station keeping operations for micro satellites (less than 20 kg).

As the potential application of through wafer interconnects and ceramic MEMS are both diverse and plentiful, the department welcomes additional collaboration

Figure 2. Microfluidic device in low temperature co-fired ceramics incorporating fluidic ports and an optical window made of sapphire.

Figure 3. Miniature electrochemical cell fabricated in low temperature co-fired ceramics.

Figure 4. Fully integrated micropropulsion device fabricated in LTCC.

with industrial and government partners. 3-D packaging schemes and ceramic MEMs devices are just two areas of research at Boise State. The broad range of research activities, the interdisciplinary nature of both research and coursework, and the involvement of both undergraduate and graduate students in research have resulted in a thriving and collaborative Materials Science and Engineering department. The culture of innovation fostered by this new department is advancing the state of knowledge in microelectronics packaging, and also equipping B.S. graduates to enter industry with meaningful experience in research procedures and materials processes.

# Complete Wafer Bump Services in the U.S. and CHINA – FROM ICI/JCAP INTERNATIONAL

ICI/jcap International is the shortest distance between two points for clients like you who need complete wafer bump services. With facilities in both Colorado Springs, Colorado and Jiangyin, China, ICI/jcap is the company to call. Our business model is built upon best pricing, all bumping technologies, superior technical support, and worldclass quality systems.

Contact either of our U.S. offices to find out how ICI/jcap International can be your bump solutions partner.

#### **Contact IC Interconnect at**

- p/ 719.533.1030 Colorado Headquarters

- p/ 408.532.0122 Silicon Valley Customer Support

- e/ ici@icinterconnect.com

- www.icinterconnect.com

# Made Industry News

## Dr. Ken Gileo and Joe Fjelstad Join Mirror Semi's Technical Advisory Board

Dr. Ken Gileo

#### Joe Fjelstad

IRVINE, CA – Dr. Ken Gilleo, widely known for his authorship of seven technical books, numerous semiconductor packaging patents, and frequent speaking appearances at professional conferences, and Joseph C. Fjelstad, author, inventor and integrated circuit packaging expert, have joined the Technical Advisory Board of Mirror Semiconductor Inc.

Dr. Gilleo, who earned his doctorate in chemistry from the University of Connecticut, brings nearly four decades of experience in electronics and electronics packaging to the Mirror Board.

Currently owner of ET-Trends LLC, Warwick, R.I., a consultancy focused on emerging technologies, Dr. Gilleo's most recent book is MEMS/ MOEMS Packaging, published by McGraw-Hill, New York.

Dr. Gilleo is also vice president for technical programs at the SMTA, the nation's leading trade organization for professionals in electronics assembly technology in Edina, Minn.

Fjelstad, who is internationally known as a popular speaker on topics related to integrated circuit packaging and interconnection, is the co-founder of SiliconPipe Inc., San Jose.

Prior to founding Silicon-Pipe in 2002, Fjelstad was an early stage development engineer at Tessera Technologies, San Jose, where he was named the company's first "Fellow" for developing several patents that greatly advanced the stateof-the-art in packaging, as well as for promoting the company's now widely accepted interconnection technology.

Joe is a columnist for several industry publications, and the author or co-author of several books, including Flexible Circuit Technology, 3d Edition and Chip-Scale Packaging for Modern Electronics. He is responsible for the development or co-development of nearly 100 patents over his 35 years in the semiconductor industry.

For more information about Mirror Semiconductor go to www.mirrorsemi.com.

### Air Liquide Names David LeBlanc President of U.S. Electronics Business

Dave LeBlanc has been appointed president of Air Liquide Electronics U.S. LP (ALEUS). LeBlanc will be based at Air Liquide's U.S. electronics business headquarters in Dallas, Texas.

LeBlanc will lead the company's businesses related to the supply of electronic gases, chemicals and services to the U.S. semiconductor industry, including sales and marketing, production, distribution, R&D, Total Gas & Chemical Management services and analytical laboratory services (Balazs Analytical Services Division). ALEUS has more than 600 employees across the country, concentrated in the western U.S., Texas and northeastern U.S.

A 24 year veteran of Air Liquide, LeBlanc was most recently vice president of process industries for Air Liquide Canada, where he was responsible for the company's bulk gases, Floxal and onsite businesses. He has held numerous other roles in the company, leading activities in marketing and distribution, human resources, and customer service.

With nearly 37,000 employees in 72 countries, Air Liquide is a world leader in industrial and medical gases and related services. The Group offers innovative solutions based on constantly enhanced technologies, contributing the manufacturing of many everyday products.

For more information visit the Air Liquide Group web site at www.airliquide.com.

## CMC Promotes Erich Rubel to Principal Lab Analyst

TEMPE, AZ – CMC Interconnect Technologies, a global resource for technical consulting and analytical services to the electronics industry, promoted Erich Rubel to Principal Analyst. Erich has extensive industry experience in failure analysis focused on advanced materials and electronic interconnect technologies, across the range of device, package, and board levels found in state-ofthe-art products.

"The success of CMC's Business Model continues to be centered around analytical and consulting services in root-cause determination and the resolution of critical client issues," stated Dr. Jonathan Harris, President of CMC, "with Erich having a significant senior role in the analytical group, which is staffed by engineers and scientists with broad industrial experience in many key market segments".

Focused on advanced mate-

rials and the processing technologies for electronic interconnect, CMC provides solutions to the industry segments including: Semiconductor, Medical, RF and Telecom, Mil/Aerospace, Photovoltaic/Opto, HBLED and MEMS/Sensor.

This global client base from Start-ups to the Fortune 100s, includes Semiconductor Device Manufacturers, Advanced Material Suppliers, Subcontractors, Passive Component Fabricators and Investor Groups.

CMC can be reached at info@cmcinterconnect.com or 480-496-5000. Please visit www.cmcinterconnect.com for additional information.

## Jerry Coder Named Chairman of SEMI

SAN FRANCISCO, CA-SEMI has announced the appointment of Jerry Coder, president emeritus of the Semiconductor Materials Business unit of Dupont Electronic Technologies, as chairman of the industry association's International Board of Directors. Coder succeeds Archie Hwang, chairman and CEO of Hermes-Epitek, who served as chairman for the past year. The results of the association's annual elections were announced at the annual SEMI membership meeting, which was held during the SEMICON West 2007 exposition in San Francisco.

In addition to the chairman, the association's membership elected Dr. Susumu Kohyama, president and CEO, Covalent Materials Corporation; Kiyoshi Togawa, senior vice president and executive officer, Hitachi Chemical Co. Ltd.; Way Tu, CEO and president of Allegro Manufacturing, Pte. Ltd.; and Kazuo Ushida, director, member of the board and senior executive officer of Nikon Corporation and president of Nikon's Precision Equipment Company.

Coder has over 40 years of semiconductor industry experience, and has been a staunch supporter of SEMI, serving in numerous leadership roles including chairman of the SEMI Finance Committee, member of the Board's Executive Committee, member of the Environmental Health and Safety (EHS) Executive Committee, and Emerging Technologies Committee.

For more information, visit www.semi.org.

## ASAT Appoints Peter Tin Senior VP of Quality and Reliability Assurance

HONG KONG and MILPITAS, CA – ASAT Holdings Limited has announced the appointment of Peter Tin as senior vice president of quality and reliability assurance, replacing Ed Bedell who resigned to pursue other opportunities.

Mr. Tin previously served as ASAT's vice president of quality from 2004 to 2005 prior to ASAT moving its manufacturing to China. During this time he was responsible for setting up the quality systems at ASAT China and instrumental in maintaining quality systems control during the transition.

Over the span of his more than 20 year career, Mr. Tin has held engineering, supplier management, reliability and quality positions in semiconductor, consumer electronics and transportation industries in the United States and Greater China.

For more information, visit www.asat.com.

## ASAT Appoints Kei Hong Chua CFO

HONG KONG and MILPITAS, CA – ASAT Holdings Limited has announced the appointment of Kei Hong Chua, 36, as executive vice president and chief financial officer effective immediately. Kei Hong succeeds acting CFO Kei Wah Chua, his brother, who will continue serving as a member of the Company's board of directors.

Kei Hong brings nearly 15 years of banking, finance and accounting experience to ASAT Holdings. Prior to joining ASAT, Kei Hong was head of Standard Chartered Bank's Alternate Investment Group in China, where he was responsible for proprietary investments in special situations across Asia. Previously, Kei Hong served as a senior manager in Corporate Finance and Business Recovery Services at PricewaterhouseCoopers in Hong Kong and as a senior manager in Arthur Andersen's Global Corporate Finance - Corporate Restructuring Services in New York. In addition, he served as a founding partner and CFO of Vertical Think, Inc., a management and consulting firm for companies engaged in eBusiness.

For more information, visit www.asat.com.

### Precision Process Establishes Tech Center in Boise Idaho

BOISE, ID – Precision Process Equipment, a designer and manufacturer of custom plating and wet processing equipment, has opened a technical center in Boise Idaho.

"Opening this office in Boise will allow us to broaden our reach to the West and the Far East" says Doug Stewart, Vice President of Sales and Marketing, adding that "operations in Boise will focus on the marketing needs of Precision Process as well as function as the focal point of the strategic partnership, Process Partners International, formed with China based manufacturer PAT."

Precision Process Equipment, headquartered in Niagara Falls NY, provides custom equipment solutions for many technologies including; Semiconductor, Solar Power, RFID, MEMS, Flexible Displays, Medical Devices, Automotive and Aero Space.

For more information visit

Looking for the best insurance against flip chip defects?

An example of an actual Sonoscan C-SAM® acoustic scan showing a flip chip with die cracks and delamination defects.

# Demand Sonoscan

Cracks, voids and delaminations can elude electrical tests. And if left undiscovered, they may result in costly production shutdowns, quarantined products and very disappointed customers.

Sonoscan systems are widely relied upon for nondestructive inspection. Using the most advanced acoustic technology available, Sonoscan accurately locates and analyzes these hidden defects—*before* they lead to failures.

#### **Packaging Applications**

- Plastic Encapsulated IC

- Die Attach

- Flip Chip

- Stacked Die

- Smart Card

- Chip Scale Package

- and many others

To learn more about Sonoscan systems and AMI technology, visit www.sonoscan.com

Sonoscan—trusted for over 30 years

800-950-2638 • 847-437-6400 • www.sonoscan.com Santa Clara, CA • Scottsdale, AZ • Elk Grove Village, IL • Burlington, MA England • Philippines • Hong Kong • Taiwan • Singapore • Shanghai

# MEDIC Industry News

www.precisionprocess.com and www.processpartnersinternational.com. Contact Precision Process at 1.800.707.3433 or 208.343.4020

## Major Packaging Technology Alliance Announced by Microbonds Inc., Mirror Semi and PROMEX

Microbonds Inc., Ontario, Canada; Mirror Semiconductor Inc., Irvine, California; and PROMEX Industries Inc., Santa Clara, California, will blend their existing processes, products and expertise to develop advanced integrated circuit (IC) packaging.

This collaborative engineering effort will enable Promex, a leader in preparing new technologies for transfer to highvolume environments, to use Microbond's "X-Wire" technology and to co-develop IC package types which use Mirror Semiconductor's novel Mirrored Pinout <sup>TM</sup> designs.

X-Wire Technology allows interconnect bonding wires to

touch and cross without electrical shorting, permitting fuller utilization of the x,y and z dimensions in electronics design and packaging.

Both Mirror Semiconductor and Microbonds provide new packaging technologies

Martin Hart, president of Mirror Semiconductor, displays a Mirror Semiconductor QFN package prototype that features Microbonds' X-Wire technology, while John Scott, Microbonds' president and CEO, looks on. At left is Richard Otte, president and CEO of PROMEX Industries, which produced the prototype.

designed to extend the life cycle and technical capabilities of today's packaging infrastructures with the lowest cost solution.

Richard Otte, CEO of Promex, said, "We are delighted to work with Microbonds and Mirror Semiconductor on this initiative. Our experience has taught us that the introduction of new materials and processes is much easier and faster when the parties can work openly together to achieve the goals of end customers."

For more information, contact Martin Hart, President, Mirror Semiconductor at info@mirrorsemi.com, phone 949-250-4001 or visit www.mirrorsemi. com.; John Scott, CEO, Microbonds, at jscott@microbonds. com, phone 905-305-0980 x222 or visit www.microbonds.com; Richard Otte, CEO, Promex, at otte@promex-ind.com, phone 408/496-0222, or visit www. promex-ind.com.

#### SILICON MICROPHONE

#### DESCRIPTION

The silicon based MSM series microphones are integrated with specialized pre-amplification ASIC to provide high sensitivity, high signal to noise ratio output from a capacitive audio sensor. Packaged for surface mounting and high temperature re-flow assembly, it routinely operates in adverse conditions that would permanently damage conventional microphones

#### FEATURES

- Available in Top Mount, Reverse Mount, Differential

- Sensitivity Ranges, -20dB to -45dB

- Low Profile, 1.25mm

- Operating Voltage, 1.5 ~ 3.6V

- Current Consumption, 150µA Typical

- S/N Ratio, 58dB Typical

- THD less than 1% @ 110dB SPL

- Sensitivity Variation, ≤1.5dB

- Ultrasonic Range, 20KHz ~ 80KHz

- Operating Temperature -40°C to 100°C

- Reflow Temperature, 260°C

- RoHS Compliant

#### **Top Mount**

APPLICATIONS

- Mobile Phones

- Laptops Computers

- PDA

- Portable Media Player

- MP3 Player

- Digital Ćamera

- Video Camera

- Voice Conferencing System

- Hands Free Car Kit

- Ultrasonic Applications

- Microphone Arrays

**Reverse Mount**

- Security System

- Industrial Applications Noise Monitoring, Safety, Flow Monitor

# Differential

MSM2DP / 2PP

For more information visit www.memstech.com

MSM2RM

## Enabling Solutions Names Pacific Gate Technologies Technical Sales Rep

SAN JOSE, CA – Enabling Solutions Inc. a leading provider of System-in-Package design and prototype services, signal integrity analysis, and power integrity solutions has appointed Pacific Gate Technologies (PGT), San Jose, as its first technical sales representative.

Manoj Nachnani, ESI president, said continued demand for the company's services created the need to add a representative to his company's direct sales efforts.

ESI specializes in designing, developing and prototyping System-in-Package devices (SiPs). Once the prototype has successfully passed through its co-design and electrical characterization, ESI and PGT will follow the SiP through highvolume manufacturing and test.

The 11-year-old ESI complements Pacific Gate's other clients, which include the Malaysian-based Polar Twin Advance IC packaging foundry, and Minami, a Japaneseheadquartered equipment manufacturer for WLCSP screen printing systems.

For more about Pacific Gate Technologies visit their website at www.pacificgate-us.com.

Visit www.en-solutions.com for more information about Enabling Solutions.

## STATS ChipPAC Acquires LSI's Assembly and Test Operation in Thailand

UNITED STATES and SING-APORE – STATS ChipPAC Ltd. and LSI Corporation have announced a definitive agreement for STATS ChipPAC to acquire LSI's assembly and test operation in Pathumthani,

Danny Fields (left) of Pacific Gate Technologies and Manoj Nachnani of Enabling Solutions, celebrate their new affiliation.

Thailand for an aggregate purchase price of approximately \$100 million.

Under the terms of the agreement, STATS ChipPAC will acquire LSI's assembly and test operation in Thailand which consists of a facility with approximately 440,000 square feet of floor space, manufacturing equipment and certain other assets. STATS ChipPAC will offer employment contracts to LSI employees in the Thailand facility. LSI will further enter into a long-term supply agreement with STATS ChipPAC for their assembly and test services needs.

More information about LSI is available at www.lsi.com.

Further information about STATS ChipPAC is available at www.statschippac.com.

### Investors Back Vietnam Packaging Plant

PALO ALTO, CA — Several Silicon Valley companies invested as much as \$200 million to launch a packaging plant in Hanoi, Vietnam. The company, Vietnam-Chipscale Advanced Packaging Services (V-Caps) will involve executives from the Silicon Valley region and the local industry in Vietnam, and could employ up to 1,500 workers initially.

V-Caps will assemble and test packages for semiconductor manufacturers across industry segments, including cellular, computing, and other areas. Operations are planned in a 300,000-sq.ft. factory in the Hoa Lac High Tech Park, according to San Jose Mercury News. Two similar buildings may be constructed for increased operations.

Founder Harry Rozakis expects local contribution, a knowledge base in the country, and low-cost business incentives to drive Vietnamese electronics manufacturing development, higher-end production services, and broad outsourcing. Vietnam operations cost significantly less than China facilities, said Sanford Garrett, seed investor in V-Caps from the Garrett Group Technology (San Francisco) financial consulting firm.

The investment round was discussed at the Vietnamese Strategic Ventures Network conference in Palo Alto. Intel invested in a Vietnam assembly and test facility at the end of 2006, and Gartner analyst firm reports that, in 2007, new Asia facilities are distributed, with China hosting about half, across Asia states such as Vietnam, Thailand, and other developing countries.

## Asymtek Wins Awards for Excellence at SEMICON West

CARLSBAD, CA – Asymtek, a Nordson Company and leader

in dispensing technology and pioneer in jetting technology, received two prestigious industry awards for its technology and service SEMICON West: Advanced Packaging magazine honored Asymtek's SC-400 PreciseCoat<sup>™</sup> Jet for its technical innovation, and Semiconductor International magazine selected Asymtek's Dispense-Jet® DJ-9000 Series as a winner of their Editors' Choice Award for the Jet's commercially proven excellence in semiconductor manufacturing.

Besides the two awards presented at SEMICON West, a leading research and analysis firm in the chip making industry acknowledged Asymtek as one of the Ten Best Suppliers of Assembly & Test Equipment in the semiconductor industry.

For more information, visit www.asymtek.com.

## Multiprobe Inc. Named One of Fastest Growing Companies in America

SANTA BARBARA, CA – Multiprobe Inc. is pleased to announce it was ranked #68 in Entrepreneur magazine's Hot 500 for 2007. Multiprobe is the leading manufacturer of high tech instrumentation for nanoprobing semiconductor devices.

The company started in the garage of founder Andy Erickson in 2001. He was soon joined by former friends, Casey Hare and John Coates, who helped to bring the cutting edge atomic force prober to market. Today the company employs more than 30 people and is the preferred choice of the world's leading semiconductor manufacturers.

Director of Worldwide Sales, Patrick Harrington, sees firsthand, the result of Multiprobe's customer oriented philosophy. "The feedback from customers is overwhelmingly positive. Satisfied customers throughout the industry are sharing their experiences with

# MELLE Industry News

their colleagues and generating a great deal of new business for us. It is an exciting time for Multiprobe."

In its annual ranking of America's fastest growing businesses, Entrepreneur magazine evaluated more than 95,000 companies and used strict criteria, including sales volume, sales growth, and positive job growth. For details and other companies in the HOT 500 visit www.entrepreneur.com/ HOT500 or see the August 2007 edition.

For more information, contact Emily Ziliotto, Multiprobe, (805)560-0404, Emily@multiprobe.com.

## **Sonoscan Updates** Its "Gold Standard" **C-SAM System**

ELK GROVE VILLAGE, IL -Sonoscan has unveiled the new D-9500<sup>™</sup> update of its popular C-SAM<sup>®</sup> acoustic microscope system. The contemporary D-9500 replaces the widely used "gold standard" D-9000 system in Sonoscan's line-up, and like the D-9000 excels in failure analysis, product development, material characterization and low-volume production.

The maximum scan area has been increased to allow the user to image a great number of

parts at once - two JEDEC-size trays of parts, for example, or a 300mm wafer. In addition, the loading and handling of samples has become much more user friendly with improved lighting and enhanced access to the scan area.

Like the D-9000, the D-9500 takes advantage of Sonoscan's

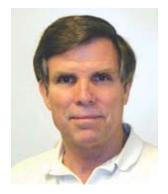

# North American Semiconductor Equipment Industry Posts July 2007 Book-To-Bill Ratio of .84

SAN JOSE, CA - North American-based manufacturers of semiconductor equipment posted \$1.44 billion in orders in July 2007 (three-month average basis) and a book-to-bill ratio of 0.84 according to the July 2007 Book-to-Bill Report published today by SEMI. A book-to-bill of 0.84 means that \$84 worth of orders were received for every \$100 of product billed for the month.

The three-month average of worldwide bookings in July 2007 was \$1.44 billion. The bookings figure is down 10 percent from the final June 2007 level of \$1.61 billion and 17 percent less than the \$1.73 billion in orders posted in July 2006.

The three-month average of worldwide billings in July 2007 was \$1.71 billion. The billings figure down three percent from the final June 2007 level of \$1.77 billion and four percent higher than the July 2006 billings level of \$1.64 billion.

"The declining book-to-bill ratio is based on lower order levels for new semiconductor manufacturing equipment," said Stanley T. Myers, president and CEO of SEMI. "Orders have slowed from the strong levels observed in the first part of this year and are at levels last seen in November of 2006."

three-month moving average bookings to three-month moving average shipments.

The SEMI book-to-bill is a ratio of Shipments and bookings figures are in millions of U.S. dollars.

proprietary processing algorithms and acoustic transducers to provide the highest levels of accuracy and sensitivity available, along with the highest throughput. Proprietary software tools maintain the accuracy of echo polarity and depth data, a feat of precision that competing systems cannot achieve.

Sonoscan quality is also evident in the D-9500's Q-BAM<sup>™</sup> mode, used to make acoustic cross sections that are nondestructive but that are as informative as destructive cross sections. Users have also discovered that a Q-BAM image is the critical first step in performing Acoustically Guided Destructive Physical Analysis<sup>™</sup>.

For more information visit www.sonoscan.com, call 847-437-6400, or email Sonoscan at info@sonoscan.com.

## New STC Initiative Addresses Rising Cost and Efficiency Challanges

NIWOT.CO-The Semiconductor Test Consortium, Inc. (STC) has announced that major progress has been made with a new initiative to enable the development of automatic test equipment (ATE) peripheral interface standards. Designed to foster pre-competitive collaboration among the entire global semiconductor test supply chain, the Semiconductor Test Interface eXtensions (STIX<sup>™</sup>) initiative addresses rising cost and efficiency challenges that impact areas around the ATE, such as enabling greater portability of test collateral through higher level abstraction of user programming, equipment integration and device interconnect.

Over the past 12 months, 11 new corporate members, six new individual members and 15 new university members joined the STC in support of the consortium's expanded scope to encompass the entire test process through the STIX initiative. The roster of new members include corporate and individual members from companies such as FormFactor, Wright Williams & Kelly, and Infineon.

The STIX initiative encompasses both open hardware and software specifications for all peripheral areas around the ATE, regardless of tester architecture or vendor. By standardizing these interfaces, integrated device manufacturers (IDMs) and outsourced semiconductor assembly and test (OSAT) service providers can benefit by gaining higher equipment utilization and easier line balancing. In addition, equipment suppliers can benefit by reducing the need for redundant research and development (R&D) efforts in non-differentiating product areas. More information can be found at www.semitest.org. ◆

- Quick-turn and mass-production

- Highly competitive, low-cost bumping technology

- Exceptional quality through high-level expertise

### PAC TECH

Pac Tech GmbH Tel: +49 (0)3321/4495-100 sales@pactech.de www.pactech.de

#### Pac Tech USA Tel: 408-588-1925, ext. 202

sales@pactech-usa.com www.pactech-usa.com

Pac Tech Asia Sdn. Bhd. Tel: +60 (4) 6430 628 sales@pactech-asia.com www.pactech-asia.com

#### THE WORLD OF NAGASE

Tel: +81-3-5640-2282

takahiro.okumura@nagase.co.jp www.nagase.co.jp

#### **Available Processes**

- Electroless Ni/Au under-bump metallization

- Ni/Au bump for ACF or NCP assembly

- Solder paste stencil printing

- Solder ball drop for wafer-level CSP

- Solder jet for micro-ball placement

- BGA and CSP reballing

- Wafer backside thinning and wafer dicing

#### **Special Features/Technologies**

- Over 10 years experience

- U.S. Government Certified

- 4- to 12-inch wafer capability

- Wafer pad metallization: Al and Cu

- Solder alloys: eutectic SnPb37, lead-free, low-alpha, and AuSn

- Fluxless and contactless bumping for MEMS and optoelectronics

- Ni/Au interface for wire-bond applications

The leader in low-cost electroless wafer bumping.

# Maine Member Company Profile

UTAC

## United Test and Assembly Center Ltd.

Offering full turn-key services to the semiconductor industry

United Test and Assembly Center Ltd. (UTAC) is a leading independent provider of test and assembly services for a wide range of semiconductor devices that include memory, mixedsignal/RF, analog and logic integrated circuits. UTAC offers full turnkey services that include wafer sort/laser repair, assembly, test, burnin, mark-scan-pack and drop shipment, as well as value added services such as package design and simulation, test solutions development and device characterization, failure analysis, and full reliability test.

**TAC's** customers comprise leading worldwide blue-chip semiconductor companies, integrated device manufacturers, fabless companies and wafer foundries that engage in the design and manufacture of semiconductors devices and powering electronic appliances.

The company's strategy is to attain a leading manufacturing role in the support of high growth applications of the Memory (DDR II/III and Flash), Mixed-Signal (3G communications, Digital Consumer), and Analog business segments. Founded in November 1997, UTAC began full operations in January 1999. The Group is headquartered in Singapore, with seven manufacturing facilities in Singapore, Taiwan, China, and Thailand and sales operations in the US, Europe, and Asia. As of December 2006, UTAC employs about 8,500 people.

UTAC's manufacturing locations are strategic in aligning with customer support and consumer demand, regional growth, cost efficiency, and risk management. The Group's manufacturing facilities in Singapore, Taiwan, China, and Thailand are supported by a global sales network in the US, Europe, and Asia. UTAC's worldwide sales offices are located in Fremont and Irvine, CA; Dallas and Austin, TX (USA); UK and Italy (Europe); and Japan, Korea, China, Taiwan, Thailand, and Singapore (Asia).

UTAC's expertise in both memory and non-memory (mixed-signal/RF and logic) semiconductor devices is a key enabler for providing wide-ranging packaging and test solutions such as multi-chip packages that integrate memory and non-memory dies. They offer full turn-key solutions starting from wafer sort to drop shipment services, direct from their facility to minimize your freight cost and delivery times. Their core services are supported by value-added services that include reliability lab, failure analysis, package design and test engineering services. They are also able to offer advanced solutions for several key end-application markets.

As a global top-ten test services company, UTAC is committed to providing the very best test capabilities and the most appropriate test solutions to fit their customers' needs. They are equipped with state-of-the-art test platforms that cater to the industry's wide range of products, including memory, mixed signal/RF & logic, and hybrid memory/mixed signal multi-chip packages. Their experienced and dedicated test development & engineering team help their customers meet specific test technology and production needs, from the IC design concept stage to the mass manufacturing stage in a fast

## UTAC's Manufacturing Facilities include:

1190 Wire-bonders 480 Memory Testers 356 Analog/MS Testers 1891 Ksqft Manufacturing Space 8500 Employees

time to market and cost-effective production cycle.

UTAC offers a broad array of JEDECcompliant leadframe, laminate-based IC packages, and application-specific packaging solutions to meet their customers' needs. Standard leadframe packages include TSOPs, QFPs, and VQFNs with pin counts ranging from 16 to 208. Laminate-based packages include FBGAs, stacked die MCPs, wCSPs, PBGAs, and flip chip BGAs that can be designed to meet specific customer's device-performance and form-factor requirements.

To meet the increasing demand for higher degree of functional integration and smaller form-factor for semiconductor IC products, UTAC has developed a range of application specific and System-inpackage (SiP) solutions. These solutions leverage UTAC's design and process competence that integrates the latest packaging technology in substrate and packaging materials, thin wafer back-grind processing, die stacking, and advanced wire bonding.

Further information about UTAC can be obtained by visiting the company's website at www.utacgroup.com.

## UTAC's Turn-key Assembly & Test Services

#### Wafer Services

- 200mm & 300mm process capability

- Wafer Probing, including bumped wafers

- Laser Repair

- Wafer Bumping/RDL (NEPES – JV)

- High-capacity on broadline portfolio of JEDEC packages:

- Leaded

Leadless

- Substrate

- Specific packaging and module solutions: wCSPs/ Flip Chip /Stack Die/UTOP, SiP, SD/MMC Cards and DIMMs

Package/Module R&D

- DDR2, DDR, SDR Mobile DRAM

- NAND, NOR Flash, SRAM, Combo Memory devices

- ATE test for Mixed Signal, Analog, Logic, RF ICs

- Test-During-Burn-In

- Test Development and

Engineering

Mark/Scan

- 3D Laser Scan

- Laser mark, Ink Mark

- Waffle Pack, Tray, T&R packing

Drop Shipment

UTAC (Shanghai) Co. Ltd. -1 factory Wai Gao Qiao FTZ, Shanghai WS and FinalTest Facility, Mixed-Signal I/C wCSP/BGA Assembly Operations started in September 2003

UTAC (Thailand) Ltd., Bangkok – 3 factories WS, Assembly and Final Test Facility, Memory, Logic, Analog I/C Package R&D and Design, Test Development SATS operations established 1993

UTAC (Singapore) Ltd., Corporate HQ – 2 factories WS, Assembly and Final Test Facility, Memory and Mixed-Signal I/C Package R&D and Design, Test Development Operations established 1997

■ UTAC's Manufacturing Facilities in Singapore, Taiwan, China, and Thailand are supported by a global sales network in the US, Europe, and Asia.

■ UTAC's Worldwide Sales Offices are located in Fremont and Irvine, CA; Dallas and Austin, TX (USA); UK and Italy (Europe); and Japan, Korea, China, Taiwan, Thailand, and Singapore (Asia).

#### www.meptec.org

# Main C Patterning Technology

# Automated Double-Sided Overlay Metrology

Keith A. Cooper and Thomas Huelsmann SUSS MicroTec

he growth of MEMS devices and other technologies using double-sided patterning has led to a maturing of MEMS manufacturing processes. Along with such techniques as deep silicon etch and release of mechanical structures, MEMS devices have likewise taken novel lithography processes to a new level of maturity and broad use. Patterning of very thick photoresist layers, etching of hundreds of microns of silicon, and double-sided lithography - techniques with only limited application a few years ago - have now been brought into the mainstream for MEMS process flows.

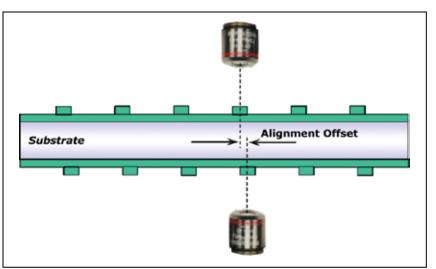

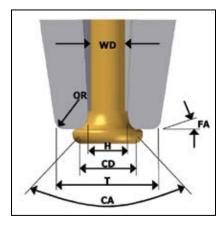

As these techniques become more commonplace, the equipment set to perform these process steps must also grow and evolve. Demand for new MEMS device features as well as greater functionality within existing devices has fueled a demand for more efficient use of wafer real estate on the front and backside of the wafer. Device layouts may require frontside to backside overlay of  $1\mu$ m; this trend toward smaller feature sizes and tighter front-back registration has driven a need for tighter registration of frontside to backside features, as well as a need for overlay metrology tools. And as backside patterning moves toward greater production volumes, so also must the backside metrology tools provide automated measurement for production scenarios.

The concept of double-sided patterning is not new – it has been present in the process flow of MEMS and communication devices for many years. Si pressure sensors, GaAs telecom chips, InP lasers, and many other such devices have utilized the backside of the wafer, either for device functionality or due to cost pressures to capture and utilize otherwise wasted substrate real estate.

The earlier uses of backside lithography employed viewing systems with infrared (IR) illumination; the proper choice of IR illumination source coupled with an IR-sensitive camera yielded sufficient clarity in the image to perform alignments of frontside to backside features on many materials included GaAs, InP and in some cases Si. But not all substrates yielded a

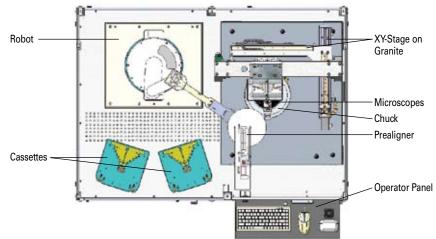

Figure 1. Layout of SUSS DSM200 Automated Metrology Tool.

reasonable image to align, particularly metallized circuits, Si substrates with high B-doping levels, or other inherently IRopaque materials such as Al203. Due to this material opacity problem and the need to perform tighter front-back alignments for smaller features, savvy equipment suppliers designed imaging systems which employ image-capturing software so that back and front of substrate can be viewed simultaneously even with highly opaque materials. Despite the ease of use and therefore popularity of this double-sided alignment technique, IR is still valuable for buried circuit layers and other device layouts and is used for those process schemes.

Many of these MEMS or optoelectronic devices have undergone the customary shrinkage of geometries in order to make the circuits smaller, faster or more cost-competitive. With this reduction in feature size comes the requisite tightening of alignment tolerance for front-front or front-back overlay. This progression is only natural as the devices become more mature or as the cost of such circuits is reduced in an effort to create broader market appeal. In their 2006 Global MEMS newsletter, Yole Developpement has projected a 13% CAGR across many MEMS devices, with many of these requiring backside patterning and the corresponding front-to-backside metrology steps.

But as the market for such devices grows and the production volumes ramp significantly, so does the need to automate the process and metrology steps to keep the cost of ownership (COO) in line with market demand. There is a clear and present need provide automated metrology systems to provide process control for these processes requiring backside alignment. The requirements of such a tool would include:

- Hands-off metrology on various sized wafers up to 8"

- Robotic handling to process various sized, often fragile, substrates with high throughput

- Access to multiple arbitrary measurement locations for process and metrology flexibility

- Repeatability, reproducibility, and accuracy

- Diagnostics/Factory Automation: auto-calibration, auto-diagnostics, SECS/GEM interface

Figure 1 shows a block diagram in plan view of a tool designed to meet these requirements. With a granite base for machine stability and a flat reference surface, the tool incorporates an XY translation stage mounted atop the granite so that

Figure 2. View of tool with robotic handling, cassettes and non-contact prealigner.

all motions are carried out with minimal friction. This granite has been polished to a total surface finish of  $2\mu m$  over its entire surface to minimize or eliminate the need for re-focusing between measurement sites.

A field-proven robotic handling system with a non-contact prealigner (Figure 2) also provides a fast and easy method to change wafer sizes or materials without any mechanical changeover of prealigner or robot end-effector. Since the tool operates completely in a hands-off mode, it can measure and report frontside to backside metrology results at a throughput of 50 wafers/hour, and the results are completely independent of the operator. Edge handling is also available for those applications where exclusion areas on the wafer dictate a certain rim of handling area. This feature is especially attractive for MEMS or optolelectronic applications where the optical and mechanical functionality of the features is particularly susceptible to damage from handling. To accommodate an advanced production scenario incorporating factory automation, SEC/GEM interface, RF ID reader for the cassettes and wafer ID reader are all available.

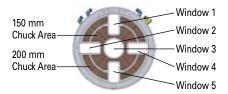

To provide freedom and flexibility in choosing the overlay verification sites, the chuck has large viewing areas with unobstructed access to the top and bottom sides of the wafer. (See Figure 3) This ensures not only that features critical to the device's performance will be visible, but also that there is no optical shift and ensuing overlay offset in the measurement process created by any uncharacterized optical aberrations in the chuck material. More than 4000mm2 on a 6" SEMI wafer is available for viewing.

The measurement of the top-bottom

Figure 3. Typical Layout of 150mm wafer Chuck.

Figure 4. Layout of vertically superimposing microscope for fiducial measurement.

overlay is carried out by a vertical superimposed microscope, depicted in Figure 4. The measurement technique is to simultaneously view the top and bottom fiducial images with CCD cameras, then determine the relative position or these two targets using a pattern recognition algorithm based on the Cognex Patmax software. Typical fiducials for the overlay metrology tool are the same as those used for preceding lithographic alignment; targets may be between 30 and  $300\mu m$ , and are most typically about  $100\mu m$  in X and Y. The Cognex system utilizes a very durable and field-proven software platform so that the system is impervious to variations in contrast, rotation of the images, and even reversal of the image tone.

After determining top-bottom overlay at this first site, the alignment stage is automatically moved to position the alignment fiducials for each of the desired locations into the field of view of the cameras and the process repeats.

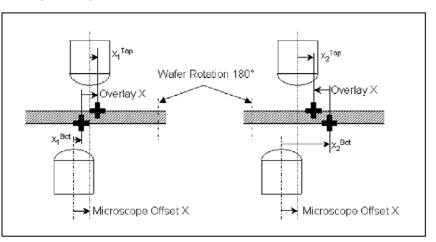

One main challenge in precisely measuring the alignment accuracy of structures on the top and bottom side of the wafer lies in several mechanical imperfections that occur during operation, like the offset between the optical axis of the microscope. In order to maintain control of these deviations each time a wafer is measured, the DSM200 rotates the substrate automatically by 180° at the end of the first measurement cycle, as depicted in Figure 5. In this way errors such as misalignment in the optical axis of the microscopes can be eliminated so the final result is accurate and trustworthy for all measurement sites.

The final overlay between the top and bottom target is calculated by the follow-ing:

$$Overlay X = \frac{1}{2} \cdot [(x_1^{Top} - x_2^{Top}) - (x_1^{Bot} - x_2^{Bot})]$$

$$Overlay Y = \frac{1}{2} \cdot [(y_1^{Top} - y_2^{Top}) - (y_1^{Bot} - y_2^{Bot})]$$

Figure 5. The DSM Principle of Operation.

# Made Patterning Technology

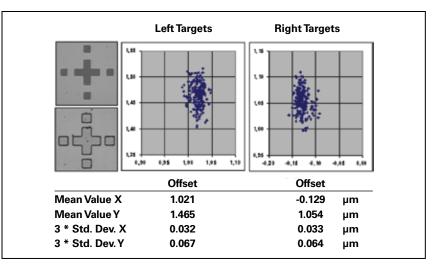

For any metrology tool to be effective, it must deliver consistent results as measured by repeatability and accuracy. To measure repeatability, a Si wafer was printed on a double-sided lithography tool from SUSS MicroTec, followed by developing of the resist features to create optically visible lithographic features. After development of the resist, the patterned wafer was loaded into cassettes and measured in the DSM200 tool as described above.

Detection repeatability can be quantified by loading a sample into the measurement tool, recording the indicated overlay repeatedly, then performing statistical analysis of the output data. Detection repeatability can be explored further by unloading and loading the same sample multiple iterations, measuring the overlay each time and analyzing the data for evidence of drift or fluctuation.

Potential sources for detection repeatability error would include mechanical drift in the stages for wafer chucking or objective/camera mounts, uncertainties in the position detection algorithm, vibration in the tool, and thermal drift. Any one of these sources can contribute significant error which would disqualify the tool for its intended use, and must be carefully considered from a system-level point of view from the ground up when designing the tool.

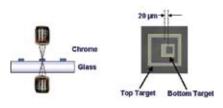

Measurement accuracy for the tool was quantified by means of measuring a transparent substrate with very thin patterns of Cr on one side, similar to a lithographic photomask. A quartz substrate, 1mm thick, with optical transparency and consistency parallel to photomasks was patterned with a laser writer, then the patterned features were transferred into the underlying Cr layer by means of dry etching. The overlay of these Cr images can be measured by a benchmark topside-topside metrology tool such as the Vistec LMS. Then this wafer was measured on the SUSS DSM200 by using the top side microscope to look at one top side feature while the bottom side microscope looks also at the same feature (for an anticipated  $0\mu m$  overlay) or an adjacent top side feature (for an anticipated  $20\mu m$  overlay), as shown in Figure 6.

Figure 6. Measuring the top-to-bottom "overlay" of a transparent substrate to quantify the tool accuracy.

Figure 7. Detection repeatability for 2000 measurement cycles.

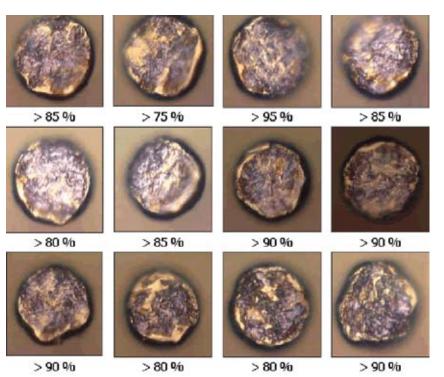

For any metrology to meet the measurement requirements, it needs to deliver a very tight grouping of overlay readings, indicating a very high detection repeatability. Results from the tests described above for the DSM200 are depicted in Figure 7, with 2000 total measurement cycles at multiple sites. The data indicate  $0.035\mu$ m for the X direction and  $0.067\mu$ m for the Y direction, both at 3 sigma, indicating that the tool does supply the requisite detection repeatability for a front-back overlay requirement of  $1\mu$ m or better.

Even if a metrology tool can repeatedly detect the apparent overlay error between 2 features, this information is nearly useless unless there is likewise a correlation between the metrology tool's results and some external measurement standard. Results from the accuracy tests using the transparent substrate with Cr features are plotted in Figure 8 and show a mean + 3 sigma value less than or equal to  $0.15\mu$ m, well within the range of performance required for current or coming generations of devices requiring front-tobackside overlay.

#### Conclusions

A growing demand for high quality frontside to backside lithography processes has likewise generated a need for an accurate, automated tool to quantify the overlay for such processes. Operating in a cassette-cassette mode for high throughput, such a tool has been designed and qualified to provide overlay metrology for technologies such as MEMS, 3D Integration, and other devices with front to back registration requirements down to  $1\mu$ m or tighter.

| Glass Te<br>with 0 µ | st Wafer<br>m Overlay |        |          |                 |                     |

|----------------------|-----------------------|--------|----------|-----------------|---------------------|

| Results              |                       |        | Target 3 | 0.2             |                     |

| Target               | Mean X                | Mean Y |          | 42 41 8 42      |                     |