# MCM Package Development of In-Vehicle Infotainment System

10/23/2014

Terry Kang, Ron Boja & Abraham Yee

Advanced Technology Group

### Contents

- In-Vehicle Infotainment System Introduction

- Key Technical Challenges & Solutions

- Package Design

- Assembly Process and Material

- Automotive Package Reliability

- Summary

# **In-Vehicle Infotainment System**

Source: NVIDIA Website

In-vehicle infotainment is a integration of hardware devices to provide audio, visual entertainment and automotive navigation system.

# **NVIDIA's VCM (Visual Computing Module)**

#### Size: 85mm X 85mm

#### Size: 42.5mm x 42.5mm

- Smaller size (75% area reduction)

- Higher electrical performance

- Lower cost

- Wider adoption

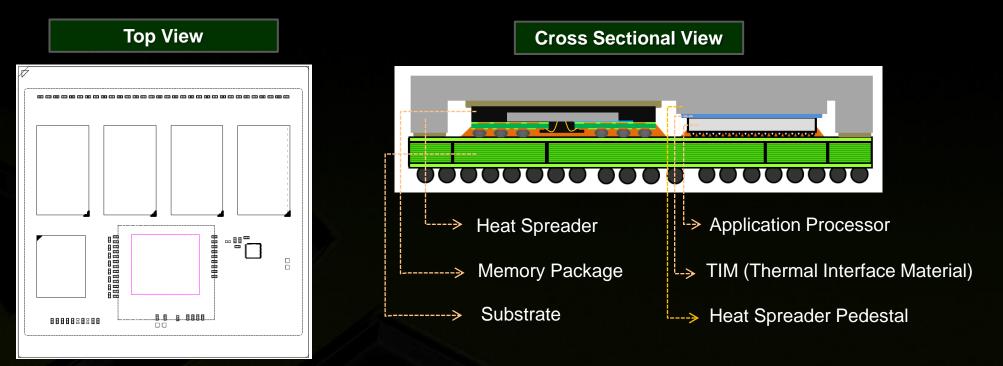

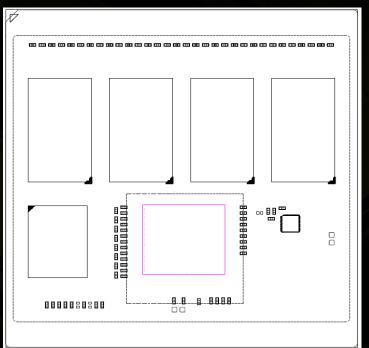

# **VCM MCM Package Introduction**

- 42.5mm x 42.5mm FCBGA with lid, 1208 Balls

- Integrated with AP, memory, flash, thermal sensor and passives

- Heat-spreader with pedestal design

- Standard substrate core and build up material

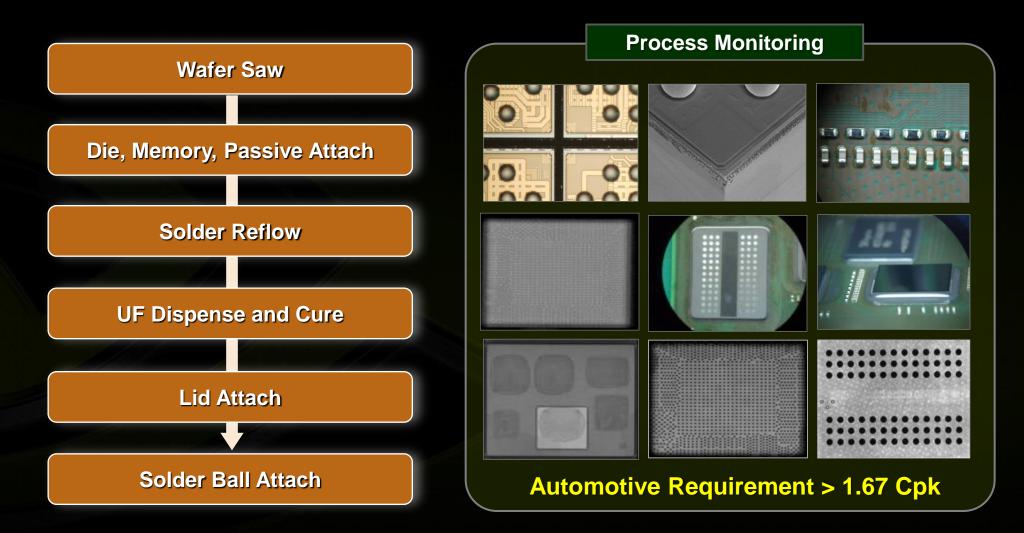

# **Assembly Process Flow**

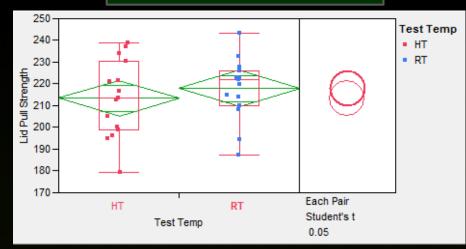

# **Lid Adhesion Strength**

#### Lid to Substrate Contact Area

|                                     |      | МСМ  |      |      |

|-------------------------------------|------|------|------|------|

|                                     | А    | В    | С    | VCM  |

| PKG Body (mm2)                      | 45   | 42.5 | 42.5 | 42.5 |

| Lid foot (mm2)                      | 5    | 5    | 5    | 3.5  |

| Lid to Substrate Contact Area (mm2) | 560  | 407  | 380  | 690  |

| Contact Area vs. PKG Body Ratio     | 0.28 | 0.23 | 0.21 | 0.38 |

#### Lid Pull Test Set-up

#### Lid Pull Test Result

- Lid Pull Adhesion

- Min: 187 Kg (RT), 179 Kg (HT)

- Max: 243 Kg (RT), 238 Kg (HT)

- Ave: 217 Kg (RT), 213 Kg (HT)

- Above spec, 145Kg (min)

- Cohesive failure

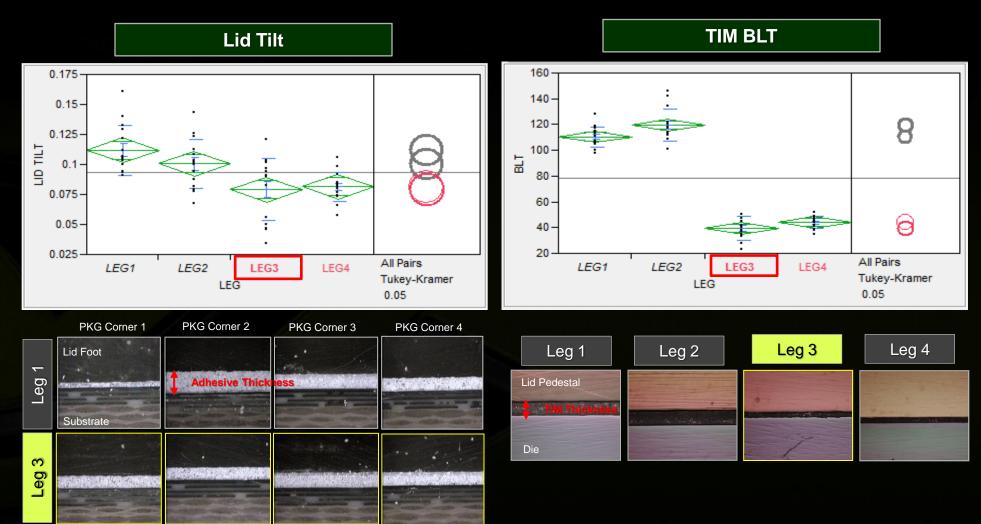

# Lid Tilt and TIM BLT Control

#### **Technical Challenges**

- Asymmetrical package floor plan

- Thinner flip chip die thickness than memory package

- TIM BLT requirement on flip chip die

- Special lid design

#### Solutions

- Adhesive and TIM volume control

- Lid foot height control

- Lid pedestal height optimization

# Lid Pedestal Height Optimization

2014 MEPTEC Packaging Technology Symposium

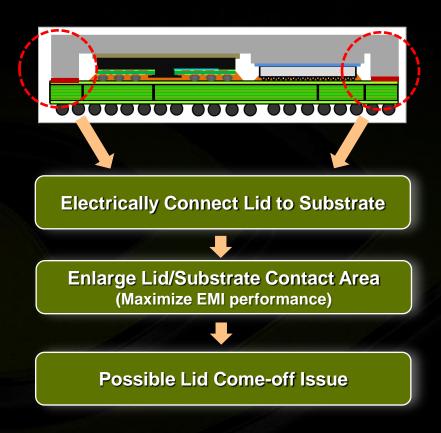

# Lid Ground for EMI Shielding

#### **Technical Challenges**

- Poor adhesion of conductive materials

- Resistivity increase during package reliability test

- Lid ground pad design on substrate

#### Solutions

- Optimize conductive material properties

- No significant R increase

- Good adhesion

- Select GND pad finish compatible with conductive material

- Lid ground pad design

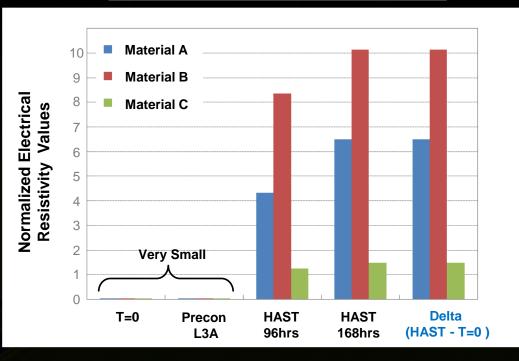

# **Conductive Material Evaluation**

**Electrically Conductive Material Candidates**

|                    | А      | В    | С      |

|--------------------|--------|------|--------|

| Volume Resistivity | High   | Low  | Medium |

| Tg (C)             | Medium | Low  | High   |

| C.T.E (ppm)        | Low    | High | Medium |

- No significant resistivity increase after T=0 and Precon

- High resistivity increase after HAST

- No correlation between initial material electrical resistivity and post package reliability test

**Resistivity Measurement Results**

## **AEC-Q100**

Automotive Electronics Council - Qualification 100 (Stress Test Qualification for Integrated Circuits)

#### Purpose

To determine that a device is capable of passing the specified stress tests and thus can be expected to give a certain level of quality/reliability in the automotive application

#### Definition of Part Operating Temperature Grade

- Grade 0: -40°C to +150°C

- Grade 1: -40°C to +125°C

- Grade 2: -40°C to +105°C

- Grade 3: -40°C to +85°C

- Grade 4: 0°C to +70°C

# **Example of AEC-Q100 Tests**

| TEST GROUP A – ACCELERATED ENVIRONMENT STRESS TESTS (CONTINUED) |      |    |                     |                      |                   |                    |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------|------|----|---------------------|----------------------|-------------------|--------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STRESS                                                          | ABV  | #  | NOTES               | SAMPLE<br>SIZE / LOT | NUMBER<br>OF LOTS | ACCEPT<br>CRITERIA | TEST<br>METHOD                             | ADDITIONAL REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Temperature<br>Cycling                                          | тс   | Α4 | н, р, в,<br>D, G    | 77                   | <u>3</u>          | 0 Faailts          | JEDEC<br>JESD22-<br>A104 and<br>Appendix 3 | <ul> <li>PC before TC for surface mount devices.</li> <li>Grade 0: -65°C to +175°C for 500 cycles, -50°C to +175°C for 2000 cycles, or -50°C to +150°C for 2000 cycles.</li> <li>Grade 1: -65°C to +150°C for 500 cycles or 50°C to +125°C for 1000 cycles.</li> <li>Grade 2: -50°C to +150°C for 500 cycles or 50°C to +125°C for 1000 cycles.</li> <li>Grade 3: -50°C to +125°C for 500 cycles or 50°C to +105°C for 1000 cycles.</li> <li>Grade 4: -10°C to +105°C for 500 cycles or 10°C to +90°C for 1000 cycles.</li> <li>TEST before and after TC at hot temperature.</li> <li>After completion of TC, decap five devices from one lot and perform WBP (test #C2) on corner bonds (2 bonds per corner) and one mid-bond per side on each device. Preferred decap procedure to minimize damage and chance of false data is shown in Appendix 3.</li> </ul> |

| Power<br>Temperature<br>Cycle                                   | РТС  | A5 | H, P, B,<br>D, G    | 45                   | 1                 | 0 FAILS            | JEDEC<br>JESD22-<br>A105                   | PC 22pcs before PTC for surface mount devices.<br>Testrequired only on devices with maximum rated<br>power = 1 watt or $\Delta T_J = 40^{\circ}$ C or devices designed<br>to drive inductive loads.<br>Grade 0: T <sub>a</sub> of -40°C to +150°C for 1000 cycles.<br>Grade 1: T <sub>a</sub> of -40°C to +125°C for 1000 cycles.<br>Grade 2 to 4: T <sub>a</sub> -40°C to +105°C for 1000<br>cycles.<br>Thermal shut-down shall not occur during this test.<br>TEST before and after PTC at room and hot<br>temperature.                                                                                                                                                                                                                                                                                                                                        |

| High Temperature<br>Storage Life                                | HTSL | A6 | Н, Р, В,<br>D, G, К | 45                   | 1                 | 0 FAILS            | JEDEC<br>JESD22-<br>A103                   | Plastic Packaged Parts<br>Grade 0: +175°C for 1000 hours or +150°C for<br>2000 hours.<br>Grade 1: +150°C for 1000 hours or +175°C for<br>500 hours.<br>Grades 2 to 4: +125°C for 1000 hours or<br>+150°C for 500 hours.<br>Ceramic Packaged Parts<br>+250°C for 10 hours or +200°C for 72 hours.<br>TEST before and after HTSL at room and hot<br>temperature.<br>* NOTE: Data from Test B3 (EDR) can be<br>substituted for Test A6 (HTSL) if package and<br>grade level requirements are met.                                                                                                                                                                                                                                                                                                                                                                   |

- Package design was optimized to control warpage, lid adhesion, TIM BLT and lid tilt. Package materials were developed and evaluated to achieve high EMI performance

- Extended package reliability tests were performed to ensure reliability margin

- NVIDIA has successfully developed MCM package to meet automotive reliability requirements and electrical/thermal performances