#### **INSIDE THIS ISSUE**

FPGA makers need to take the lead in initiating the qualification of alternative subcontractors.

The demand for greater cost performance and differentiation has fueled the development of advanced packaging.

Silico SiC : mor

They won't replace silicon, but GaN and SiC are becoming much more attractive as prices drop.

Binghamton University Professor of Chemistry and Materials Science wins Nobel Prize in Chemistry.

# Cutting-edge solutions for 5G applications

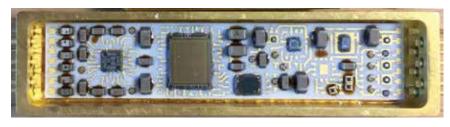

Amkor is the first OSAT to deliver high volume manufacturing of products using Antenna in Package (AiP)/ Antenna on Package (AoP) technology. Our fully-integrated 5G NR millimeter wave (mmWave) and sub-6 GHz RF modules deliver capabilities across several spectrum bands utilizing a compact footprint.

00

www.amkor.com

The MEPTEC Report is a Publication of the Microelectronics Packaging & Test **Engineering Council**

141 Hewitt Street, Summerville, SC 29486 Tel: (650) 714-1570 Email: bcooper@meptec.org

Publisher MEPCOM LLC Editor Bette Cooper Art Director/Designer Gary Brown Sales Manager Gina Edwards

#### MEPTEC Executive Director

Ira Feldman

MEPTEC Advisory Board

**Board Members**

Ivor Barber AMD

lack Belani Indium Corporation

Joel Camarda Altierre

Calvin Cheung ASE (US) Inc.

Jeff Demmin Booz Allen Hamilton

Douglass Dixon 360 BC Group

Nick Leonardi SMART Microsystems

Phil Marcoux PPM Associates

Herb Reiter eda 2 asic Consulting

**Special Advisors**

Ron lones N-Able Group International

Mary Olsson

Honorary Advisors

Seth Alavi Sunsi

Gary Catlin

Rob Cole

Skip Fehr

Anna Gualtieri Elle Technology

In Memoriam

Bance Hom

#### Contributors

Benson Chan Binghampton University

Ira Feldman Feldman Engineering Corp

Martin Hart TopLine Corporation

Ron lones N-Able Group International

Dr. Randall K. Kirschman R&D Consultant

Mark LaPedus SEMICONDUCTOR ENGINEERING

Kevin Rinebold Mentor®, A Siemens Business

A Quarterly Publication of The Microelectronics Packaging & Test Engineering Council

CALL TO ACTION - A prudent investment today can mitigate the risk of waiting for an unexpected disaster to strike, potentially costing the defense industry hundreds of millions of dollars. A production stoppage of critical FPGA components could ultimately diminish market readiness, possibly tipping the balance of peace in the World Order.

MARTIN HART **TOPLINE CORPORATION**

MARKET TRENDS - They won't replace silicon, but GaN and SiC are becoming much more attractive as prices drop. Several vendors are rolling out the next wave of power semiconductors based on gallium nitride (GaN) and silicon carbide (SiC), setting the stage for a showdown against traditional silicon-based devices in the market.

SEMICONDUCTOR ENGINEERING

MARK LAPEDUS

| Packaging & Assembly for<br>Hectronics<br>Part V - Reliability and Toting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | The series is defined as indexes,<br>the series is defined as a strength<br>of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series is<br>a strength of the series is defined as a strength of the series | States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| And an and a set of the set of th | Second and a secon | A schedule of the second and the schedule of the second and the second and the schedule of the                                                                                  | Hitleho Varanze<br>parts anguges to the<br>The Construction of the<br>The Construction of the Construc-<br>tion of the Construction of the<br>Second Second Second Second Second<br>Second Second Second Second Second<br>Second Second Second Second Second Second<br>Second Second                                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ender of the second sec | I of an EV. (2014) An analysis of the event of the even of the event of the even of the event of the event of the even                                                                                      | Hence is the gate has also availed<br>the cost on any participant, or and of<br>the cost on any participant, or any parti-<br>tion of the second second second second<br>second second second second second second second<br>second second second second second second<br>second second second second second second second second second second<br>second second |  |

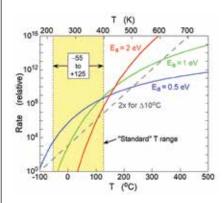

PACKAGING - Parts II, III and IV of this series explored the challenges presented by variations of the basic properties of assembly and packaging materials as temperature is raised. This concluding Part presents a few basic observations on reliability and accelerated testing, in relation to electronics packaging and assembly for high-temperature operation.

**DR. RANDALL K. KIRSCHMAN R&D CONSULTANT FOR ELECTRONICS TECHNOLOGY**

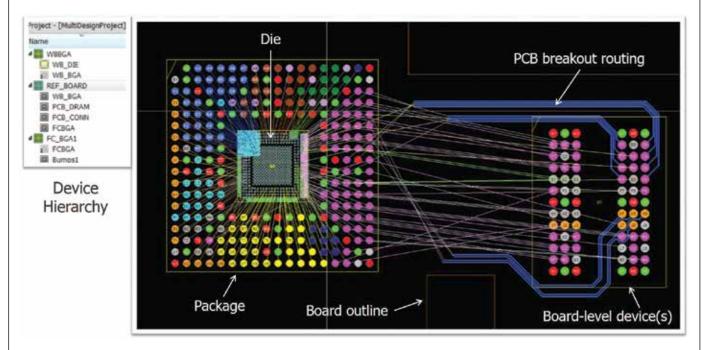

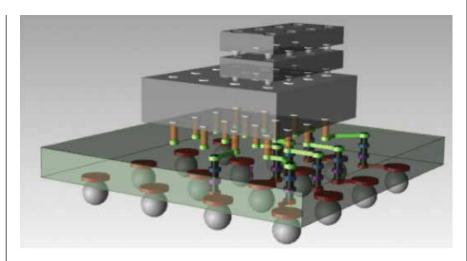

PACKAGING - Heterogeneous packaging is a disruptive impact on traditional design and verification methods. The growth of these designs demands an efficient, proven automated sign-off for physical, electrical, thermal, and manufacturing performance. To ensure consistency and automation a single environment is essential to manage all of these processes.

**KEVIN RINEBOLD MENTOR®, A SIEMENS BUSINESS**

**28** TECH BRIEFS – The State-of-the-Art Technology Briefs contains articles from the Binghamton University S3IP "Flashes." Binghamton University currently has research thrusts in healthcare/medical electronics; 2.5D/3D packaging; power electronics; cybersecure hw/sw systems; photonics; MEMS; and next generation networks, computers and communications.

**BENSON CHAN BINGHAMPTON UNIVERSITY**

# DEPARTMENTS

4 Call to Action 5 Up Front

6 Member News II Coupling & Crosstalk 13 Industry Insights

MEPTEC Report Vol. 23, No. 4. Published quarterly by MEPCOM LLC, 141 Hewitt Street, Summerville, SC 29486. Copyright 2020 by MEPCOM LLC. All rights reserved. Materials may not be reproduced in whole or in part without written permission. MEPTEC Report is sent without charge to members of MEPTEC. For non-members, yearly subscriptions are available for \$75 in the United States, \$80US in Canada and Mexico, and \$95US elsewhere. For advertising rates and information contact Gina Edwards at 408-858-5493.

# CALL TO ACTION

# Does the FPGA Industry Face Peril? Pt. II

Martin Hart TopLine Corporation

PREVIOUSLY, PART I OF THE FALL 2019 MEPTEC REPORT "Call to Action" addressed a concern that the main producers of Field Programmable Gate Arrays (FPGA) rely on a single source subcontractor to attach copper wrapped solder columns as their final production step. The Defense Logistics Agency (DLA) publishes a list of supply chain subcontractors authorized to assemble FPGA devices in the Qualified Manufacturer List (QML-38535).

Stakeholders have reason to be alarmed. A production stoppage of critical FPGA devices could result in the failure of the defense industry to fulfill commitments for delivery of warfighters. Radiation Hardened FPGA packages are constructed to withstand intense radiation and high temperatures in order to satisfy mission requirements.

#### **Supply Chain Resiliency**

Several risk archetypes for achieving a robust and resilient production of FPGA devices include a diminishing domestic manufacturing base and a fragile market as described in the Department of Defense (Presidential Executive Order 13806) Industrial Policy report titled, "Assessing and Strengthening the Manufacturing and Defense Industrial Base and Supply Chain Resiliency of the United States". FPGA packages with solder columns are produced in a low-volume manufacturing environment; as such, around 75,000 individual FPGA devices spread over 100 different outline packages are produced annually. Total annual volumes of 70 million copper wrapped solder columns are minuscule when compared to volumes of Commercial Off-The-Shelf (COTS) FPGA devices consuming billions of solder balls.

Attaching solder columns to FPGA packages is substantially different from attaching solder balls that dominate the COTS market. Solder columns are cylindrically shaped pins that must be held

|   | CAGE Code | Parent Company                       |  |  |

|---|-----------|--------------------------------------|--|--|

| 1 | 1RU44     | BAE Systems PLC                      |  |  |

| 2 | 65342     | Cobham plc                           |  |  |

| 3 | 65786     | Cypress Semiconductor, Inc           |  |  |

| 3 |           | Acquired by Infineon Technologies AG |  |  |

| 4 | 34168     | Honeywell International, Inc         |  |  |

| 5 | 0J4Z0     | Microchip (Microsemi)                |  |  |

| 6 | F7400     | Microchip (Atmel)                    |  |  |

| 7 | OC7V7     | Teledyne Technologies Incorporated   |  |  |

| 8 | 01295     | Texas Instruments Incorporated       |  |  |

| 9 | 68994     | Xilinx Incorporated                  |  |  |

Producers of FPGA devices with solder columns (in Alphabetical order).

vertically in place by precision machined fixtures without slanting or falling over at any time during the entire attachment and reflow process. A final assembly step requires that the entire matrix array of up to 1752 columns be planarized without damaging a single column. No manufacturing defects are allowed. Talented operator skills must be employed during every step in the process of attaching columns to FPGA packages. Attaching copper wrapped solder columns to FPGA packages is fundamentally a non-automated, artisan process.

Fortunately, royalty-free, U.S. manufactured copper wrapped solder columns are readily available today in the supply chain without delay. However, starting from scratch, it could take 24 months for alternative subcontractors to undergo the arduous process of attaining QML status for column attachment services.

#### Monetary Considerations

Companies that produce FPGA devices are not required to voluntarily qualify multiple subcontractors to attach copperwrapped solder columns to their products. A lack of funding by FPGA manufacturing is most often cited as the primary reason for not qualifying a second source. Multiple microelectronic subcontractors in the supply chain are ready, willing and able to provide column attachment services as long as funding is available to pay for the cost of QML qualification. A sizable investment would be required to support an accelerated initiative by FPGA makers to mitigate risk and qualify multiple subcontractors to attach copper wrapped solder columns. FPGA makers need to take the lead in initiating the qualification of alternative subcontractors. As a practical matter subcontractors cannot independently apply for QML status without the support of the FPGA maker.

#### Conclusion

It's time for advocacy stakeholders to initiate a shared vision to ensure a robust, resilient and sustainable supply chain for FPGA devices. Domestic manufacturing of copper wrapped solder columns is already available. The next step is to qualify multiple microelectronic subcontractors who are ready and willing to provide the critical process of copper wrapped column attachment services for FPGA packages. A prudent investment today can mitigate the risk of waiting for an unexpected disaster to strike, potentially costing the defense industry hundreds of millions of dollars. A production stoppage of critical FPGA components could ultimately diminish market readiness, possibly tipping the balance of peace in the World Order.

# UP FRONT

# Warming Up to 2020

Ira Feldman Executive Director. MEPTEC

#### WELCOME! FROM LONG TIME

MEPTEC members to recent subscribers to casual visitors, we are glad you are here.

The cold of winter has started in North America. It's true that here in Silicon Valley we are blessed with moderate temperatures. However, the chill is in the air hopefully accompanied by much needed rain. Some find this time of year dreary, but I enjoy the warmth of the holidays spent with family and friends.

We had a very well attended annual MEPTEC holiday gathering. Okay truth be told it was the December Semiconductor Industry Speaker Series luncheon. Beyond wishing everyone 'happy holidays' and catching up with industry

friends, there was a great lunch including holiday treats. Not to mention Jan Vardaman's (TechSearch International), now traditional yearly Industry Outlook on "Advanced Packaging for 2020 and Beyond". Jan always brings a fresh perspective to things and was not shy about sharing her thoughts! There will be plenty of other great luncheon presentations during 2020 so stay tuned as we announce them.

Our next full day event is the Known Good Die (KGD) Workshop on Tuesday April 21, 2020 in Silicon Valley. We are excited to celebrate KGD's 20th year as this critical topic is revisited! Don't miss the keynote "Making KGD Silicon Work in Your Supply Chain" by David Greenlaw, Nvidia VP Product Engineering. Please see the event information on page 14 and http://www.kgdworkshop.org/ for more information.

The Advisory Board (AB) has been busy planning our event calendar for 2020. We will be announcing the other full day events and luncheons shortly.

I look forward to hearing your suggestions and feedback as to how MEPTEC can best serve you. Don't be shy!

Happy holidays to you and yours!

Ira Feldman Executive Director, MEPTEC ira@meptec.org +1 650-472-1192

Ouik-Pak

A Division of Promex Industries

#### **Open-molded/Pre-molded Air Cavity Plastic QFN/SOIC Packages** (OmPP<sup>®</sup>) – perfect for RF/MW,

MEMS and sensor applications

Body sizes 3x3 mm to 12x12 mm, lead pitch sizes 0.80 mm to 0.40 mm

- Gold plated for superior bondability

- · JEDEC standard outlines

- Matching ceramic, plastic, quartz and glass lids with epoxy seals

- **RoHS- and REACH-compliant** green molding compound

- · Available in high volumes and off-the-shelf stock

#### Wafer Preparation Services

Dicing, backgrinding, pick & place

#### **Open Cavity Plastic Packages**

(OCPP<sup>™</sup>) – ideal for rapid IC prototype assembly, design verification and

customer samples

Available in any plastic package

Faster Time to Market for Your IC Designs

- Mechanically and electronically identical to production parts

- Turn-around in 24 hours or less with no minimum orders

#### Plastic Overmolded Packages -

for prototype to production volumes

- Overmolded metal leadframe arrays

- Saw-singulated chip scale

- packages including QFN and DFN

- · Wire bonded and flip chip devices

#### Custom Air Cavity Packages -

created for your device in a variety of body sizes/ shapes, lead counts and materials with custom encapsulation

matching made-to-order lids or

#### **Quick-Turn Assembly Services**

- High-volume precision die attach

- Al and Au wirebond

- Multiple encapsulation options

- Flip chip assembly

- · Custom assembly for complex packages (stacked die, COB, COF, SIP. MCM. MEMS. BGA. embedded thermal sensors and laminate arrays)

1.858.674.4676 | email sales@icproto.com | www.icproto.com

All manufacturing

# HENKEL APPOINTS NEW CFO

Effective January 1, 2020, Marco Swoboda, Corporate Senior Vice President Finance, will become new Chief Financial Officer of Henkel. He will succeed Carsten Knobel who will take over the position as CEO effective January 1, 2020. "We are pleased to name Marco Swoboda as a highly qualified successor to our Chief Financial Officer from within our organization. He has strong financial expertise with many years of international experience," said Dr. Simone Bagel-Trah, Chairwoman of the Shareholders' Committee and the Supervisory Board. www.henkel.com

#### MITSUNOBU KOSHIBA OF JSR TO RECEIVE SEMI SALES AND MARKETING EXCELLENCE AWARD

SEMI has announced that Mitsunobu (Nobu) Koshiba of JSR Corporation has won the SEMI Sales and Marketing Excellence Award, inspired by Bob Graham, for 2019. The 22nd recipient of the award. Koshiba was honored for his role in developing and bringing to market multiple photoresist generations that have been critical to the semiconductor industry. He will be recognized during ceremonies at SEMICON Japan 2019, December 11-13, in Tokyo. www.semi.org

#### ANALOG APPOINTS DR. SUSIE WEE TO BOARD OF DIRECTORS

Analog Devices, Inc. has announced the appointment of Dr. Susie Wee to the Board of Directors as an independent director, effective November 29, 2019.

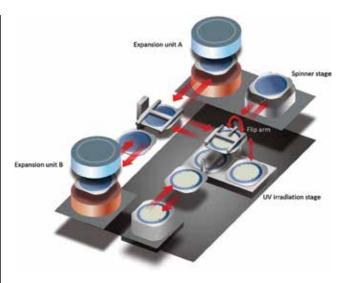

# Improved Productivity and Reliability for Thin Memory Chips

Development of DDS2320, Die Separator with Dual Processing Stage

DISCO CORPORATION), A semiconductor manufacturing equipment manufacturer, has developed DDS2320, a fully automatic die separator capable of processing 300 mm wafers that contributes to improved throughput and reliability in memory production. This equipment was exhibited at SEMICON Japan 2019.

Memory demand is expected to increase with the development of IoT, AI, and ADT. As a result, productivity improvement in memory chip manufacturing and improvement of post-processing device reliability will be required more than in the past.

While DISCO had previously introduced the die separator DDS2300 to the market, DD2320 has been newly developed to meet these emergent needs.

#### **Improved Productivity**

Efficient production of thin die is now possible due to the adoption of a newly developed expansion unit.

Cool expansion and heat

shrinking in one unitParallel processing with dual expansion unit

#### Improved Device Reliability Post-Processing

Particle adhesion is reduced by performing processing and transfer after reversing the workpiece, leading to improved device reliability and yield.

• Reverse-side cool expansion / heat shrinking  Reverse-side spinner cleaning/transfer

#### Approximately 40% FootPrint Reduction

In previous models, auxiliary equipment was installed in the area around the main equipment. DDS2320 achieves a smaller footprint by having the auxiliary equipment installed internally. For more information,

visit www.discousa.com.

# SEMI and VLSI Research Unveil End-to-End Semiconductor Manufacturing Industry Report

#### SEMI AND VLSI RESEARCH HAVE

unveiled the *Semiconductor Manufacturing Monitor*, a report covering the semiconductor manufacturing industry from materials to electronic systems. The inaugural report includes comprehensive 2018 and 2019 quarterly data for the semiconductor manufacturing supply chain, a one-quarter outlook, and semiconductor equipment forecast scenarios to 2020.

"The Semiconductor Manufacturing Monitor sets a new standard for semiconductor manufacturing by offering critical insights for making strategic business decisions and investments in our highly dynamic industry," said Ajit Manocha, SEMI president and CEO. "The combination of SEMI's leading benchmark data and VLSI Research's semiconductor manufacturing expertise delivers an unparalleled breadth of market research spanning the entire semiconductor manufacturing supply chain."

Published four times each year, the annual subscription provides information on:

- Electronic systems sales

- IC sales by logic and memory

- Semiconductor manufacturing CapEx

- Foundry, fabless, OSAT and semiconductor equipment company revenues

- Silicon shipments

- Global wafer fab capacity

- IC inventory

This Semiconductor Manufacturing Monitor is ideal for companies requiring cost-effective, comprehensive industry data from trusted sources. Visit www.semi.org to learn more.  $\blacklozenge$

## nepes Corporation to Acquire Deca Technologies Manufacturing Operations

DECA TECHNOLOGIES IS pleased to announce that it has reached an agreement with nepes Corporation whereby nepes will expand its geographic footprint and manufacturing capabilities by taking over the operations of Deca Technologies Philippines manufacturing facility. The investment will permit the expansion of the WLCSP capacity already in mass production and now offer up to 100,000 wafers per month with a dual site capability courtesy of the Korea site in addition to the Philippines facility.

As part of the agreement, nepes has licensed Deca's M-Series technology to further enable the rapid industry adoption of advanced fan-out technology. Deca's revolutionary M-Series with Adaptive Patterning combined with nepes strong experience in fan-out and large panel manufacturing creates a powerful combination for future growth.

Multiple industry research firms have identified M-Series designed into several Tier One handsets in support of a leader in PMIC applications, further announcements are expected to follow as more customers adopt the technology. Integration of nepes' large panel and SIP capabilities with M-Series and Adaptive Patterning will create multiple exciting customer module solution possibilities including advanced heterogeneous integration.

nepes has manufacturing sites in South Korea and China and international sales offices in San Diego, CA and Shanghai, China. Visit www. nepes.co.kr for more. ◆

### NXP Increases Performance and Expands LPC5500 Arm<sup>®</sup> Cortex<sup>®</sup>-M33 Microcontroller Series

NXP SEMICONDUCTORS has announced the availability of its LPC552x/S2x Microcontroller (MCU) family – further extending its performance efficient LPC5500 MCU series with the second of seven families planned for the series. The LPC552x/S2x MCU family offers significant advantages for developers, including pin-, software- and peripheral-compatibility to accelerate time to market, while leveraging 40-nm NVM process technology to deliver a cost- and power-efficient microcontroller platform. The LPC552x/S2x is a mainstream family in LPC5500 series, providing a perfect balance between security, performance efficiency and system integration for general embedded and industrial IoT markets. It combines the high-performance efficiency of the Cortex-M33 core with multiple high-speed interfaces, an integrated power management IC, and rich analog integration. Key features include:

To learn more about the LPC552x/S2x MCU family, visit: www.nxp.com/ LPC552x. ◆

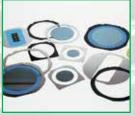

# SPECTRUM IS YOUR HI-REL IC PACKAGE AND LID SOLUTION For Mil-Aero, Automotive, communications, Medical, wireless and avionics applications

Spectrum offers:

- Highly knowledgeable sales staff with decades of Industry Experience

- Highest quality ROHS, REACH, Non-Conflict Minerals and Counterfeit Prevention compliant materials

- ISO-9001:2015 and AS9120B QMS Certified

- Qualified Source for: Mil-Aero, Automotive, Communications, Medical, Wireless, Avionics

- World Wide Same Day Shipping

- Guaranteed On-Time Delivery

- Small Business, Veteran Owned

- Competitive pricing

Located in Silicon Valley for the past 30 years, Spectrum Semiconductor Materials, Inc. is a World Wide Authorized Distributor of packages and lids for IC assembly. Our proven track record, consistent customer service and long-standing supplier relationships makes us the premier distributor for your IC Packaging needs.

Visit www.spectrum-semi.com to see what we can do for you!

155 Nicholson Ln. San Jose, CA 95134 (408) 435-5555 Email: ssm\_sales@spectrum-semi.com

#### MEMBER NEWS

Dr. Wee is the Senior Vice President and General Manager of DevNet and CX Ecosystem Success at Cisco Systems and will serve on the Board's Compensation Committee.

"We are pleased to welcome Susie to the ADI Board. Her extensive experience in information technology and application development, together with her established track record of driving software innovation at global technology companies, will be of great value to ADI and our customers," said Ray Stata, ADI Chairman of the Board.

www.analog.com

# NORDSON MOVES TO NEW OFFICE AND DEMONSTRATION CENTER IN TOKYO

Nordson Corporation announces that Nordson Advanced Technology K.K. Japan has relocated to new, larger office and demonstration facilities in central Tokyo to deliver superior sales, service, technical training, and support to its customers and sales network in Japan. The Nordson Advanced Technology group sells and supports the products from several Nordson divisions (Nordson ASYMTEK, Nordson SELECT, Nordson DAGE, Nordson MARCH, Nordson MATRIX, Nordson SONOSCAN, and Nordson YESTECH) under a unified, in-country team. With the expanded facility, Nordson Advanced Technology K.K. consolidated its fluid dispensing and conformal coating, test and inspection, and plasma treatment equipment into one location. The move was completed in the summer and an opening event was held in October 2019. www.sonoscan.com

# With Sub Micron Accuracy from Lab to Fab

FINETECH'S HIGH-PRE-CISION placement and assembly systems support customers from the photonics and optoelectronics industry in cost-efficient product development and transfer to automated manufacturing. With the newly introduced FINEPLACER® lambda 2 and the high-yield production platform FINEPLACER® femto 2, the Berlin-based precision machine manufacturer offers integrated equipment and process solutions for all product stages from a single source.

As a manufacturer of micro assembly equipment and process technology, Finetech has been supporting start-ups, as well as global technology leaders, for almost three decades in the development of innovative semiconductor products.

They are the first choice for complex multi-stage assemblies with extremely high accuracy requirements,

as well as diverse and very demanding bonding technologies. Applications include the development and production of optical transceivers up to 400 G for data communication, environmental sensors for autonomous driving, or power laser modules for use in industrial and medical applications.

The FINEPLACER<sup>®</sup> lambda 2 is used to place and connect components with an accuracy of better than 0.5 microns - ideal for the high requirements, e.g. in the development of optoelectronic products such as transceivers (TOSA/ROSA) or laser diode modules.

Thanks to the proven FINEPLACER<sup>®</sup> alignment and placement principle with only one moving axis, the system combines highest process quality, stability and accuracy. In conjunction with specially developed optical systems with an optical resolutions down to 0.7  $\mu$ m, it enables superimposed images of the highest optical quality for the reliable detection and alignment of finest structures in the micron range.

For more information, visit www.finetechusa.com. •

#### Mobileye and NIO Partner to Bring Level 4 Autonomous Vehicles to Consumers in China and Beyond

MOBILEYE, AN INTEL COMPANY, AND NIO, a pioneer in China's premium electric vehicle market, are engaging in a strategic collaboration on the development of highly automated and autonomous vehicles (AV) for consumer markets in China and other major territories. As part of the planned cooperation, NIO will engineer and manufacture a self-driving system designed by Mobileye, building on its Level 4 (L4) AV kit. This self-driving system would be the first of its kind, targeting consumer autonomy and engineered for automotive qualification standards, quality, cost and scale. NIO will mass-produce the system for Mobileye and also integrate the technology into its electric vehicle lines for consumer markets and for Mobileye's driverless ride-hailing services. NIO's variants will target initial release in China, with plans to subsequently expand into other global markets.

Under the planned collaboration, Mobileye will provide NIO with the design of the self-driving system building on the Mobileye AV Series, a L4 AV kit comprised of the Mobileye EyeQ<sup>®</sup> system-on-chip, hardware, driving policy, safety software and mapping solution. NIO will take on the automotive-grade engineering, integration and mass-production of Mobileye's system for both consumer automotive markets and for Mobileye's mobility-as-a-service (MaaS) applications. In addition to integrating the self-driving system into its vehicle lines, NIO will develop a specially configured variant of electric AVs that Mobileye will use as robotaxis, deployed for ride-hailing services in global markets.

Visit www.intel.com for more info.  $\blacklozenge$

# Custom Microelectronic Assembly **Think SMART**

Unique Sensor, MEMS, and

**Power Sub-Assemblies**

####

SMART Microsystems works with Design Engineers who need high-guality, low volume microelectronic sub-assemblies for their innovative new products. As North America's leading full-service microelectronic assembly supplier, SMART Microsystems takes complete responsibility for custom process development for your new design, taking it from prototyping through launch in less overall time and cost than other package assembly suppliers.

Call us today at 440-366-4203 or visit our website for more information about our capabilities and services.

**Innovative Microelectronic Solutions.**

141 Innovation Drive, Elyria, Ohio 44035 Telephone: 440.366.4203 info@smartmicrosystems.com

SMART Microsystems is Powered by

HESSE HITACHI Kulicke & Soffa, III LOBOROUTT (Nanotronics (Nordson LATE ESOEC E PELIGHTING

)**9001:2015**

WWW.SMARTMICROSYSTEMS.COM

# BERND HOPS TO HEAD CORPORATE COMMUNICATIONS AT INFINEON

Infineon Technologies AG has announced that effective January 2020 Bernd Hops, currently Head of External Communications, will take over as Head of Communications and Public Authorities & Associations at Infineon Technologies AG. He will succeed Klaus Walther, who held this position from 2013. In this capacity, Mr. Hops will report to Chief Executive Officer Dr. Reinhard Ploss and have global responsibility for internal, external and political communication. www.infineon.com

# INTEL ACQUIRES ARTIFICIAL INTELLI-GENCE CHIPMAKER HABANA LABS

Intel Corporation has announced that it has acquired Habana Labs, an Israel-based developer of programmable deep learning accelerators for the data center for approximately \$2 billion. The combination strengthens Intel's artificial intelligence (AI) portfolio and accelerates its efforts in the nascent, fast-growing AI silicon market, which Intel expects to be greater than \$25 billion by 2024. Intel's Al strategy is grounded in the belief that harnessing the power of AI to improve business outcomes requires a broad mix of technology - hardware and software and full ecosystem support. Today, Intel AI solutions are helping customers turn data into business value and driving meaningful revenue for the company. In 2019, Intel expects to generate over \$3.5 billion in Al-driven revenue, up more than 20 percent year-over-year. www.intel.com

# Henkel Celebrates Groundbreaking of New Plant in Korea

New High-tech Facility as Global Hub for the Electronics Business

HENKEL HAS HELD THE groundbreaking ceremony for a new production facility in the high-tech industrial cluster in Songdo, Korea. With an investment of more than 30 million euros, the new plant will become a global production hub for the electronics business of Henkel Adhesive Technologies.

The Songdo Plant will have a gross area of 10,144m<sup>2</sup> in a two-story building and will commence full production in Q1 of 2022. The new facility will be designed as a high-tech smart factory including a comprehensive building management system (BMS). In addition, the production facilities will fulfill high sustainability standards and be equipped with the state-of-the-art technologies such as solar energy panels, high-efficiency equipment for energy conservation and securing of green land.

For more information, visit www.henkel.com. •

# Intel Research Identifies Digital Skills Gap Slowing Industry 4.0

INTEL HAS RELEASED THE RESULTS OF a new study, "Accelerate Industrial," that represents the most comprehensive view of Industry 4.0, the digital transformation of the manufacturing sector. The research uncovered a serious skills gap that most Western industrial production training programs and government investment initiatives fail to address.

The study found that today's leaders need to create tomorrow's future-ready workforce. This requires the collaboration of universities, government and industry – including initiatives that focus on worker training for the transforming manufacturing sector.

A recent Deloitte/Manufacturing Institute study suggests that industries are entering a period of acute long-term labor shortages, with a shortfall in manufacturing expected to be 2.4 million job openings unfilled by 2028, resulting in a \$2.5 trillion negative impact on the U.S. economy.

The study uncovered the top five challenges

cited by respondents that have the potential to derail investments in smart solutions in the future:

• 36% cite "technical skill gaps" that prevent them from benefiting from their investment.

• 27% cite "data sensitivity" from increasing concerns over data and IP privacy, ownership and management.

• 23% say they lack interoperability between protocols, components, products and systems.

• 22% cite security threats, both in terms of current and emerging vulnerabilities in the factory.

• 18% reference handling data growth in amount and velocity, as well as sense-making.

"Accelerate Industrial" was conducted and authored by Dr. Faith McCreary, a principal engineer, experience architect and researcher at Intel, in tandem with Dr. Irene Petrick, senior director of Industrial Innovation for Intel's Industrial Solutions Division. For more information visit www.intel.com. •

# COLUMN

# COUPLING & CROSSTALK

By Ira Feldman

closer to home.

Electronic coupling is the transfer of energy from one circuit or medium to another. Sometimes it is intentional and sometimes not (crosstalk). I hope that this column, by mixing technology and general observations, is thought-provoking and "couples" with your thinking. Most of the time I will stick to technology but occasional crosstalk diversions may deliver a message

# Trust Your Paranoia!

PRESIDENT RONALD REAGAN'S use of the Russian proverb "*Doveryai, no proveryai*" was the perfect soundbite to describe the 1987 Intermediate-Range Nuclear Forces Treaty. What does this and Andy Grove's "*only the paranoid survive*" have to do with semiconductors?

*"Trust, but verify"* appears to be a nonsensical phrase since verification implies a lack of trust. However, it accurately describes how models of trust work. The extensive process of verification built into the treaty basically meant there was no trust between the United States and the former Soviet Union. But, as each side performed their commitments in a verifiable manner the treaty worked.

Most people trust something until it no longer works. We hop in our car trusting that the brakes will stop the vehicle when needed. Did you take a moment to inspect the brake pads before driving off? Of course not, unless you already suspected a problem. Did you tell a colleague or friend a 'secret'? Will you continue to share with them? Yes, until that trust is broken and something untoward happens. Cases of "blind trust" rarely end well...

A good engineer, by nature and practice, tends to be skeptical. Usually a project needs to be successful the first time or the cost of failure will be too high. We double-check, we cross-check, and sometimes triple-check our process assumptions as well as the calculations and data. The cost of correcting a small error on a semiconductor mask set can run into the millions of dollars. Some endeavors, like space flight, combine the need for first time success without any failures due to the lives at stake and enormous cost.

My son does not fully comprehend why I insist on checking his math homework with him before he is 'done'. Like most high school students, he thinks he is done after he quickly writes out the answers in his notebook but before we go through to check... He hasn't grasped the value in reinforcing his mastery of the material as he attempts to explain his steps (especially those he failed to write out) nor finding simple calculation errors before turning in his homework. Asking him to detail out all the steps of his calculations is our family's current "trust but verify".

"Trust, but verify" appears to be a nonsensical phrase since verification implies a lack of trust. However, it accurately describes how models of trust work.

Semiconductor design using modern electronic design automation (EDA) software has extensive process checks to make sure the design is correct. As the process nodes have shrunk to ever smaller sizes, not only has the non-recurring engineering (NRE) costs increased, but the complexity of the physical process also has increased, resulting in more opportunities for design errors and fabrication yield loss. Most modern integrated circuits (ICs) are designed using a high-level description (HDL), examples include VHDL and Verilog, which provides a 'logical' language (think software code) to describe the desired functionality. The design in HDL can be simulated and analyzed to verify the desired operation. At some point the HDL is expressed as an electrical circuit schematic which is also checked and simulated. This circuit schematic is then translated into a physical layout, i.e. the patterns and shapes of the traces to be processed on the IC.

One of the last checks performed

before the patterns are written on the masks is "physical verification". At this stage the mask patterns are checked against design rules (minimum feature size, minimum clearances, etc.), electrical checks are performed, and layout versus schematic (LVS) is run. LVS calculates the schematic of the patterns - as generated - and compares them against the input schematics. This makes sure the EDA tools did not create an error by adding extra circuitry, neglecting part of the circuitry, or misinterpreting the circuitry. Yes, we trust the tools to operate correctly but it is essential to verify the output to make sure there are no errors. Each and every discrepancy needs to be checked carefully to make sure there are no systemic errors or fatal mistakes. Only after the design team is fully satisfied that everything is correct, does the mask data get sent off to generate the physical glass masks.

At the moment the EDA data becomes physical masks is where nature intrudes and physical variations become the difference between failure and success. Just like a film negative, an error in generating the mask or contamination on the mask will cause defects in every IC patterned. Needless to say, mask fabricators very carefully measure and inspect the masks to insure they match the submitted data.

In the actual IC fabrication process itself there are systemic (process "bias") and random defects that will impact the yield of the individual devices. Hence the need for extensive quality control including "metrology" (measurement) and testing to separate the defective devices from those presumed good. I've previously discussed the need for Known Good Die (KGD) and I hope you will join us as MEPTEC discusses the need and ever present challenges at the upcoming KGD Workshop on April 21, 2020.

In addition to a method for finding the good die, what is needed in terms of trust? Beyond the random variations that cause die to fail, how does one ensure there are no 'bad actors' in one's supply chain? Jeff Demmin (Booz Allen Hamilton and MEPTEC Advisory Board member), touched upon this in his MEPTEC-IMAPS Semiconductor Industry Speaker Series luncheon presentation on September 11, 2019.

Today's distributed global supply chain typically has over a dozen entities 'touching' an IC between fabrication and

# COLUMN

assembly into an electronic sub-system. Most of these companies are located outside of the US. And there are increasing cases of counterfeit ICs being found due to the economic incentives. With the IC itself it is very difficult and costly to confirm that the actual circuits match those of the design and do not contain changes or extraneous circuitry. Unfortunately, reverse engineering an IC is a destructive process. So, one can never say with 100% certainty that a specific IC being used has not been tampered with.

Combined with no longer having domestic companies that are 'trusted' semiconductor foundries available to build complete devices (especially at advanced process nodes) this creates a challenge for defense related applications. In addition to developing methods for detecting the counterfeiting of or tampering with packaged devices, the Defense Advanced Research Projects Agency (DARPA) is driving the development of Heterogenous Integration (HI) based solutions. Their approach is to use HI 'chiplets' developed and fabricated in secure and trusted facilities for the most 'sensitive' functions. These chiplets can

then be integrated with more common building blocks available from the commercial market with less concern as to the level of trust.

So, regardless of one's level of paranoia, processes (as always) need to be established to ensure one's supply chain's quality and security. And the roots of the paranoia expressed by former CEO and Intel co-founder Andy Grove? His biggest concern was that of missing strategic inflection points (SIP) where the fundamentals of the business or available technology have shifted. If a company did not see and respond to these SIP, they may be passed by competitors or left out of a market entirely. Thus, his focus on manufacturing and quality (product and process).

Mr. Grove realized that existing teams have a very large bias towards the status quo. He often used outsiders (other divisions / business units, consultants, etc.) to review things from a fresh perspective. This is similar to having a separate team do the design verification and physical verification of a chip design. Like most audit processes, an outsider may find details overlooked by the those involved in the day-to-day activities.

Bottom line? For any important process, even though you may trust that it is being done 'correctly', you must establish an independent 'audit' or checking process. Be paranoid and trust, but verify. And do not hesitate to ask for 'outside' help!

For more of my thoughts, please see my blog http://hightechbizdev.com.

As always, I look forward to hearing your comments directly. Please contact me to discuss your thoughts or if I can be of any assistance.

IRA FELDMAN is the Principal Consultant of Feldman Engineering Corp. which guides high technology products and services from concept to high volume manufacturing. He engages on a wide range of projects including technical marketing, product-generation processes, supplychain management, and business development.

(ira@feldmanengineering.com)

Stocked in USA www.TanakaWire.com

# COLUMN

# INDUSTRY INSIGHTS

By Ron Jones

# Changes

I'M A SEMICONDUCTOR GUY, through and through. Always have been, always will be.

I started at Signetics R&D in January 1967 and have been in the industry ever since. To put a finer point on it, I am mostly an assembly/test semiconductor guy. If you scratch me, what will flow out is a mixture of die attach epoxy compound and under fill resin.

My first assembly position was at Texas Instruments in 1970 as a die attach and wire bond engineer on TI's first automated assembly line. A couple of years later I was the first engineering manager on the ABACUS automated assembly line building 14/16 plastic DIPs. I was also the manager for the consolidated military high-rel assembly/test operation in TI's Sherman plant.

I joined Amkor in 1985 and shortly after moved to live in Korea as Corporate VP of Worldwide Operations. I next joined Indy Electronics/Olin Interconnect Technologies in Manteca as president. When that facility was sold, I moved to Thailand as CEO of Thai Microsystems.

When Thai Microsystems was sold, I formed N-Able Group International in 1996 – half of our business has been in consulting or recruiting for the semiconductor assembly test arena.

I began my association with MEPTEC in 1990. That is when I first met Bette Cooper and later Gary Brown. We have worked on a number of things together over the years:

- I have attended many, many MEPTEC meetings.

- I joined the advisory board in 1997 and transitioned off in 2010 when the board was scaled down.

- I began writing a column for the MEPTEC Report in 1998 and continue to do so today.

During those many years I've gotten to know Bette and Gary very well. They epitomize semiconductor assembly and test as much as anybody I know. They are knowledgeable, honest and ethical and would do anything in the world for you.

They have provided a real service to the semiconductor assembly and test segment of our industry. The MEPTEC luncheons are a great opportunity for members of our segment to get together, talk shop, and just catch up on being friends. The MEPTEC symposiums are a great way to stay up on industry trends that are taking place in our market.

Technology has certainly changed during my 53 years in the industry. When I began, we were on one-inch wafers and now twelve-inch wafers are typical.

One thing about the semiconductor industry is that there is always change. For Bette and Gary, they moved from Silicon Valley to Medicine Park, OK, then to the Charleston, South Carolina area.

Technology has certainly changed during my 53 years in the industry. When I began, we were on one-inch wafers and now twelve-inch wafers are typical. Then geometries are measured with a yardstick and they are now down in the deep submicron range. A typical device used to be seven masking levels and now it's not unusual to have devices with 50 levels. For all these changes, the typical process steps are spin, expose, develop, etch, deposit/implant, oxidize... Rinse and repeat.

On the other hand, some things never change. Bette and Gary are the same responsible, conscientious, ethical people they have been over the decades that I have known them. In my opinion, the MEPTEC Report is one of the most professionally done industry magazines I have run across, and Gary is one of the most talented graphic artists I know of.

Working with them is a combination of collaboration and Saturday Night Live. Every e-mail contains a zinger of some sort in both directions. You can say whatever you want without fear that it will be taken the wrong way. They are both witty and more than willing to fire salvos but at the same time more than willing to take incoming fire. When I see an incoming email from either of them, I know there'll be something in it to laugh about and the opportunity to fire back.

For many years they have offered a real and valuable service to our industry and have always done it with integrity, honesty and openness.

Some things never change.

This article is not about me, but merely to establish my bona fides as somebody that understands the assembly, packaging and test arena and who has dealt with Bette and Gary for many years. We are lucky to have them providing this service for us and I don't think it would be out of line to say thank you next time you communicate with them.  $\blacklozenge$

RON JONES is CEO of N-Able Group International (NGi); a semiconductor focused consulting and recruiting company. N-Able Group serves clients in the Americas, Asia and Europe. NGi supports the semiconductor supply chain including fabless and IDM semiconductor device companies, wafer foundry and OSAT providers, materials and equipment suppliers, software companies and investors. Email ron.jones@n-ablegroup.com for more info.

# MEPTEC MEDICAL METTER MEDICAL MEDICA

# KNOWN GOOD DIE WORKSHOP 2020 Tuesday, April 21, 2020

SEMI Global Headquarters, Milpitas, California

WW ith the demise of Moore's Law due to the economics of advanced semiconductor process nodes, the demand for greater cost performance and differentiation has fueled the development of advanced packaging. Having Known Good Die (KGD) is essential for many, if not all, of the current 'crop' of advanced packaging including 2.5/3D die stacking, Fan-out Wafer Level Packaging (FOWLP), System in Package (SiP), Heterogeneous Integration (HI), and Panel Level Processing (PLP). Not to mention bare die used in modules and on flex-circuits such as chip on board (CoB), chip on flex (CoF), and chip on glass (CoG).

It is clear that the various functional areas that necessary to have KGD have made progress since the first KGD conference in Napa in 1994. For example, electronic design automation (EDA) design for test (DFT) tools are generating much higher levels of test coverage that historically was the case.

However, these efforts in isolation may not be sufficient especially since issues may cross more than one functional area. Or worse changes in one area may exacerbate problems in another. What is missing is a forum that will take a higher level and cross-functional view of the challenges of producing KGD.

This event will bring together experts to cover topics such as:

- Metrology and Inspection

- Test and Handling

- Big Data and Analytics

- Business Model

- EDA and CAD Tools

#### Limited Sponsorships & Exhibit Tables are Available

For questions about event attendance, sponsorships, or exhibiting, please email Susan Kinne susan@meptec.org.

#### FOR MORE INFORMATION AND TO REGISTER ONLINE TODAY GO TO KGDWORKSHOP.ORG

# Power Semi Wars Begin

*They won't replace silicon, but GaN and SiC are becoming much more attractive as prices drop*

Mark LaPedus, Executive Editor for Manufacturing SEMICONDUCTOR ENGINEERING

#### Reprinted with permission from SEMICONDUCTOR ENGINEERING, October, 23, 2019

SEVERAL VENDORS ARE ROLLING out the next wave of power semiconductors based on gallium nitride (GaN) and silicon carbide (SiC), setting the stage for a showdown against traditional siliconbased devices in the market.

Power semiconductors are specialized transistors that incorporate different and competitive technologies like GaN, SiC and silicon. Power semis operate as a switch in high-voltage applications such as automotive, power supplies, solar and trains. The devices allow the electricity to flow in the "on" state and stop it in the "off" state. They boost the efficiencies and minimize the energy losses in systems.

For years, the power semi market has been dominated by silicon-based devices, namely power MOSFETs and insulatedgate bipolar transistors (IGBTs). Both are mature and inexpensive, but they are also reaching their theoretical limits in several respects.

That's where GaN and SiC fit in. In the market for years, GaN and SiC devices compete against IGBTs and MOSFETs in various segments. Both GaN and SiC are wide-bandgap technologies, meaning they are faster and more efficient than siliconbased devices.

Still, GaN and SiC devices have relatively low adoption rates and won't displace their silicon rivals anytime soon. Today, silicon-based devices have more than 90% market share in the overall power semi market, according to Yole Développement. Generally, GaN and SiC devices are expensive technologies with various challenges.

That's beginning to change because new GaN and SiC devices are making a

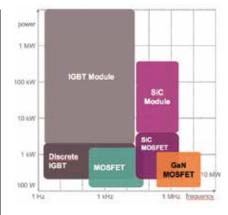

Figure 1. How power switches are categorized. *Source: Infineon*

bigger dent in the market. SiC, for example, is growing at a double-digit pace, compared to single digits for silicon-based devices, according to Yole. "The silicon carbide power device market is expected to grow very fast, driven mainly by the automotive market," said Hong Lin, an analyst at Yole. "The market potential is huge and is attracting a lot of players. We expect the competition to be very strong in the coming years."

GaN is a tiny market today. "When we calculate the growth rate in five years, GaN could be really much bigger than silicon carbide and IGBTs. The market could grow very fast," Lin said.

As it turns out, though, there is no one power semi that fits all needs. There is a place for all technologies. "The total market is growing very quickly. Every device can still have their place, at least for the foreseeable future," Lin said.

Nonetheless, there are a number of events taking place in this market. Among them:

Cree, Rohm and others are increasing their capital spending and building new SiC fabs. Vendors are preparing for huge demand in the battery-electric car market.

- Automotive OEMs are securing supply deals with SiC device makers to meet demand.

- Efficient Power Conversion (EPC), a supplier of GaN power semis, is making what it calls a "frontal assault" against power MOSFETs. GaN is making inroads in various systems.

- Equipment vendors are seeing an uptick in demand in compound semi fabs.

In total, the power device market is expected to grow from \$17.5 billion in 2018 to more than \$21 billion by 2024, according to Yole. Of that, the SiC device market will grow from \$420 million in 2018 to \$564 million in 2019, according to Yole. In 2018, the GaN device market was less than a \$10 million business, according to the firm.

#### The End of Silicon?

In total, the world generates 12 billion kilowatts of power every hour, according to North Carolina State University. More than 80% of the world's electricity is transported through a power electronic system, according to the school.

Power electronics make use of various devices that control and convert electric power in systems, such as cars, motor drives, power supplies, solar and wind turbines.

Generally, power is wasted during the conversion process in systems. In one example, the power wasted in desktop PCs sold in 1 year is equivalent to 17 500MW power plants, according to NC State.

Therefore, the industry requires more efficient devices, such as power semis and other chips. Each power semi is denoted by a numerical figure with a "V" or volt-

MEETINGS & COURSES: February 1-6 CONFERENCE & EXHIBITION: February 4-6 SAN DIEGO CONVENTION CENTER | CA

# ELEVATE THE EXCELLENCE OF ELECTRONICS

# Join Us for What Will be an Excellent Experience in 2020

The pursuit of excellence in electronics is year-round. But, for the six days of IPC APEX EXPO 2020 the focus of the electonics manufacturing industry will be on how collectively we can elevate all aspects of our industry and the products we create. We'll learn together, explore innovative ideas and share our experiences all with an eye toward a future driven by success.

Plan now to elevate your excellence in San Diego at IPC APEX EXPO 2020.

Thank you to our IPC APEX EXPO 2019 volunteers, supporters, sponsors, exhibitors, instructors, speakers, committee leaders and committee members for an outstanding event.

# MARKET TRENDS

age. "The 'V' as in VDSS is the maximum allowed operating voltage, or drain-source voltage specification," explained Alex Lidow, chief executive of EPC. "The terminology 'DSS' means drain-to-source with the gate shorted."

Nonetheless, there are several power semis to choose from. On the silicon front, the choices include power MOSFETs, super-junction power MOSFETs and IGBTs.

Considered the least expensive and most popular device, power MOSFETs are used in adapters, power supplies and other products. They are used in lower-voltage 10- to 500-volt applications.

Super-junction power MOSFETs, which are souped-up MOSFETs, are used in 500- to 900-volt systems. Meanwhile, the leading midrange power semiconductor device is the IGBT, which is used for 1,200-volt to 6.6-kilovolt applications.

MOSFETs compete against GaN devices in the lower voltage segments, while IGBTs and SiC go head-to-head at the high end. All devices compete with one other in the 600- to 900-volt range.

Regardless, IGBTs and power MOS-FETs will remain the mainstream technologies for the foreseeable future. "Silicon is a very mature technology, leading to better cost positions in many aspects, including from a supply chain and internal production processes to existing designs and processes at the customer side," said Gerald Deboy, a senior principal at Infineon. "This is why for many applications silicon-based power switches will continue as the preferred technology for many years."

Silicon-based devices, however, have several limitations, such as high conduction losses and low switching frequencies. Conduction loss is due to the resistance in the device.

That's why OEMs are interested in two wide-bandgap technologies—GaN and SiC. Silicon has a bandgap of 1.1 eV. In comparison, SiC has a bandgap of 3.3 eV, while GaN is 3.4 eV.

"GaN and SiC are wide-bandgap materials, which means higher bonding energy of the atoms in the crystal," said Steven Liu, vice president of corporate marketing at UMC. "SiC and GaN are promising components for the power semiconductor market due to the higher efficiency and smaller form-factor characteristics, compared to their silicon-based peers. The devices can be made much smaller in size for the same relative voltage and current handling capability."

GaN and SiC power semis have been shipping for some time, but they are still expensive. "The manufacturing cost is the main obstacle to market growth, since today both are mainly still using 6-inch and below wafers for production. Once the cost can be improved to a certain threshold, the market size could explode," Liu said.

SiC and GaN are promising components for the power semiconductor market due to the higher efficiency and smaller form-factor characteristics.

Still, there is a place for all power semi types, according to Infineon. Infineon has a unique perspective, given that it sells IGBTs, MOSFETs, GaN and SiC.

"Criteria for selection of a widebandgap device instead of traditional silicon depends on balancing system cost and performance requirements for particular applications," Infineon's Deboy said. "There are various applications where a tipping point in cost and performance goals has been reached for systems based on wide bandgap material. Depending on the specific application, GaN or SiC devices have a better cost position at the system level, even while the GaN or SiC device itself is more expensive than the silicon alternative."

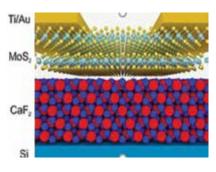

#### What is SiC?

The SiC market is heating up. Suppliers of SiC devices include Cree/Wolfspeed, Infineon, Mitsubishi, On Semiconductor, STMicroelectronics, Rohm and Toshiba.

SiC is a compound semiconductor

material based on silicon and carbon. It has 10 times the breakdown field strength and 3 times better thermal conductivity than silicon.

There are two SiC device types—SiC power MOSFETs and diodes. SiC power MOSFETs are power switching transistors. A diode passes electricity in one direction and blocks it in the opposite direction.

SiC devices are produced in 150mm fabs today, although 200mm is in R&D. In the production flow, a SiC substrate is developed. An epitaxial layer is grown on the substrate. It is then processed into a device.

Making the substrate is the biggest challenge. "This wider bandgap gives the materials interesting qualities such as faster switching and higher power density," said Llewellyn Vaughan-Edmunds, director of strategic marketing at Applied Materials, in a blog. "A major challenge is substrate defects. Basal plane dislocations and screw dislocations can create 'killer defects' that must be reduced for SiC devices to achieve the high yields required for commercial success."

The issues with the SiC substrate translates into higher costs and potential supply constraints during boom cycles. "Cost is a challenge versus silicon or even GaNon-silicon approaches. There are two main reasons—the cost of the SiC substrate and the material yield. Given the tight supply conditions, those prices are unlikely to start dropping soon, but the situation will improve," said Kevin Crofton, president of SPTS Technologies and senior vice president at KLA.

To address the cost issues, some vendors are working on 200mm SiC fabs. This will increase the die per wafer, thereby reducing the cost.

Meanwhile, SiC MOSFETs are based on two structure types—planar and trench. Planar incorporates a traditional sourcegate-drain structure. Trench forms a "U shape" vertical gate channel.

"At the device level, first and second silicon carbide MOSFET generations based upon planar technologies are now well established, but scaling of these technologies to reduce cost and improve performance is technically challenging," said David Haynes, senior director of strategic marketing at Lam Research. "Trenchbased silicon carbide MOSFETs offer the potential to overcome this scaling barrier

# MARKET TRENDS

for key applications in electric vehicles and hybrid electric vehicles, but the performance and reliability of these devices still must improve to address a broader range of automotive applications."

In both cases, suppliers are striving to make good parts with a low on-resistance. This involves unwanted resistance between the source and drain. "My goal is to make every generation with a lower specific on-resistance," said John Palmour, CTO of power and RF at Cree. "It also has to be reliable."