## VISUALIZING THE PACKAGING ROADMAP

IVOR BARBER CORPORATE VICE PRESIDENT, PACKAGING AMD

IEEE EPS Lunchtime Presentation March 2019

AMD

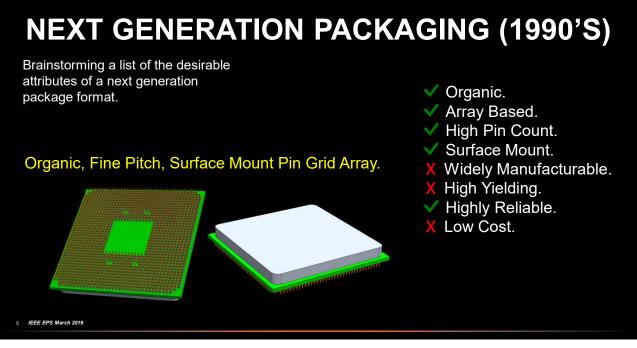

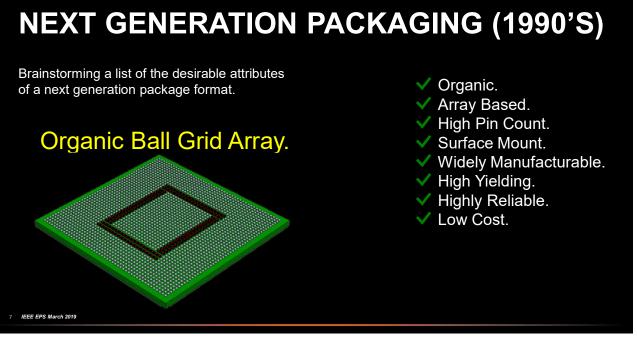

## **NEXT GENERATION PACKAGING (1990'S)**

- Brainstorming a list of the desirable attributes of a next generation package format.

- Organic

- Array Based

- High Pin Count

- Surface Mount

- Highly Manufacturable

- High Yielding

- Highly Reliable

- Low Cost

5

IEEE EPS March 2019

# THE EMERGENCE OF MULTI-DIE PACKAGING

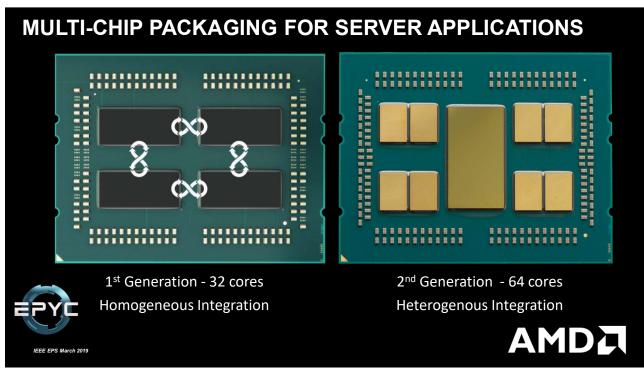

- The slowing of Moore's Law as an economic driver has led to renewed interest in multi-die packaging.

- Traditional SOC scaling has hit cost barriers which make <u>die</u> <u>partitioning</u> economically viable for high end packaging.

- Xilinx used silicon interposers with TSV (2.5D).

- Traditional SOC scaling has fundamental barriers which prohibit monolithic integration of analog, logic and memory circuits.

- Multi-die packaging will replace both Moore's Law and SOC scaling as the economic and technological driving force of the Semiconductor Industry.

Attribution : Bill Bottoms, Various HIR Roadmap Presentations

10 IEEE EPS March 2019

13

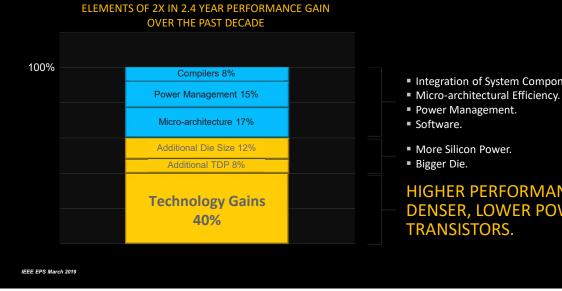

PERFORMANCE GAINS OVER THE PAST DECADE

Integration of System Components.

**HIGHER PERFORMANCE, DENSER, LOWER POWER**

## ACCELERATING THE EXPONENTIAL

#### A BETTER FUTURE DEPENDS ON IMPROVING COMPUTATION EFFICIENCY

NEW APPROACHES NEW ARCHITECTURE

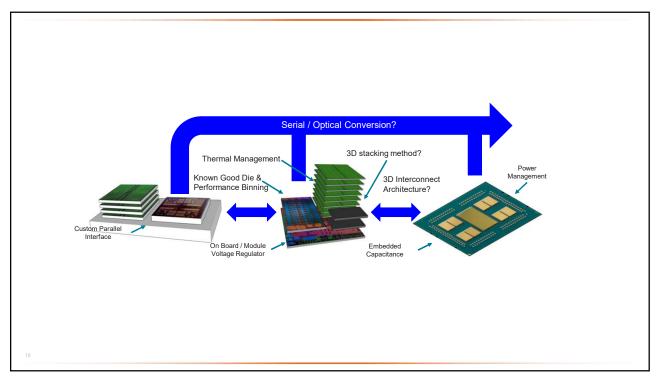

### **NEXT GENERATION PACKAGING**

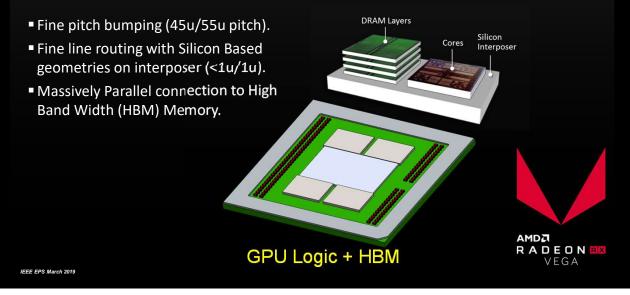

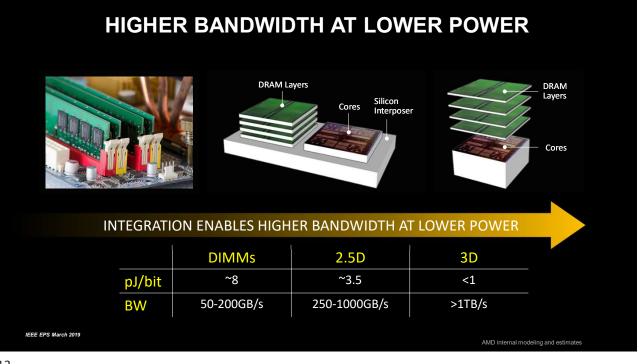

Organic. Array Based. Brainstorming a list of the desirable attributes of a next generation ✓ High Pin Count. package format. Surface Mount. Widely Manufacturable. High Yielding. Highly Reliable. Low Cost. Memory Integration. Massively Parallel Chip-To-Chip Connectivity . Multiple Voltages/Voltage Regulation. Power Reduction/Power Management. lntegrated High Speed/Optical Conversion. 16 IEEE EPS March 2019

#### **END NOTES**

• Slide 14, 15 Lisa T. Su, Samuel Naffziger, and Mark Papermaster, "Multi-Chip Technologies to Unleash Computing Performance Gains over the Next Decade," IEDM Conference 2017".

20 IEEE EPS March 2019