# **Changing Market Requirements** Bring **New Challenges and Opportunities**

Herb Reiter

eda 2 asic Consulting, Inc

herb@eda2asic.com (408) 981 5831

MEPTEC\* Luncheon, February 13, 2019

\*: MicroElectronics Packaging and Test Engineering Council

### Introduction

## **Key Market Data and Requirements**

### Multi-die ICs and Advanced Packaging

### EDA Tools, Flows and Libraries

### Summary

### Herb Reiter's Alliance Management Work

eda2asic

TSMC, UMC, Chartered // IBM, TI, LSI, Lucent, Fujitsu, NEC, Toshiba, Mitsubishi

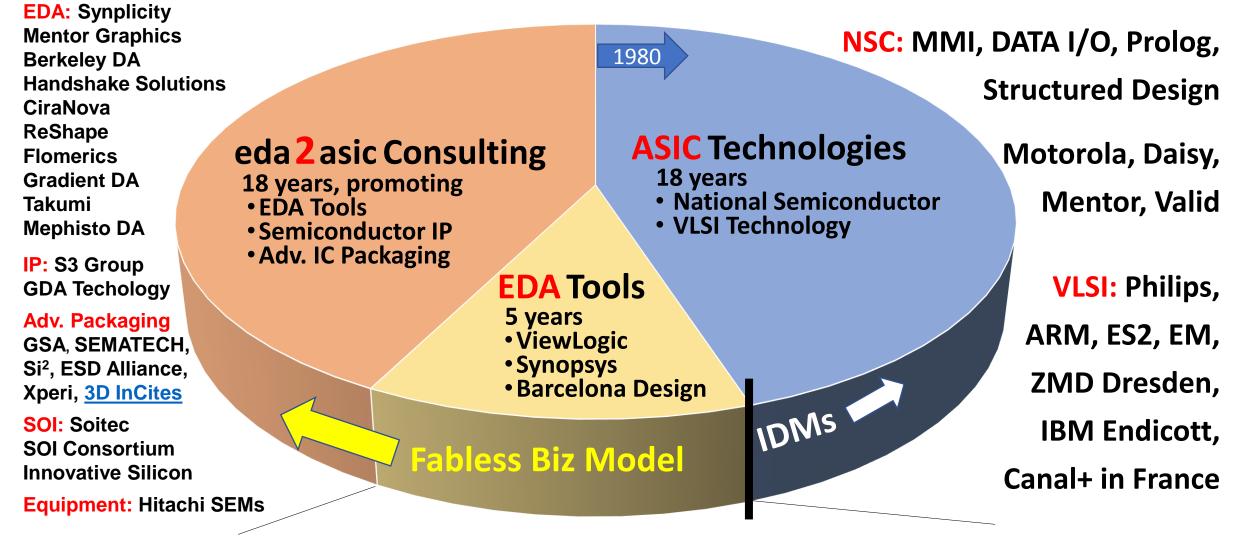

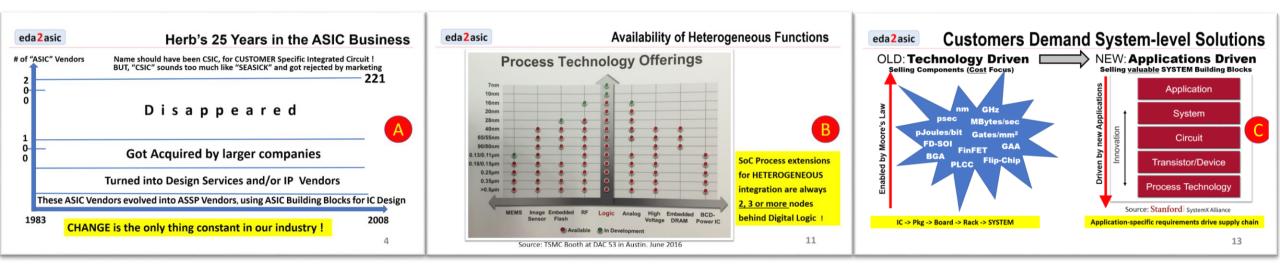

### Herb's 25 Years in the ASIC Business

### Introduction

**Key Market Trends**

Multi-die ICs and Advanced Packaging

EDA Tools, Flows and Libraries

Summary

### **ECOSYSTEM for Electronic Products & Semiconductors**

**Major Market Segments demanding Electronic System Solutions** Communication/5G, Computing, Industrial, Consumer/VR/AR, IoT, Automotive, Mil/Aero, ...

> **Electronic System Vendors** Samsung, Apple, Dell, Lenovo, Huawei, BBK, HP, LG, WD

**Semiconductor Vendors** Samsung, Intel, SK Hynix, Micron, Qualcomm, Broadcom, TI, Toshiba, WD, NXP

Wafer Fabs TSMC, GF, UMC, Samsung, SMIC,.. **OSATs** ASE, Amkor, JCET, ... Semiconductor IP & EDA ARM, SNPS, CDNS, Mentor,...

IC Design Services eSilicon, Open Silicon,...

Materials and Equipment for Manufacturing, Metrology and Test

DowDupont, 3M, BASF, Henkel, ... // AMAT, TEL, LAM, EVG, ... // KLA, Nanometrics, ... // Advantest, ...

Streamlining of ECOSYSTEM-wide cooperation is needed to create attractively-priced electronic products AND decent profit margins!!! 6

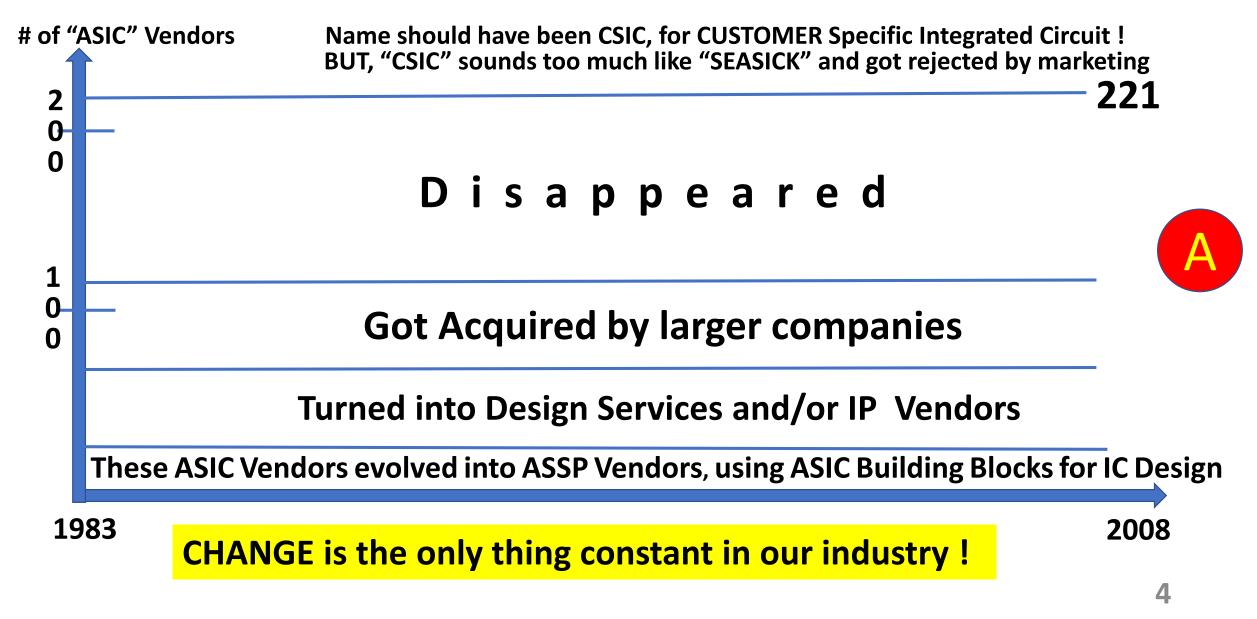

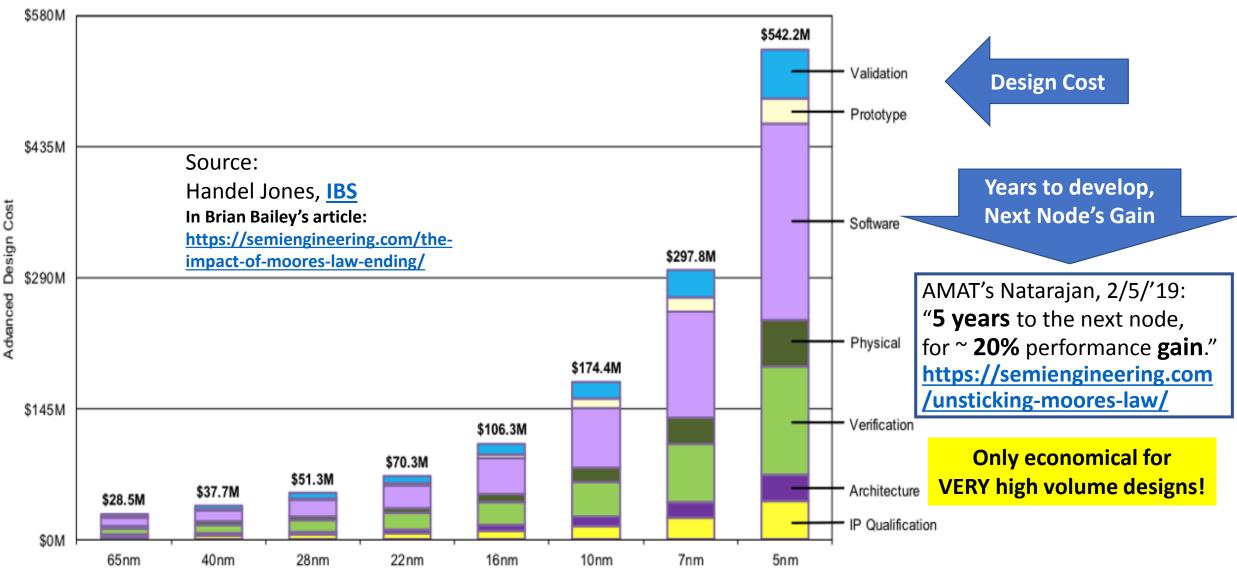

### Following Moore's Law Costs Time and Money

eda2asic

eda2asic

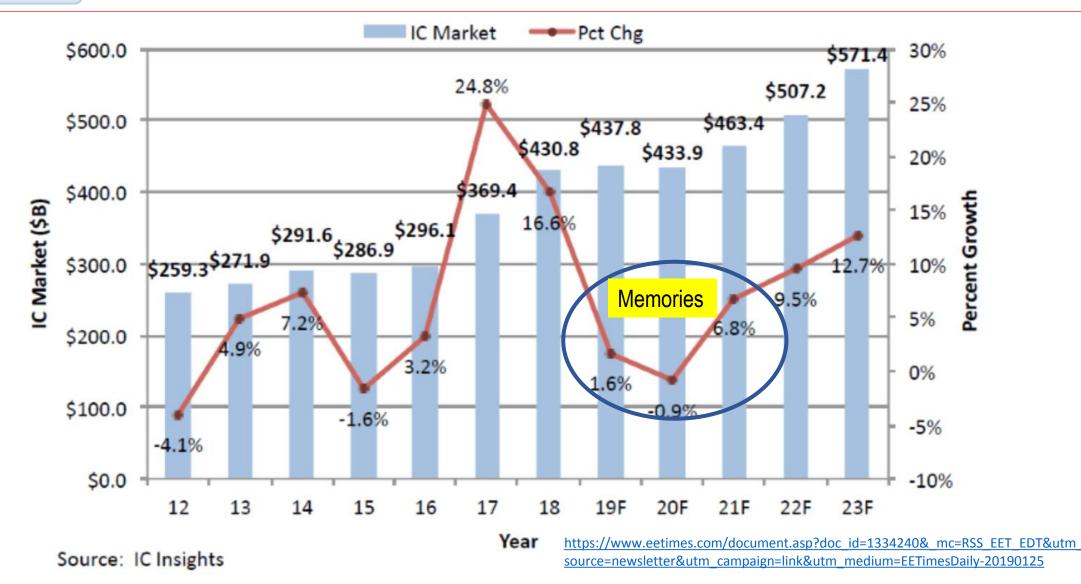

### **IC Market Growth Rates**

### **Gartner's Revenue Growth Forecast Through 2022**

(Presented by Bob Johnson at ISS2019, updated Q4, 2018)

eda2asic

9

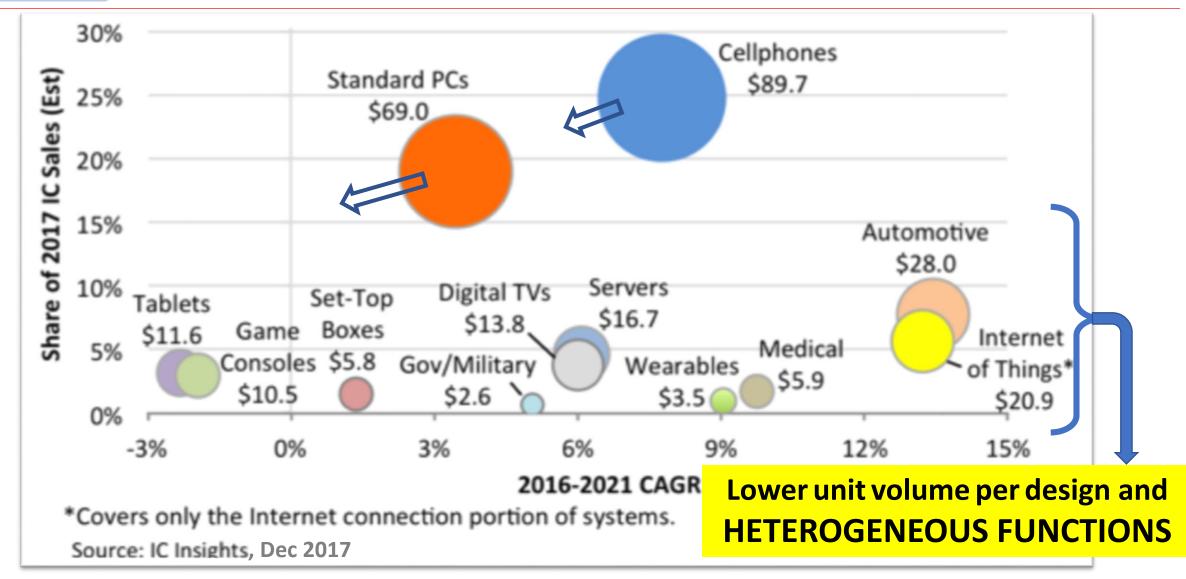

### IC End-Use Markets (\$B) and Growth Rates

eda2asic

http://www.icinsights.com/news/bulletins/Automotive-And-IoT-Will-Drive-IC-Growth-Through-2021/

10

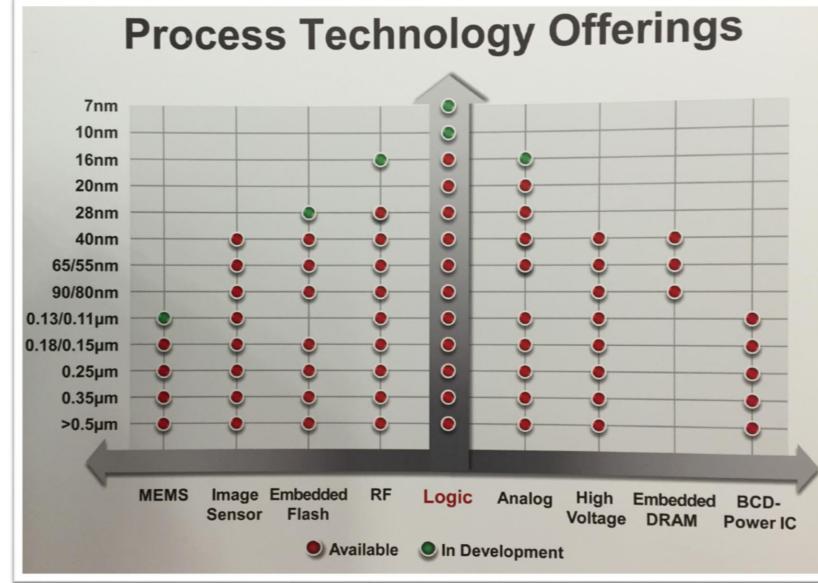

### **Availability of Heterogeneous Functions**

B

SoC Process extensions for HETEROGENEOUS integration are always 2, 3 or more nodes behind Digital Logic !

Source: TSMC Booth at DAC 53 in Austin, June 2016

#### --- China ----

#### Source: The Economist, Dec 1, 2018 This headline article is at: <u>https://www.economist.com/leaders/2018/12/01/</u> <u>chip-wars-china-america-and-silicon-supremacy</u>

This article looks at history, outlines our current challenges with China and suggests:

- Work with allies to push back on unfair practices

- Foster domestic innovation

- Prepare for a world with pervasive and powerful Chinese chips

### The Economist

Naval gazing-Russia eyeballs Ukraine Edit genes, but not like this Technology Quarterly: Zero carbon Our books of the year

Chip wars America, China and silicon supremacy

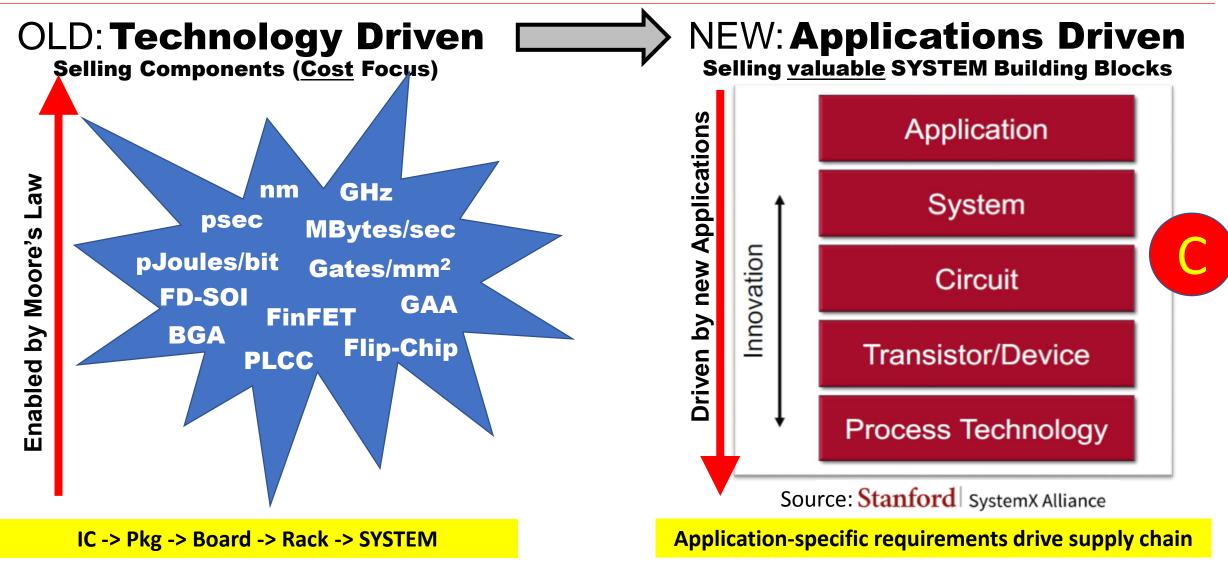

### **Customers Demand System-level Solutions**

## Market Requirements are Changing Significantly

| CRITERIA                  | Traditional, technology driven     | New, applications driven               |

|---------------------------|------------------------------------|----------------------------------------|

| Revenue Drivers           | Few: PCs, Laptops, Smartphones     | Many, Diverse: IoT, 5G, AI, Auto, FHE, |

| Updating Flexibility      | Only Software Updates practical    | System Upgrades → H/W Updates Too      |

| Typical Life-time Volume  | 100,000s to Many Millions          | 100s to 100,000s, Rarely More          |

| Functionality             | Primarily Logic and RAM            | Logic, RAM, NVM, RF, MEMS, Sensors     |

| Formfactor / Power Diss.  | Small / Low                        | Smaller / Very Low, Energy Harvesting  |

| NRE / Time / Manpower     | ~500,000,000 / 1-3 Yrs / 200+ Eng. | < Million / Months / 5-10 people       |

| Unit Cost Sensitivity     | VERY HIGH, <b>Cost</b> -driven     | MUCH LOWER, Value-driven               |

| Standards Support         | Established Worldwide              | Emerging, Regional, Appl. Specific     |

| Ecosystem/User Experience | Mature / Well Trained Users        | Emerging / Education Needed            |

#### eda2asic

### 100 Million "Computers on Wheels" by ~2030 ...

**FEBRUARY 6, 2019**

#### Digital Functions Heterogeneous Functions PACKAGING ALTERNATIVES

**Opportunities for :**

- Logic

- Memory

- Misc sensors

- Actuators

- ADCs / DACs

- **Displays & drivers**

- Several radios

- LEDs & drivers

- Power electronics

- OFF-THE SHELF AND CUSTOM IC PACKAGES

https://www.machinedesign.com/motioncontrol/could-5g-be-missing-puzzle-pieceself-driving-cars?NL=MACD-001&Issue=MACD-001 20190206 MACD-

001&Issue=MACD-001\_20190206\_MACD-001\_515&sfvc4enews=42&cl=article\_1\_b &utm\_rid=CPG05000000219930&utm\_ca mpaign=23153&utm\_medium=email&elq 2=37acfbd8bf8a410d971c464e65b3b678

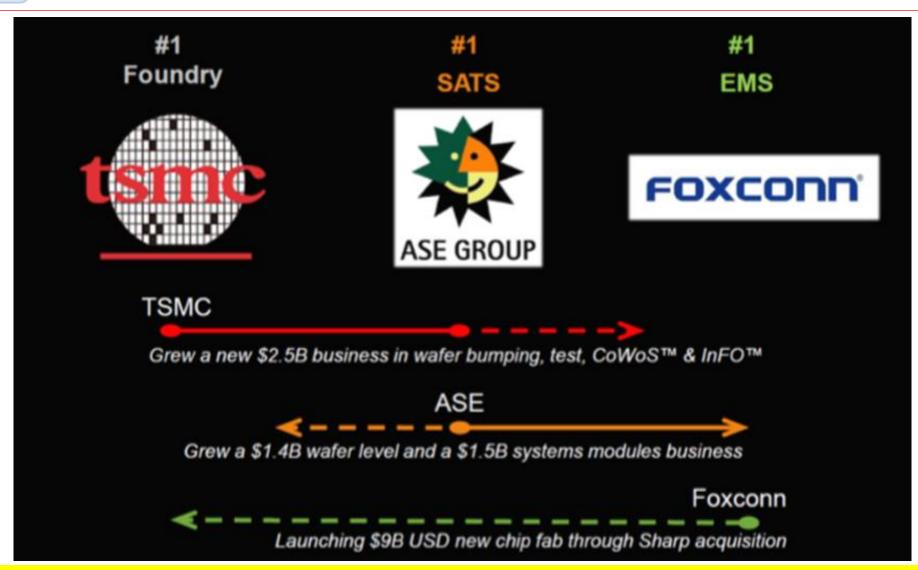

### **Examples for "Re-Integration" Towards IDMs**

eda2asic

**Traditional silos re-integrate. Examples from industry.** (Presented by Tim Olson, DECA Technologies) at ISS2019 **16**

### Introduction

### **Key Market Data and Requirements**

### **Multi-die ICs and Advanced Packaging**

### EDA Tools, Flows and Libraries

### Summary

#### The 3D-IC Dream ~10 Years Ago

## Lower System COST

Smaller FORM-FACTOR

## Higher PERFORMANCE per WATT

# **BUT:** PI & HEAT MANAGEMENT

#### eda2asic

### **System-level Solutions in a Package**

SOURCE: Electronic Design Article, Part 1, Sept 2018 "Path to Systems: Opportunities and Challenges for Next-Gen Semiconductor Integration"

https://www.electronicdesign.com/embedded-revolution/path-systemsopportunities-and-challenges-next-gen-semiconductor-integration

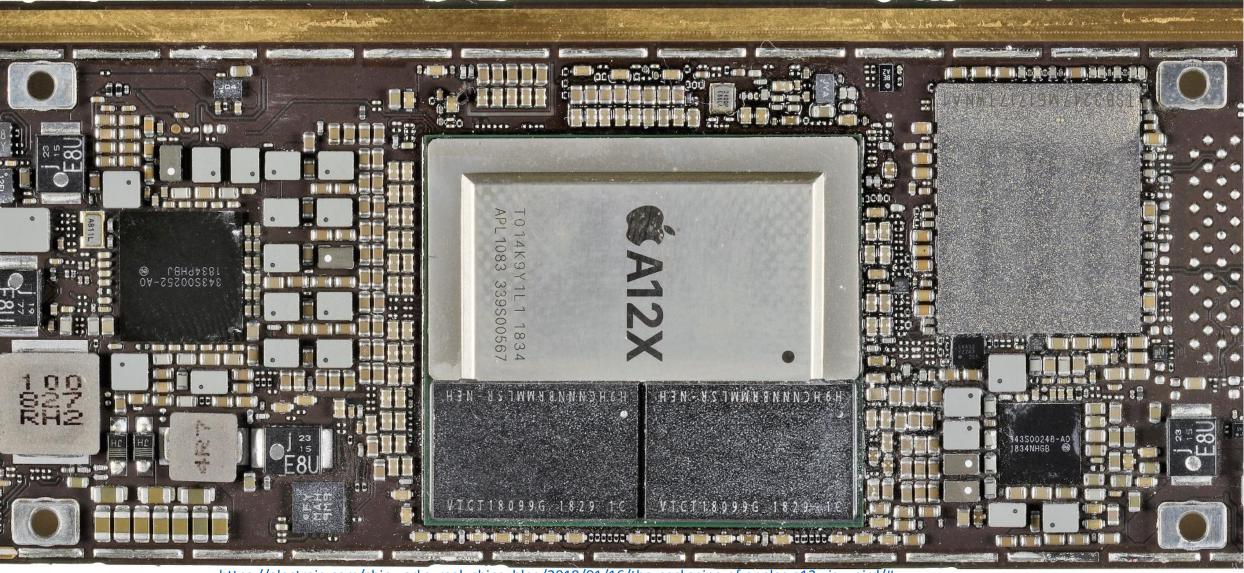

Second generation of TSMC's Integrated Fan Out (InFO) Packaging for the Apple A11 processor for the iPhone X SOURCE: YOLE Newsletter, February 2018

Value creation moves from single-die ICs to multi-die advanced packages !!! WHY? Heterogeneous Functions, NRE, Unit Cost, Performance/Watt, Form-factor, Reliability,...

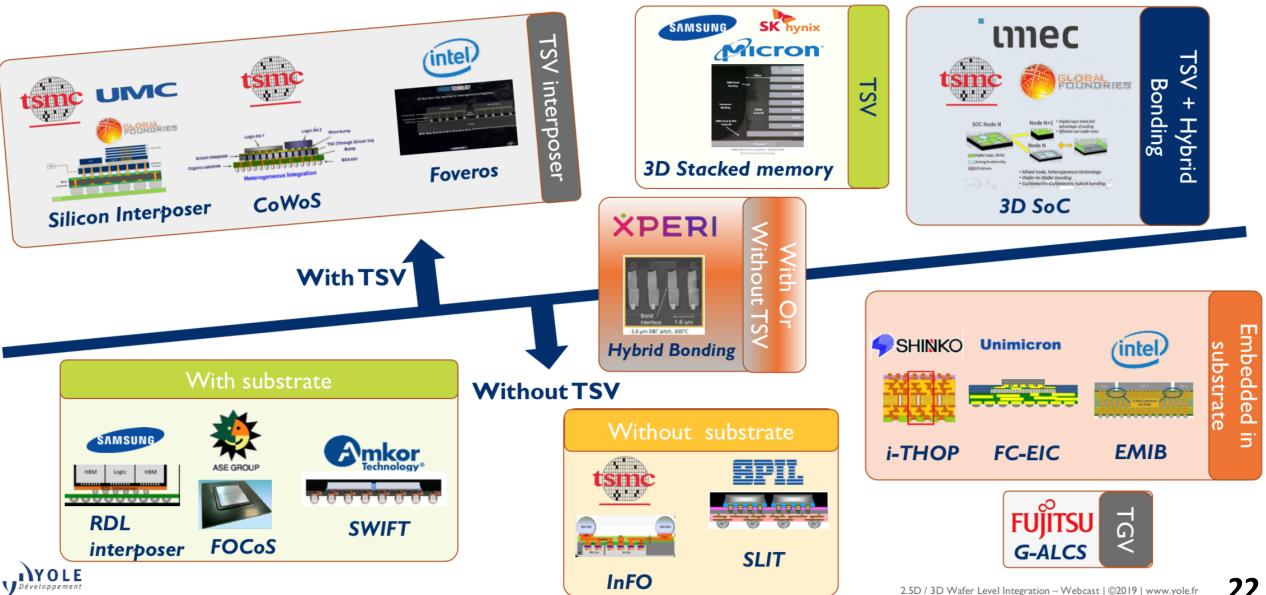

### 2D-SoCs

- "That's how we always designed ICs", BUT

- NRE's are exploding

- Time to Market => Years

- Mixing heterogeneous functions extremely costly

- Bug fixes very expensive

- Reliability @ < 7nm

- IP availability & cost

- Sole source Si supply

- Customization difficult

- Design reuse difficult

### **2.5D-ICs**

- Lower total power

- Enables modularity

- Mostly: Logic & HBM, BUT

- Si Interposer: \$\$, <20 cm<sup>2</sup>

- Thin die warpage, stress

- Organic I/Po → larger L/S

- Glass I/Po still not mature

- TSVs processing & area: \$\$

- Thermal management

- Interaction between dies

- Power and Signal Integrity

## **3D-ICs**

- Lowest total power

- Unlimited B/W, BUT:

- Primary use memories

- Thermal management

- Interaction between dies

- W-2-W → same die size

- Testability, redundancy

- Yield management

- Vertical bus standards

- NO planning, design & verification tools yet

- Monolithic 3D for logic ?

Also: Design and Manufacturing of Wafer and Panel-level single and multi-die packaging is rapidly maturing! Announced WLP/PLP platforms: TSMC's InFO // Samsung's ePLP // Nepes' RCP // Shinko's MCeP 20

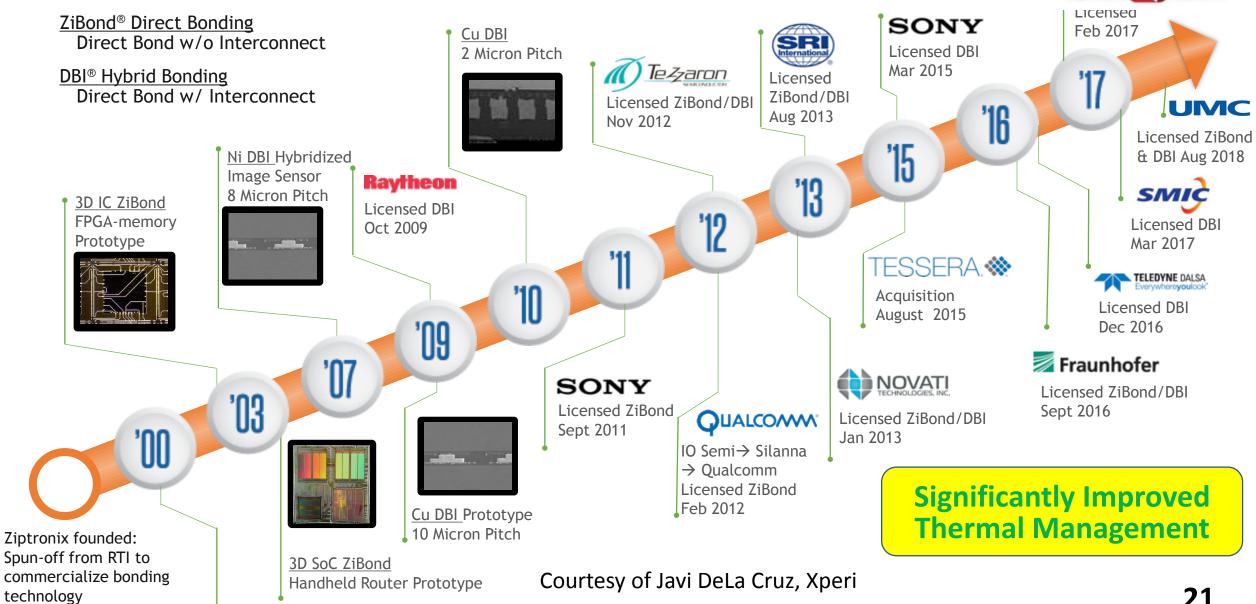

### **Two Decades of Direct Bonding Proliferation**

Omni sion.

#### Wide Range of 2.5/3D-IC Applications Using Hybrid Bonding

22

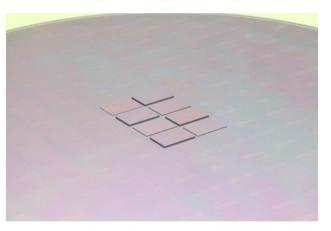

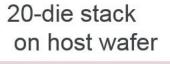

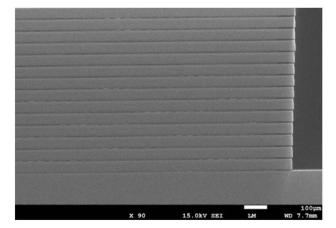

### DBI® Die-to-Wafer Readiness

- Some devices do not lend themselves well to wafer-to-wafer bonding

- Throughput 10x faster than TCB

- Only viable way to achieve 16-high HBM3 stacks with height restriction

- Production ready process available for tech-transfer

2-die, 3-die and 4-die Stacks on host wafer

Cross-section of 20-die stack

**XPERI**

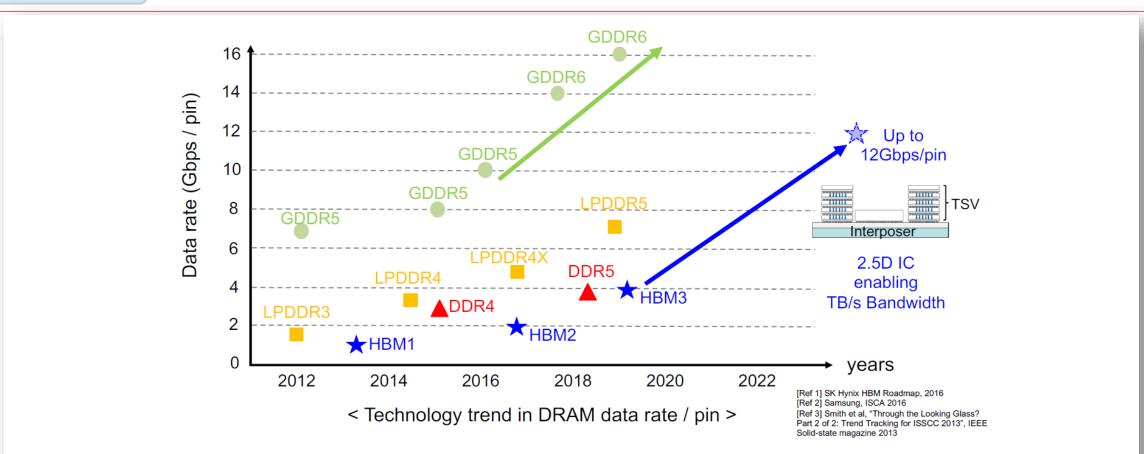

### **Data Rate Trends in Gbps per Pin**

eda2asic

ERA

- Data rate of high-speed channel in DRAM is continuously increasing for higher bandwidth

- Maintaining signal integrity in the high-speed channel is crucial for higher data bandwidth

#### KAIST

TeraByte Interconnection and Package Laboratory

Source: Youngwoo Kim, Post-Doc at KAIST's Terabyte Labs. Presented at DesignCon 2019

#### Apple's iPAD Pro with A12X Applications Processor Passives, Passives, Passives and a few ICs

https://electroiq.com/chipworks\_real\_chips\_blog/2019/01/16/the-packaging-of-apples-a12x-is-weird/#

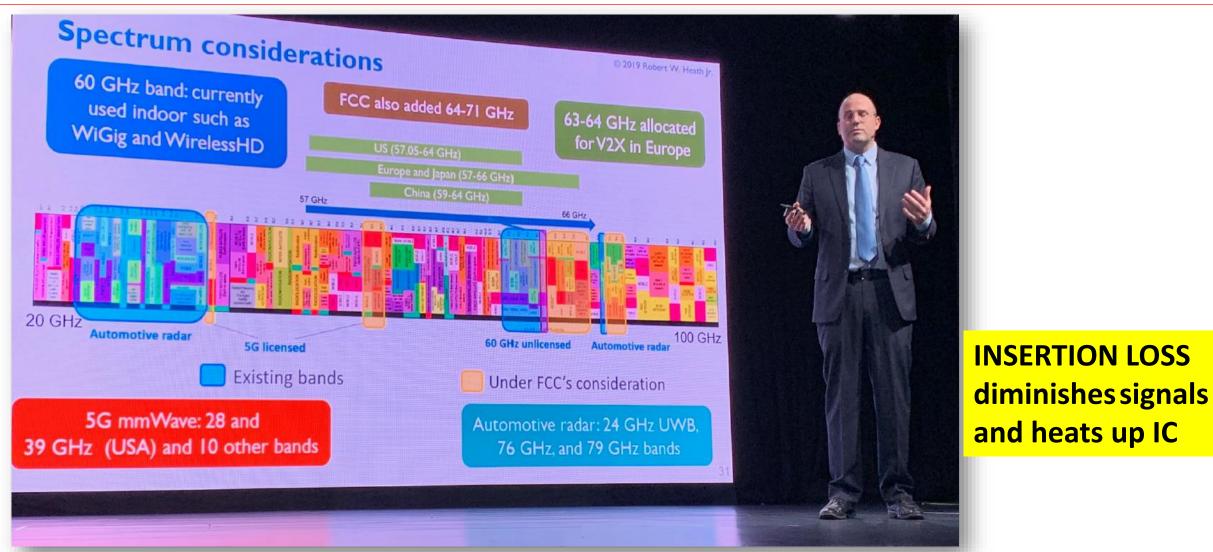

## eda2asic 5G, Lidar,... Need High Frequency IC Packaging Materials

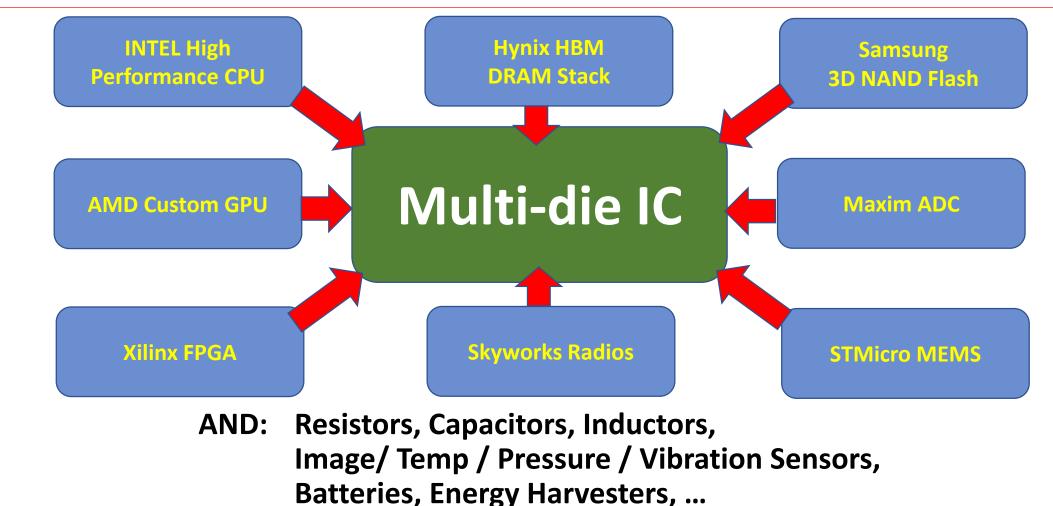

### Heterogeneous Integration of CHIPLETs ("LEGO Blocks")

eda2asic

Assembly & Test Houses have an inherent advantage (vs Fabs) when a mix of dies from multiple foundries is needed!

### Introduction

### **Key Market Data and Requirements**

### Multi-die ICs and Advanced Packaging

**EDA Tools, Flows and Libraries**

**Summary**

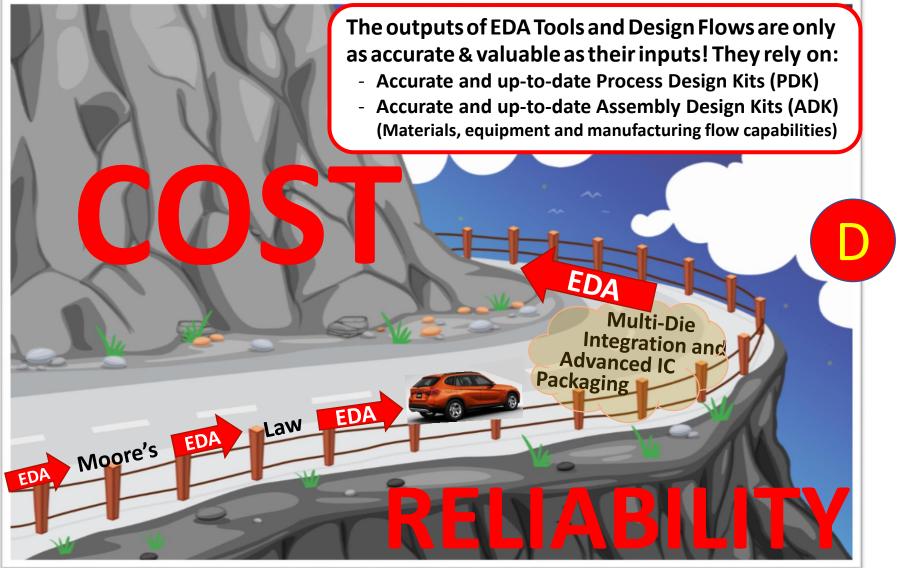

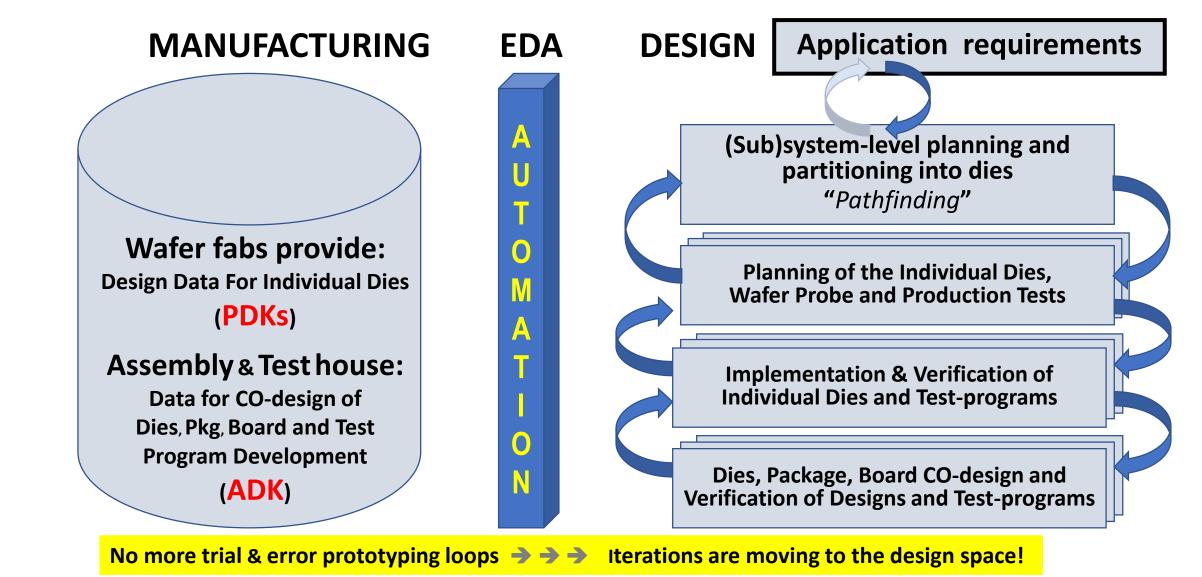

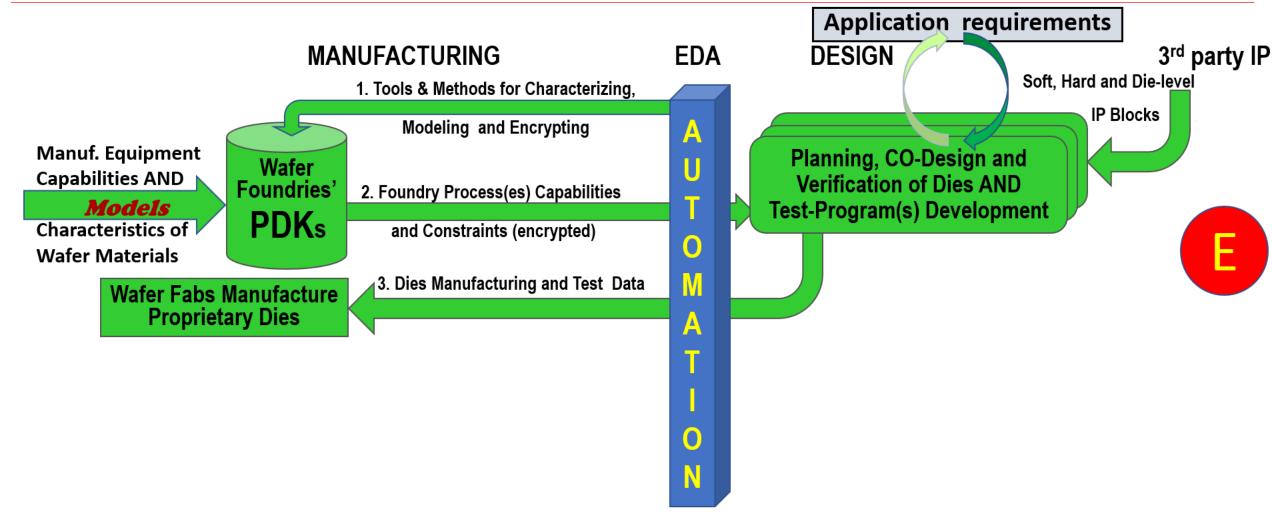

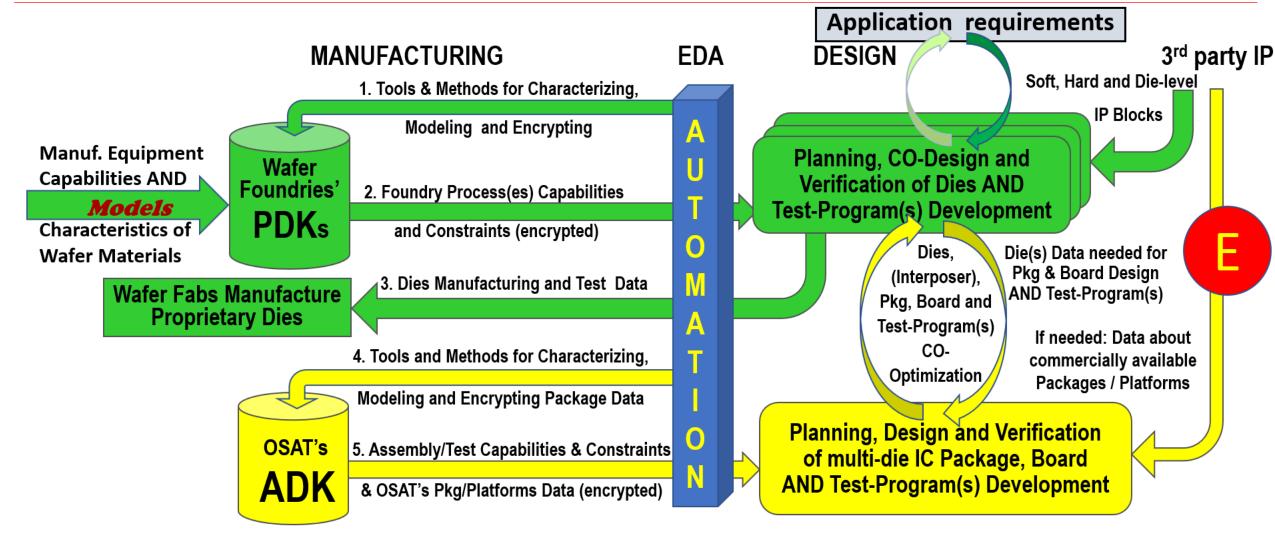

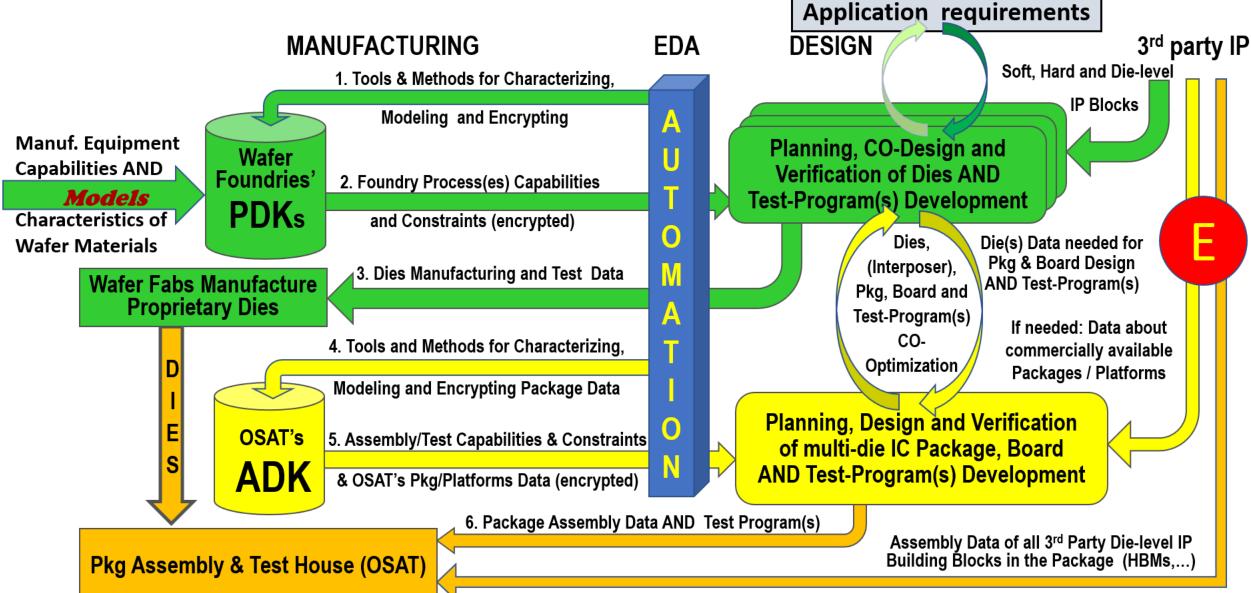

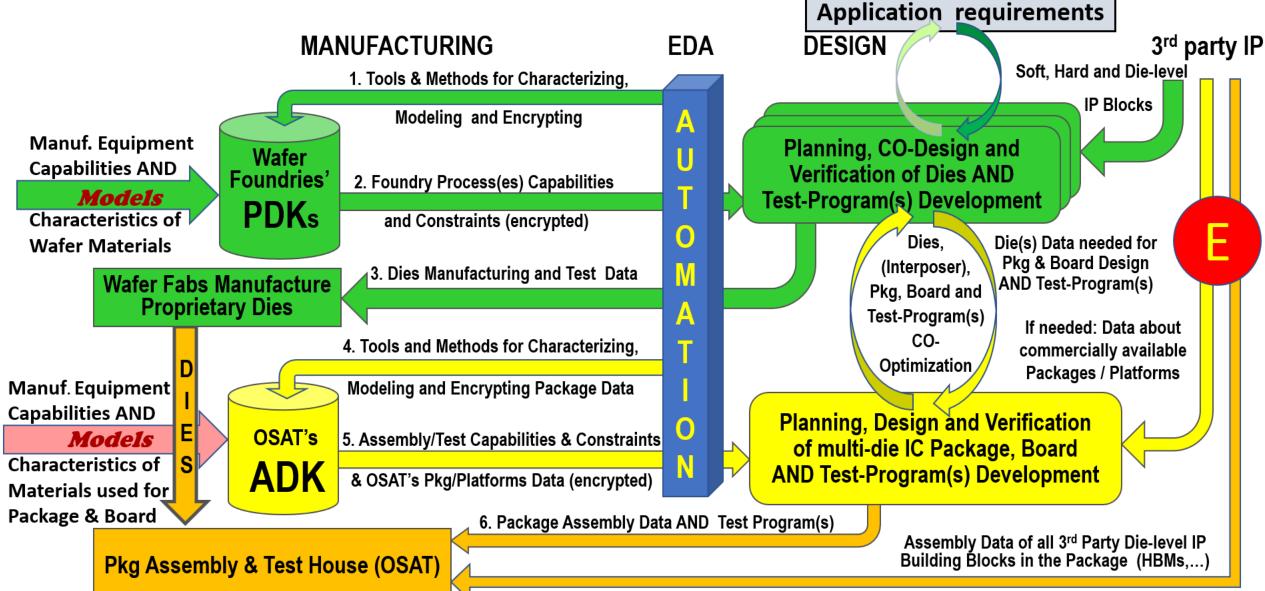

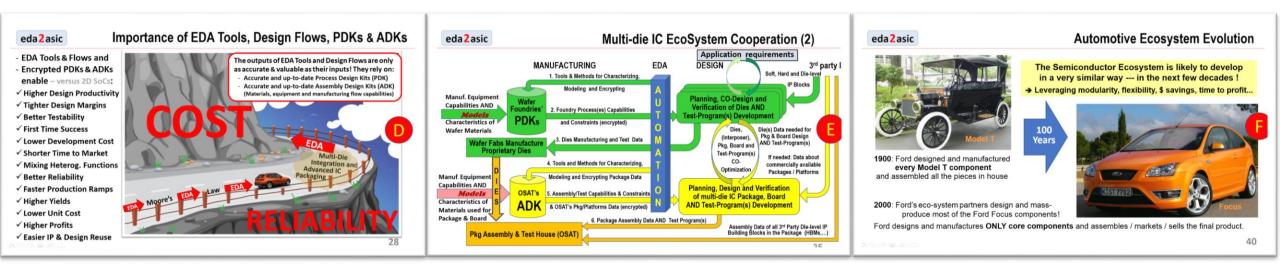

## Importance of EDA Tools, Design Flows, PDKs & ADKs

- EDA Tools & Flows and

Encrypted PDKs & ADKs enable – versus 2D SoCs:

✓ Higher Design Productivity

- ✓ Tighter Design Margins

- ✓ Better Testability

eda2asic

- ✓ First Time Success

- ✓ Lower Development Cost

- $\checkmark$  Shorter Time to Market

- ✓ Better Reliability

- ✓ Faster Production Ramps

- $\checkmark$  Higher Production Yields

- ✓ Lower Unit Cost

- ✓ Higher Profits

- ✓ Easier IP & Design Reuse

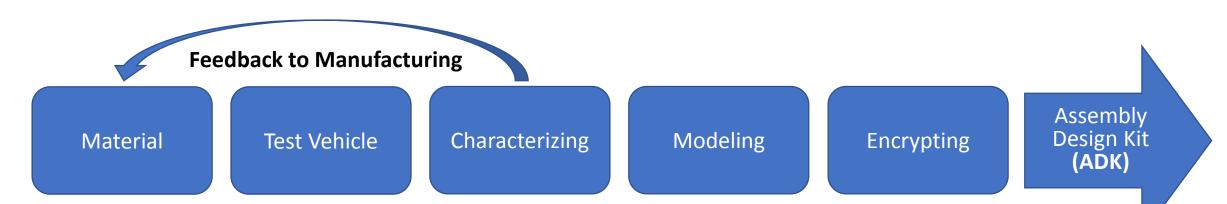

### Characterization of IC Packaging Materials for ADK\*

Interposer **RDL**, Vias, Power Planes Underfill Bond wires Micro balls, C4 balls Copper studs Pkg Substrate **RDL**, Vias, Power Planes Molding Compound UBM Heatsink, PCB, etc...

Develop suitable test structure(s) & methodologies to capture all relevant material characteristics for rigid and flex

Capture relevant characteristics, e.g.

- Operating temp range

- Aging mechanisms

- Thermal conductivity

- Expansion coefficient

- Young's modulus

- Poisson ratio

- Dielectric loss

- Behavior if stretched, compressed, bent, twisted, warped,...

- Chemical resistivity

Describe all these with equations, graphs, tables, ... Get accurate and up-to-date inputs for EDA tools

Encrypt generated data, materials behavior so that only authorized EDA tools can interpret suppliers' proprietary information. Convey all material capabilities and constraints to the IC & package designers for planning, design and exhaustive verification.

#### **ACCURATE** materials characterization and modeling -> ACCURATE simulation results

\*ADK = Package **Assembly Design Kit**

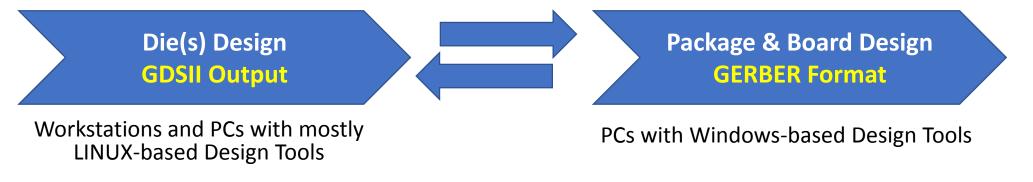

### EDA and Packaging experts develop jointly – with customer(s) inputs:

- Die Package Board bi-directional Reference Design Flow:

- Recommends tools for design planning, implementation and verification steps for multi-die ICs

- Describes hand-of criteria from designers to manufacturing partner's assembly and test team

- Outlines logistics and inputs needed for wafer-probe, interim and final test

- Suggests how and who to cooperate with in EDA as well as at the assembly and test partner(s)

- Lists additional info sources: Web-pointers, industry standards, white papers, books, ...

- Describes best practices for data exchange between die(s) and package; encourages CO-design

Maturity of design & manufacturing steps influences when to automate which design step(s) !

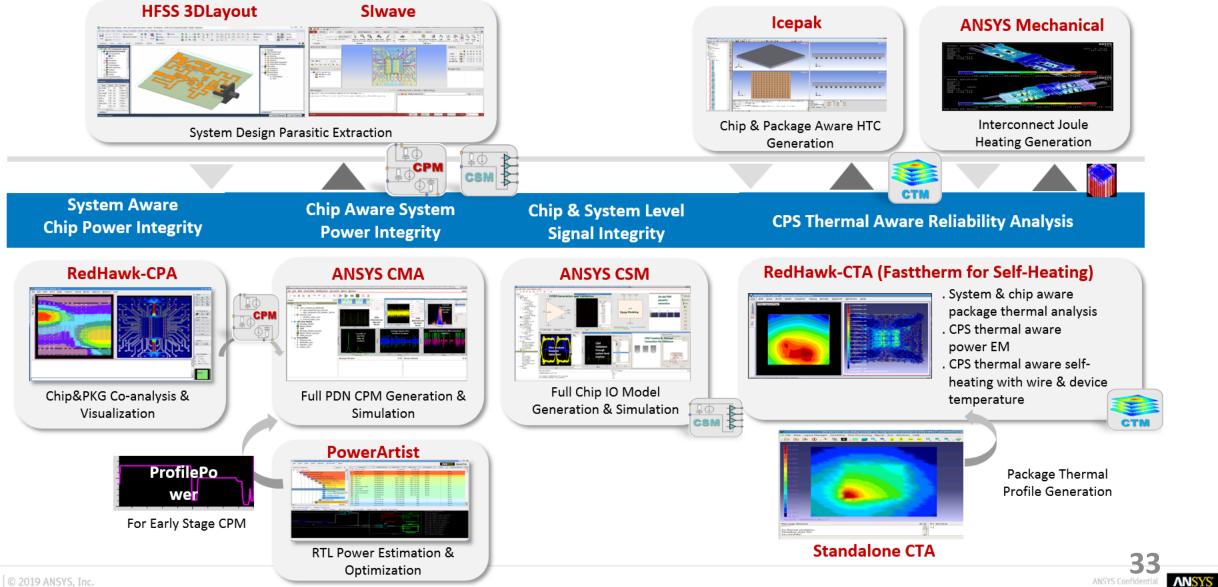

#### **ANSYS Chip Package System Eco System for Power/Thermal/Signal Integrity** : Reproducing Silicon/System Validation Environment

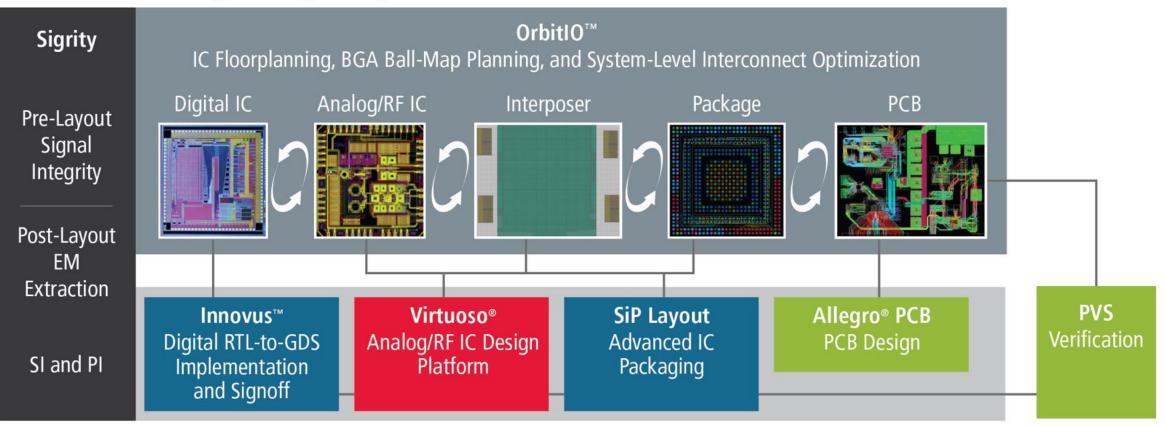

#### IC/Interposer/Package/PCB Cross-Domain Solution System Planning

#### Assembly, Planning, and Optimization Level

**Implementation Level**

Courtesy of Bill Acito and John Park, Cadence Design Systems

https://www.3dincites.com/2018/11/eda-design-tools-flows-targeting-wlp-featured-at-iwlpc-2018/

34

cādence

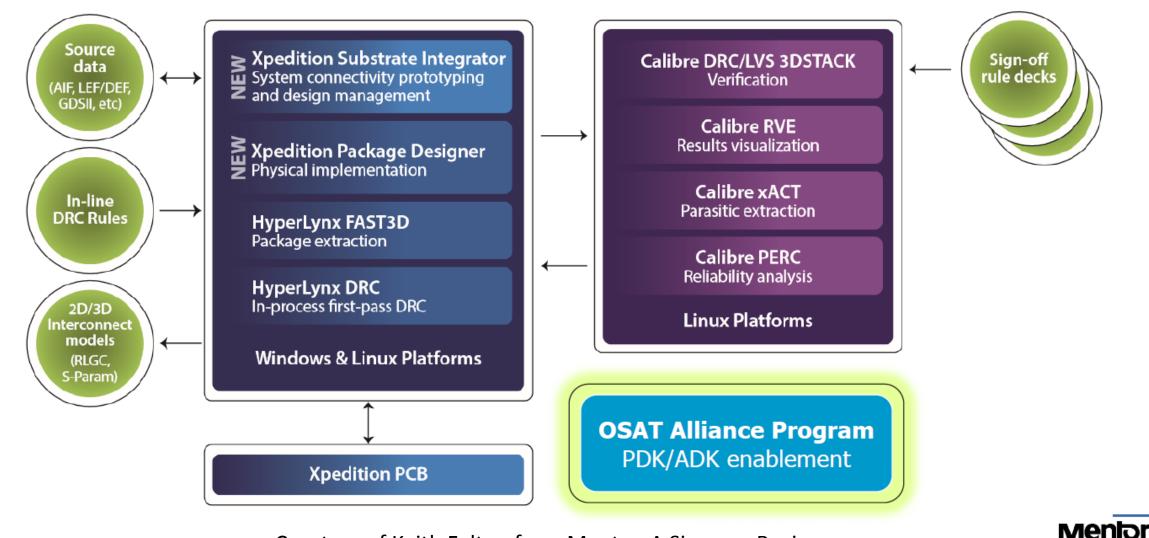

### Mentor current design flow for Advanced Packaging

Courtesy of Keith Felton from Mentor, A Siemens Business https://www.3dincites.com/2018/11/eda-design-tools-flows-targeting-wlp-featured-at-iwlpc-2018/

35

### OSATs need to expand relationships with multiple

- CMOS, GaAs, SiGe, SiC, InP, GaN, SOI,... advanced and traditional wafer foundries

- CHIPLET sources to integrate die-level IP building blocks into multi-die ICs

- MEMS and Sensors suppliers as well as wafer-probe & test experts

- Interposer suppliers (silicon, organic, high-res Si) and low-cost litho for substrate

- Miniature passives (RLC) suppliers and Flexible Hybrid Electronics (FHE) partners

- EDA vendors to

- model and encrypt your materials and equipment capabilities for ADK

- develop reference design flows for your off-the-shelf platforms

- improve IC test programs, self-test capability, built-in redundancy

- utilize Software as a Service (SaaS) business model = rent EDA tools by the minute

### eda2asic Flexible Hybrid Electronics (FHE) and Medical Wearables

### Introduction

### **Key Market Data and Requirements**

### Multi-die ICs and Advanced Packaging

### EDA Tools, Flows and Libraries

**Summary**

- 50+ years of following Moore's Law has reached many economical and technical limits

- % growth and margins of smartphones are declining -> no longer innovation drivers

- Lower volume, customer specific solutions offer higher value and better profit margins

- Closer and structured supply chain cooperation is needed to meet customer requirements

- Designers, Wafer-fabs, Assembly & Test Houses (OSATs) need to become equal partners

- Multi-die ICs offer modularity, enable heterogeneous integration, lower NRE & risk

- Multi-die ICs increase Performance/Watt, but power density & thermal challenges increase

- Study system requirements; leverage your core competence; offer unique solutions

It's not the strongest of the species that survives, nor the most intelligent. It is the one that is most adaptable to change. Charles Darwin

### **Automotive Ecosystem Evolution**

~1900: Ford designed and manufactured every Model T component and assembled all the pieces in house

~2000: Ford's eco-system partners design and massproduce most of the Ford Focus components!

The Semiconductor Ecosystem is likely to develop in a very similar way --- in the next few decades ! → Leveraging modularity, flexibility, \$ savings, time to profit...

Technology AND Business Model = SUCCESS

HETEROGENEOUS Functions -> Multi-die IC

#### **APPLICATIONs** drive the requirements

Walk the fine line between COST & REL with EDA

It's COMPLICATED

#### Nobody spends an annual salary on a car any more

#### **BEFORE deciding your 2019 strategy, please click here and read:**

- Brian Bailey's "Chip Dis-Integration" at <u>https://semiengineering.com/chip-dis-integration/</u>

- Ed Sperling's "Advanced Packaging Confusion" at <u>https://semiengineering.com/advanced-packaging-confusion/</u>

- Mark LaPedus' "Extending the IC Roadmap" with An Steegen's comments at <u>https://semiengineering.com/extending-the-ic-roadmap/</u>

- Brian Bailey's "Design for Advanced Packaging" at https://semiengineering.com/design-for-advanced-packaging/

- Herb Reiter's "The Great Divide Between Semiconductor Design and Manufacturing" <u>https://www.3dincites.com/2016/08/the-great-divide-between-semiconductor-design-and-manufacturing/</u>